近些年,日益增多的高頻信號設計與穩步增加的電子系統性能緊密相連。隨著系統性能的提高,PCB設計師的挑戰與日俱增:更微小的晶粒,更密集的電路板布局,更低功耗的芯片要求。隨著所有技術的迅猛發展,我們已成為高速設計的核心,需要考慮其復雜性和所有因素。

回顧

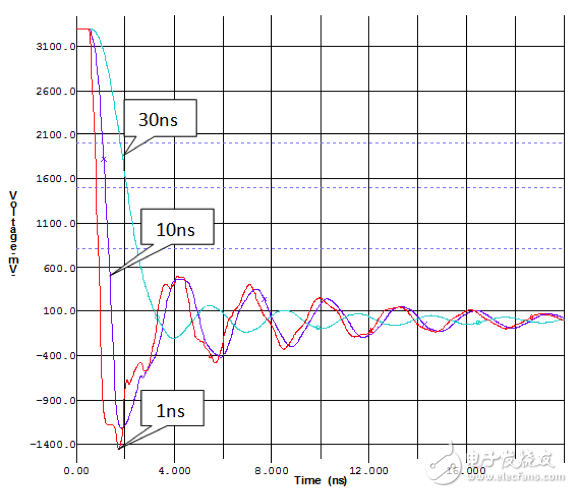

在過去30年,PCB設計發生了很大變化。 1987年,我們認為0.5微米是技術的終結者,但今天,22納米工藝已變成了常態。如下圖所示,1985年的邊緣速率推進了設計復雜性的提升(通常為30納秒),而如今邊緣速率已變成1納秒。

過去30年邊緣速率的變化

技術進步中伴隨各種問題

技術的進步總是伴隨著一系列問題。隨著系統性能的提升和高速設計的采納,一些問題必須在設計環境中進行處理。下面,我們來總結一下面臨的挑戰:

信號質量

IC制造商傾向于更低的核心電壓和更高的工作頻率,這就導致了急劇上升的邊緣速率。無端接設計中的邊緣速率將會引發反射和信號質量問題。

串擾

在高速信號設計中,密集路徑往往會導致串擾——在PCB上,走線間的電磁耦合關聯現象。

串擾可以是同一層上走線的邊緣耦合,也可以是相鄰層上的寬邊耦合。耦合是三維的。與并排走線路徑相比,平行路徑和寬邊走線會造成更多串擾。

寬邊耦合(頂部)相比于邊緣耦合(底部)

輻射

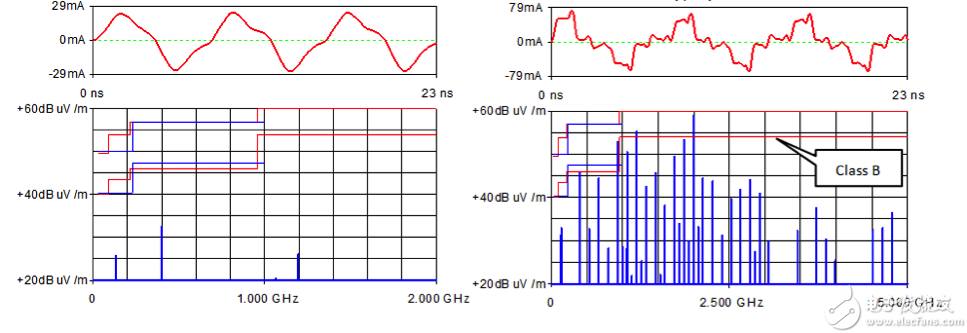

在傳統設計中的快速邊緣速率,即使使用與先前相同的頻率和走線長度,也會在無端接傳輸線上產生振鈴。這從根本上導致了更高的輻射,遠遠超過了無終端傳輸線路的FCC/CISPR B類限制。

10納秒(左)和1納秒(右)的邊緣速率輻射

設計解決方案

信號和電源完整性問題會間歇出現,很難進行判別。所以最好的方法,就是在設計過程中找到問題根源,將之清除,而不是在后期階段試圖解決,延誤生產。通過疊層規劃工具,能更容易地在您的設計中,實現信號完整性問題的解決方案。

電路板疊層規劃

高速設計的頭等大事一定是電路板疊層。基板是裝配中最重要的組成部分,其規格必須精心策劃,避免不連續的阻抗、信號耦合和過量的電磁輻射。在查看您下次設計的電路板疊層時,請牢記以下提示和建議:

-

所有信號層需相鄰并緊密耦合至不間斷的參考平面,該平面可以創建一個明確的回路,消除寬邊串擾。

每個信號層的基板都鄰接至參考平面

-

有良好的平面電容來減少高頻中的交流阻抗。緊密耦合的內電層平面來減小頂層的交流阻抗,極大程度減少電磁輻射。

-

降低電介質高度會大大減少串擾現象,而不會對電路板的可用空間產生影響。

布線和工作流程

精心策劃疊層后,下一步便需關注電路板布線。基于設計規則和工作區域的精心配置,您能夠最高效成功地對電路板進行布線。以下這些提示,能幫助您的布線更加容易,避免不必要的串擾、輻射和信號質量問題:

-

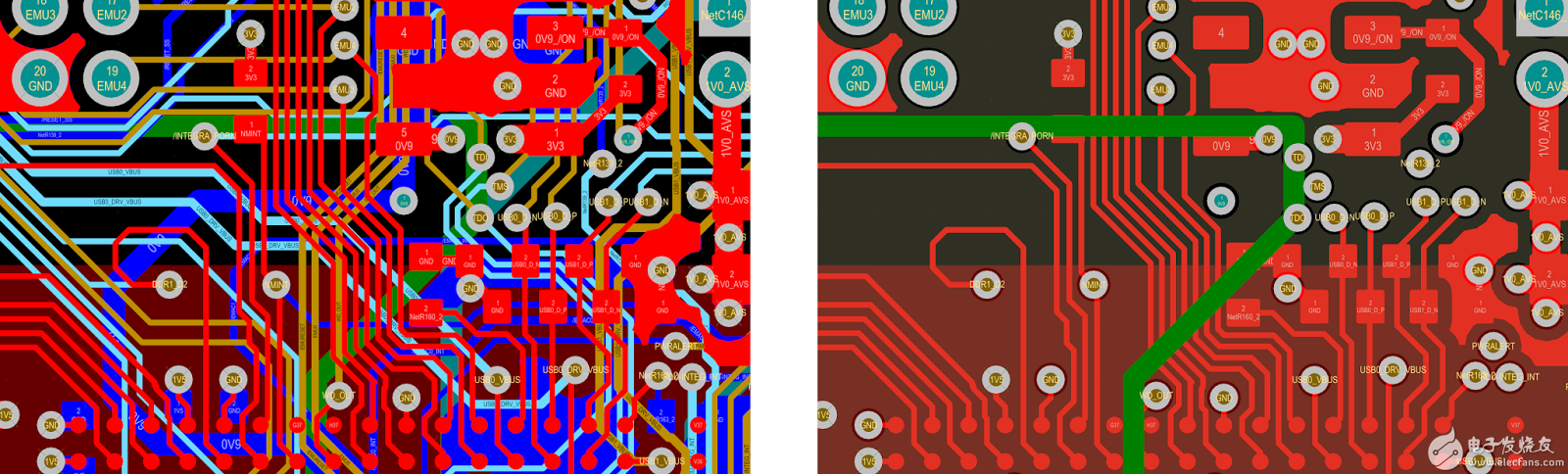

簡化視圖,以便清楚查看分割平面和電流回路。為此,首先確定哪個銅箔平面(地或電源)作為每個信號層的參考平面,然后打開信號層和內電層平面同時查看。這能幫助您更容易地看到分割平面的走線。

多重信號層(左)、頂層和相鄰平面視圖(右)

-

如果數字信號必須穿越電源參考平面,您可以靠近信號放置一或兩個去耦電容(100nF)。這樣,就在兩個電源之間提供了一個電流回路。

-

避免平行布線和寬邊布線,這會比并排布線導致更多串擾。

-

除非使用的是同步總線,否則,平行區間越短越好,以減少串擾。為信號組留出空間,使其地址和數據間隔是走線寬度的三倍。

-

在電路板的頂層和底層使用組合微帶層時要小心。這可能導致相鄰板層間走線的串擾,危及信號完整性。

-

按信號組的最長延遲為時鐘(或選通)信號走線,這保證了在時鐘讀取前,數據已經建立。

信號清晰度

在未來,電子設計的復雜性毫無疑問會持續增加,這會給PCB設計師帶來一系列亟待解決的挑戰。確保電路板疊層、阻抗、電流回路的正確配置,是設計穩定性的基礎。Altium Designer高速設計的最新功能,例如xSignals,通過2D場解算器驗證,可以實現關鍵信號更加精確的匹配。

您是否使用了疊層規劃助手,來管理日益復雜的高信號速度設計?如果沒有,請查看ICD Stackup Planner,這是Altium Designer的一個應用擴展。

-

pcb

+關注

關注

4319文章

23099瀏覽量

397891 -

高性能

+關注

關注

0文章

157瀏覽量

20399 -

Altium Designer

+關注

關注

48文章

394瀏覽量

44701

發布評論請先 登錄

相關推薦

圣誕特輯 |開源芯片系列講座第25期:RISC-V架構在高性能領域的進展與挑戰

直播預約 |開源芯片系列講座第25期:RISC-V架構在高性能領域的進展與挑戰

電子設計競賽準備經歷分享

探秘PCB羅杰斯板材:電子領域的高端之選

探尋玻璃基板在半導體封裝中的獨特魅力

在電子設計領域,高性能設計有其獨特挑戰

在電子設計領域,高性能設計有其獨特挑戰

評論