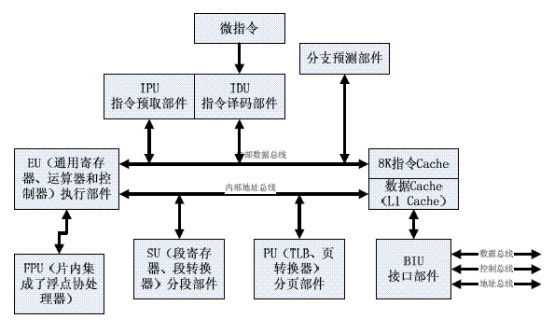

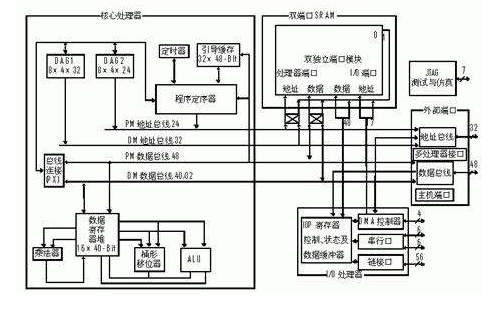

這里我們主要介紹Intel 80x86系列CPU保護(hù)模式下最核心的部件中幾個(gè)寄存器的作用,這些寄存器在Linux內(nèi)核運(yùn)行時(shí)起著至關(guān)重要的作用。至于其他那些各式各樣的硬件設(shè)備,我們?cè)谥v解設(shè)備驅(qū)動(dòng)時(shí)會(huì)針對(duì)具體的驅(qū)動(dòng)程序來(lái)介紹的。首先,大家先看看CPU的主要架構(gòu):

EU(通用寄存器、運(yùn)算器和控制器)執(zhí)行部件:完成指令所要求的功能。

SU(段寄存器、段轉(zhuǎn)換器)分段部件:完成執(zhí)行單元的地址請(qǐng)求, 將虛地址轉(zhuǎn)換為線性地址。

PU(TLB、頁(yè)轉(zhuǎn)換器)分頁(yè)部件:將線性地址轉(zhuǎn)換為物理地址。

BIU(總線接口)接口部件:完成指令預(yù)取請(qǐng)求和執(zhí)行單元的數(shù)據(jù)存取請(qǐng)求,數(shù)據(jù)存取請(qǐng)求優(yōu)先于指令預(yù)取請(qǐng)求。

IPU(控制邏輯和預(yù)取隊(duì)列)預(yù)取部件:16字節(jié)指令預(yù)取隊(duì)列, 提出預(yù)取請(qǐng)求。

IDU(指令譯碼、6字節(jié)指令隊(duì)列)譯碼部件:完成指令譯碼功能。

FPU(片內(nèi)集成了浮點(diǎn)協(xié)處理器):專用于浮點(diǎn)運(yùn)算的處理部件。

下面,我們針對(duì)EU、SU和PU模塊做做詳細(xì)說(shuō)明,其他模塊就暫時(shí)不介紹了。

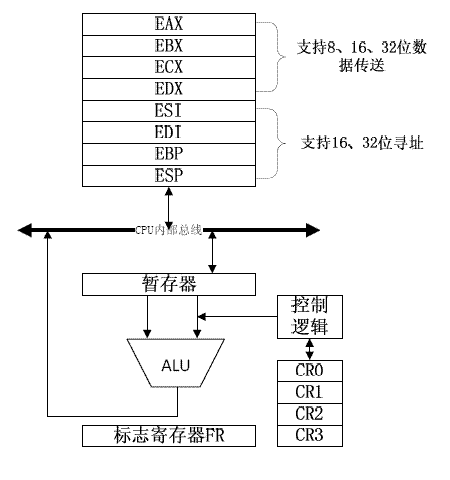

1 EU模塊

EU模塊是CPU中最核心,最重要的部件。現(xiàn)在的奔騰CPU已經(jīng)發(fā)展了若干年了,但其中最起作用的還是加法單元ALU,一組通用寄存器組、一個(gè)標(biāo)志和控制邏輯。如圖:

首先,8個(gè)32位通用寄存器按使用情況分為三種:指針寄存器、變址寄存器、數(shù)據(jù)寄存器。

[1] 指針寄存器:主要提供全部或部分偏移量

ESP:專門(mén)存放堆棧段中棧頂單元的偏移量。

EBP:存放堆棧段中某個(gè)單元的全部/部分偏移量,也可存放32位或16位操作數(shù)或運(yùn)算結(jié)果。

[2] 變址寄存器

ESI/EDI:存放主存操作數(shù)的全部/部分偏移量,也可存放16位操作數(shù)和結(jié)果,在多數(shù)情況功能可以互換。 但在串操作指令中作用不能互換,源操作數(shù)必須用ESI提供偏移量,目的操作數(shù)必須用EDI提供偏移量。

[3] 數(shù)據(jù)寄存器

◆ 數(shù)據(jù)寄存器既可以作為4個(gè)32位的寄存器,也可以作為8個(gè)16位的寄存器 ,還可以作為16個(gè)8位的寄存器。

◆ 在程序中,數(shù)據(jù)寄存器用來(lái)存放操作數(shù)、運(yùn)算結(jié)果或其他信息。

◆ 數(shù)據(jù)寄存器在許多指令中要求指明使用,但也有隱含或特定使用,詳細(xì)情況請(qǐng)查閱相關(guān)資料。

其次,4個(gè)控制寄存器CR0~CR3

[1] CR0:由80286的MSW寄存器演變而來(lái),并增加了2位,Linux最看重他的PG位——PG=0,允許分頁(yè);PG=1,不允許分頁(yè)。

[2] CR1:未使用

[3] CR2:頁(yè)故障地址寄存器, 存放出現(xiàn)故障的頁(yè)的32位線性地址

[4] CR3:頁(yè)目錄基地址寄存器, 存放頁(yè)目錄表的基地址。

最后來(lái)看看標(biāo)志寄存器FR

FR用來(lái)記錄程序執(zhí)行時(shí)的狀態(tài),即兩個(gè)操作數(shù)通過(guò)ALU后的狀態(tài):

[1] 進(jìn)位標(biāo)志位CF(Carry Flag)

[2] 奇偶標(biāo)志位PF(Parity Flag)

[3] 輔助進(jìn)位標(biāo)志位AF(Auxiliary Carry Flag)

[4] 零值標(biāo)志位ZF(Zero Flag)

[5] 符號(hào)標(biāo)志位SF(Sign Flag)

[6] 溢出標(biāo)志位OF(Overflow Flag)

[8] 中斷標(biāo)志位IF(Interrupt-enable Flag)

[9] 方向標(biāo)志位DF(Direction Flag)

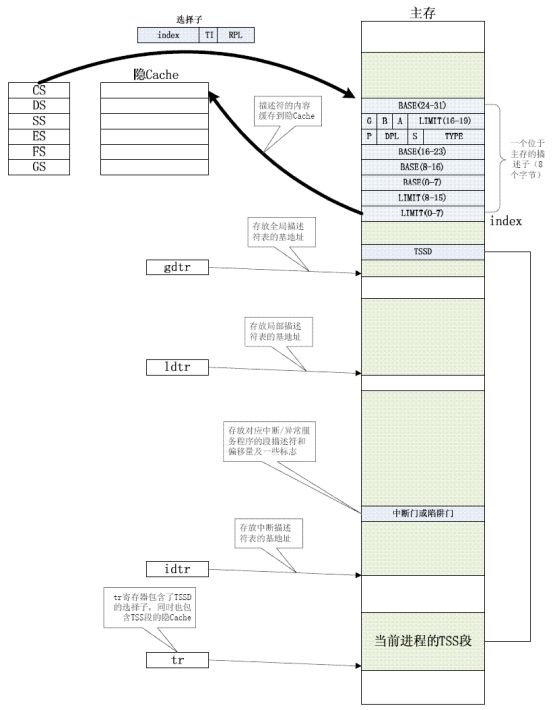

2 SU模塊

下面著重看看SU部件。這個(gè)部件也被Linux用到了,但Linux用它的目的并不是遵循Intel手冊(cè)對(duì)地址進(jìn)行虛擬化,而是利用它來(lái)做用戶態(tài)和內(nèi)核態(tài)的切換。而對(duì)地址的虛擬化,則是通過(guò)PU單元,也就是分頁(yè)機(jī)制來(lái)實(shí)現(xiàn)的。

首先來(lái)看看SU模塊的架構(gòu)圖:

處理器提供了6個(gè)段寄存器,段寄存器的唯一的目的是存放選擇子(16位)。這些段寄存器稱為cs, ss, ds, es, fs和gs。盡管只有6個(gè)段寄存器,但程序可以把同一個(gè)段寄存器用于不同的目的,方法是先將其值保存在存儲(chǔ)器中,用完后再恢復(fù)。

6個(gè)寄存器中3個(gè)有專門(mén)的用途:

cs——代碼段寄存器,指向包含程序指令的段。

ss——棧段寄存器,指向包含當(dāng)前程序棧的段。

ds——數(shù)據(jù)段寄存器,指向包含靜態(tài)數(shù)據(jù)或者全局?jǐn)?shù)據(jù)的段。

其它三個(gè)段寄存器作一般用途,可以指向任意的數(shù)據(jù)段。

每個(gè)段由一個(gè)8字節(jié)的描述子(Segment Descriptor)表示,它描述了段的特征。描述子放在全局描述符表(Global Descriptor Table, GDT)或局部描述符表(Local Descriptor Table, LDT)中,這些表位于內(nèi)存中,如圖所示。如果是多CPU,則每個(gè)CPU定義一個(gè)GDT,而每個(gè)進(jìn)程除了存放在GDT中的段之外如果還需要?jiǎng)?chuàng)建附加的段,就可以有自己的LDT。GDT在主存中的基地址和大小存放在gdtr處理器寄存器中,當(dāng)前正被使用的LDT地址和大小放在ldtr處理器寄存器中。

虛擬地址由16位選擇子和32位偏移量組成,段寄存器僅僅存放選擇子。CPU的分段單元(SU)執(zhí)行以下操作:

[1] 先檢查選擇子的TI字段,以決定描述子對(duì)應(yīng)的描述子保存在哪一個(gè)描述符表中。TI字段指明描述子是在GDT中(在這種情況下,分段單元從gdtr寄存器中得到GDT的線性基地址)還是在激活的LDT中(在這種情況下,分段單元從ldtr寄存器中得到LDT的線性基地址)。

[2] 從選擇子的index字段計(jì)算描述子的地址,index字段的值乘以8(一個(gè)描述子的大小,其實(shí)就是屏蔽掉末尾那三位指示特權(quán)級(jí)的CPL和指示TI的字段),這個(gè)結(jié)果與gdtr或ldtr寄存器中的內(nèi)容相加。

[3] 將對(duì)應(yīng)的描述子從內(nèi)存拷貝到CPU的隱Cache中,這樣,只有在選擇子改變的情況下才會(huì)修改Cache中的內(nèi)容。

[4] 把邏輯地址的偏移量與隱Cache中描述子Base字段的值相加就得到了線性地址。

請(qǐng)注意,多虧了與段寄存器相關(guān)的不可編程的隱Cache,只有當(dāng)段寄存器的內(nèi)容被改變時(shí)才需要執(zhí)行前三個(gè)操作。

LDT在Linux中使用得很少,我們就不細(xì)說(shuō)他了,它跟我們下面講的IDT差不多。

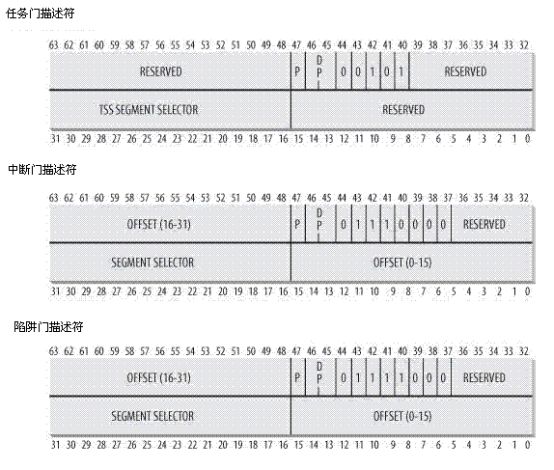

中斷描述符表(Interrupt Descriptor Table,IDT)是一個(gè)系統(tǒng)表,它與每一個(gè)中斷或異常向量相聯(lián)系,每一個(gè)向量在表中有相應(yīng)的中斷或異常處理程序的入口地址。內(nèi)核在允許中斷發(fā)生前,必須適當(dāng)?shù)爻跏蓟疘DT。

IDT的格式與這GDT和LDT的格式非常相似,表中的每一項(xiàng)對(duì)應(yīng)一個(gè)中斷或異常向量,每個(gè)向量由8個(gè)字節(jié)組成。因此,最多需要256×8=2048字節(jié)來(lái)存放IDT(Linux有256個(gè)中斷向量)。

idtr寄存器使IDT可以位于內(nèi)存的任何地方,它指定IDT的線性基地址及其大小(最大長(zhǎng)度)。在允許中斷之前,必須用lidt匯編指令初始化idtr。

IDT包含三種類型的描述符,下圖顯示了每種描述符中的64位的含義。尤其值得注意的是,在40~43位的Type字段的值表示描述符的類型。

這里還要提一個(gè)問(wèn)題,就是TSS技術(shù)是個(gè)很過(guò)時(shí)的技術(shù),Linux并沒(méi)有按照Intel要求的那樣把TSSD(任務(wù)門(mén))存放到IDT中,而是存放在全局描述符GDT中。每個(gè)CPU的tr寄存器包含了對(duì)應(yīng)TSS的TSSD選擇符(這個(gè)選擇符可以編程),還包含了兩個(gè)隱藏的非編程字段:TSSD的Base字段和Limit字段作為隱Cache,這樣,處理器就能直接對(duì)TSS尋址而不用從GDT中檢索TSS的地址。TSS這個(gè)東西主要用來(lái)在進(jìn)程切換的時(shí)候保存部分CPU寄存器的內(nèi)容(其實(shí)就主要是堆棧切換的時(shí)候使用到的那些寄存器)。Linux只為每個(gè)CPU準(zhǔn)備一個(gè)TSS數(shù)據(jù)結(jié)構(gòu)——tss_struct,只是用來(lái)存放當(dāng)前進(jìn)程的部分寄存器內(nèi)容,并沒(méi)有按照Intel推薦的那樣為每個(gè)進(jìn)程準(zhǔn)備一個(gè)TSS數(shù)據(jù)結(jié)構(gòu),并存放所有的內(nèi)容。所以,按照我的理解,每個(gè)進(jìn)程的那個(gè)thread_struct結(jié)構(gòu)存放的內(nèi)容就是當(dāng)進(jìn)程被執(zhí)行的時(shí)候需要tss_struct記住的那些寄存器的內(nèi)容。

當(dāng)執(zhí)行了一條指令后,CS和eip這對(duì)寄存器包含下一條將要執(zhí)行的指令的邏輯地址。在處理那條指令之前,控制單元會(huì)檢查在運(yùn)行前一條指令時(shí)是否已經(jīng)發(fā)生了一個(gè)中斷或異常。如果發(fā)生了一個(gè)中斷或異常,那么控制單元執(zhí)行下列操作:

1. 確定與中斷或異常關(guān)聯(lián)的向量i (0 ≤ i ≤ 255)。

2. 讀由idtr寄存器指向的 IDT表中的第i項(xiàng)。

3. 從gdtr寄存器獲得GDT的基地址,并在GDT中查找,以讀取IDT表項(xiàng)中的選擇符所標(biāo)識(shí)的段描述符。這個(gè)描述符將會(huì)是一個(gè)中斷門(mén)或者一個(gè)陷阱門(mén),其含有指定中斷或異常處理程序所在段的基地址。

4. 確信中斷是由授權(quán)的(中斷)發(fā)生源發(fā)出的。首先將當(dāng)前特權(quán)級(jí)CPL(存放在cs寄存器的低兩位)與段描述符(存放在GDT中)的描述符特權(quán)級(jí)DPL比較,如果CPL小于DPL,就產(chǎn)生一個(gè)“General protection”異常,因?yàn)橹袛嗵幚沓绦虻奶貦?quán)不能低于引起中斷的程序的特權(quán)。對(duì)于編程異常,則做進(jìn)一步的安全檢查:比較CPL與處于IDT中的門(mén)描述符的DPL,如果DPL小于CPL,就產(chǎn)生一個(gè)“General protection”異常。這最后一個(gè)檢查可以避免用戶應(yīng)用程序訪問(wèn)特殊的陷阱門(mén)或中斷門(mén)。

5. 檢查是否發(fā)生了特權(quán)級(jí)的變化,也就是說(shuō),CPL是否不同于所選擇的段描述符的DPL。如果是,控制單元必須開(kāi)始使用與新的特權(quán)級(jí)相關(guān)的棧。通過(guò)執(zhí)行以下步驟來(lái)做到這點(diǎn):

i. 讀tr寄存器,以訪問(wèn)運(yùn)行進(jìn)程的TSS段。

ii. 用與新特權(quán)級(jí)相關(guān)的棧段和棧指針的正確值裝載ss和esp寄存器。這些值可以在TSS中找到。

iii. 在新的棧中保存ss和esp以前的值,這些值定義了與舊特權(quán)級(jí)相關(guān)的棧的邏輯地址。

6. 如果故障已發(fā)生,用引起異常的指令地址裝載CS和eip寄存器,從而使得這條指令能再次被執(zhí)行。

7. 在棧中保存eflags、CS及eip的內(nèi)容。

8. 如果異常產(chǎn)生了一個(gè)硬件出錯(cuò)碼,則將它保存在棧中。

9. 裝載cs和eip寄存器,其值分別是IDT表中第i項(xiàng)門(mén)描述符的段選擇符和偏移量字段。這些值給出了中斷或者異常處理程序的第一條指令的邏輯地址。

控制單元所執(zhí)行的最后一步就是跳轉(zhuǎn)到中斷或者異常處理程序。換句話說(shuō),處理完中斷信號(hào)后,控制單元所執(zhí)行的指令就是被選中處理程序的第一條指令。

中斷或異常被處理完后,相應(yīng)的處理程序必須產(chǎn)生一條iret指令,把控制權(quán)轉(zhuǎn)交給被中斷的進(jìn)程,這將迫使控制單元:

1. 用保存在棧中的值裝載CS、eip或eflags寄存器。如果一個(gè)硬件出錯(cuò)碼曾被壓入棧中,并且在eip內(nèi)容的上面,那么,執(zhí)行iret指令前必須先彈出這個(gè)硬件出錯(cuò)碼。

2. 檢查處理程序的CPL是否等于CS中最低兩位的值(這意味著被中斷的進(jìn)程與處理程序運(yùn)行在同一特權(quán)級(jí))。如果是,iret終止執(zhí)行;否則,轉(zhuǎn)入下一步。

3. 從棧中裝載ss和esp寄存器,因此,返回到與舊特權(quán)級(jí)相關(guān)的棧。

4. 檢查ds、es、fs及gs段寄存器的內(nèi)容,如果其中一個(gè)寄存器包含的選擇符是一個(gè)段描述符,并且其DPL值小于CPL,那么,清相應(yīng)的段寄存器。控制單元這么做是為了禁止用戶態(tài)的程序(CPL=3)利用內(nèi)核以前所用的段寄存器(DPL=0)。如果不清這些寄存器,懷有惡意的用戶態(tài)程序就可能利用它們來(lái)訪問(wèn)內(nèi)核地址空間。

3 PU模塊

分頁(yè)單元PU模塊的目的是把線性地址轉(zhuǎn)換成物理地址。其中一個(gè)關(guān)鍵任務(wù)是把所請(qǐng)求的訪問(wèn)類型與線性地址的訪問(wèn)權(quán)限相比較,如果這次內(nèi)存訪問(wèn)是無(wú)效的,就產(chǎn)生一個(gè)缺頁(yè)異常。

分頁(yè)單元把所有的主存看成一塊一塊的,稱其為頁(yè)框(page frame)(有時(shí)叫做物理頁(yè))。每一個(gè)頁(yè)框是固定的大小(跟分段的最大區(qū)別,一般為32位處理器為4k、64位處理器為64k)包含一個(gè)頁(yè)(page)。

把線性地址映射到物理地址的數(shù)據(jù)結(jié)構(gòu)稱為頁(yè)表(page table),其存放在主存中,并在啟用分頁(yè)單元之前必須由內(nèi)核對(duì)頁(yè)表進(jìn)行適當(dāng)?shù)某跏蓟?0386開(kāi)始,所有的80x86處理器都支持分頁(yè),它通過(guò)設(shè)置cr0寄存器的PG標(biāo)志啟用。當(dāng)PG=0時(shí),線性地址就被解釋成物理地址。

從80386起,Intel處理器的分頁(yè)單元處理4KB的頁(yè)。32位的線性地址被分成3個(gè)字段:

目錄(Directory)——最高10位

頁(yè)表(Table)——中間10位

偏移量(Offset)——最低12位

當(dāng)一個(gè)進(jìn)程運(yùn)行時(shí),必須有一個(gè)分配給它的頁(yè)目錄,其每一個(gè)目錄項(xiàng)指向一個(gè)頁(yè)表的地址。不過(guò),沒(méi)有必要馬上為進(jìn)程的所有頁(yè)表都分配內(nèi)存。Linux是在當(dāng)進(jìn)程實(shí)際需要一個(gè)頁(yè)表時(shí)才給該頁(yè)表分配RAM以提高效率。

正在使用的頁(yè)目錄的物理地址存放在控制寄存器cr3中。線性地址內(nèi)的最高10位(Directory字段)決定頁(yè)目錄中的目錄項(xiàng),而目錄項(xiàng)指向適當(dāng)?shù)捻?yè)表。地址的中間10位(Table字段)依次又決定頁(yè)表中的表項(xiàng),而表項(xiàng)含有頁(yè)所在頁(yè)框的物理地址。最低12位(Offset字段)決定頁(yè)框內(nèi)的相對(duì)位置(見(jiàn)圖)。由于它是12位長(zhǎng),故每一頁(yè)含有4096字節(jié)的數(shù)據(jù)。

頁(yè)目錄項(xiàng)和頁(yè)表項(xiàng)有同樣的結(jié)構(gòu),每項(xiàng)的內(nèi)容主要包括對(duì)應(yīng)頁(yè)(頁(yè)表也是一個(gè)頁(yè))的索引以及對(duì)應(yīng)頁(yè)的狀態(tài),我們將在存儲(chǔ)管理中分段Linux分段分頁(yè)機(jī)制博文中詳細(xì)介紹。

下面再來(lái)談?wù)劮猪?yè)的硬件保護(hù)方案,分頁(yè)單元和分段單元的保護(hù)方案不同。盡管80x86處理器允許一個(gè)段使用四種可能的特權(quán)級(jí)別,但與頁(yè)和頁(yè)表相關(guān)的特權(quán)級(jí)只有兩個(gè),由頁(yè)目錄項(xiàng)和頁(yè)表項(xiàng)有同樣的結(jié)構(gòu)的User/Supervisor標(biāo)志所控制。若這個(gè)標(biāo)志為0,只有當(dāng)CPL小于3(這意味著對(duì)于Linux而言,處理器處于內(nèi)核態(tài))時(shí)才能對(duì)頁(yè)尋址;若該標(biāo)志為1,則總能對(duì)頁(yè)尋址。

此外,與段的三種存取權(quán)限(讀,寫(xiě),執(zhí)行)不同的是,頁(yè)的存取權(quán)限只有兩種(讀,寫(xiě))。如果頁(yè)目錄項(xiàng)或頁(yè)表項(xiàng)的Read/Write標(biāo)志等于0,說(shuō)明相應(yīng)的頁(yè)表或頁(yè)是只讀的,否則是可讀寫(xiě)的。

4 高速緩存

當(dāng)今的微處理器時(shí)鐘頻率接近幾個(gè)GHZ,而動(dòng)態(tài)RAM(DRAM)芯片的存取時(shí)間是時(shí)鐘周期的數(shù)百倍。這意味著,當(dāng)從RAM中取操作數(shù)或向RAM中存放結(jié)果這樣的指令執(zhí)行時(shí),CPU可能等待很長(zhǎng)時(shí)間。

為此,80x86體系結(jié)構(gòu)中引入了一個(gè)叫行(line)的新單位。行由幾十個(gè)連續(xù)的字節(jié)組成,它們以脈沖突發(fā)模式(burst mode)在慢速DRAM和快速的片上靜態(tài)RAM(SRAM)之間傳送,用來(lái)實(shí)現(xiàn)高速緩存。

具體的高速緩存實(shí)現(xiàn)細(xì)節(jié)太復(fù)雜,我只簡(jiǎn)單地說(shuō)說(shuō)原理:當(dāng)訪問(wèn)一個(gè)RAM存儲(chǔ)單元時(shí),CPU從物理地址中提取出子集的索引號(hào)并把子集中所有行的標(biāo)簽與物理地址的高幾位相比較。如果發(fā)現(xiàn)某一個(gè)行的標(biāo)簽與這個(gè)物理地址的高位相同,則CPU命中一個(gè)高速緩存(cache hit);否則,高速緩存沒(méi)有命中(cache miss)。

當(dāng)命中一個(gè)高速緩存時(shí),高速緩存控制器的操作不同,具體取決于存取類型。 對(duì)于讀操作,控制器從高速緩存行中選擇數(shù)據(jù)并送到CPU寄存器;RAM不被訪問(wèn)且節(jié)約了CPU時(shí)間,因此,高速緩存系統(tǒng)起到了其應(yīng)有的作用。對(duì)于寫(xiě)操作,控制器可能采用以下兩個(gè)基本策略之一,分別稱之為通寫(xiě)(writethrough)和回寫(xiě)(writeback)。在通寫(xiě)中,控制器總是既寫(xiě)RAM 也寫(xiě)高速緩存行,為了提高寫(xiě)操作的效率關(guān)閉高速緩存。回寫(xiě)方式只更新高速緩存行,不改變RAM的內(nèi)容,提供了更快的功效。當(dāng)然,回寫(xiě)結(jié)束以后,RAM最終必須被更新。只有當(dāng)CPU執(zhí)行一條要求刷新高速緩存表項(xiàng)的指令時(shí),或者當(dāng)一個(gè)FLUSH硬件信號(hào)產(chǎn)生時(shí)(通常在高速緩存不命中發(fā)生之后), 高速緩存控制器才把高速緩存行寫(xiě)回到RAM中。

當(dāng)高速緩存沒(méi)有命中時(shí),高速緩存行被寫(xiě)回到內(nèi)存中,如果有必要的話,把正確的行從RAM中取出放到高速緩存的表項(xiàng)中。很復(fù)雜吧?我們應(yīng)該大肆慶幸,因?yàn)樗羞@一切都在硬件級(jí)處理,內(nèi)核根本不需要關(guān)心。

高速緩存技術(shù)正在快速向前發(fā)展。例如,第一代Pentium芯片包含一顆稱為L(zhǎng)1-cache的片上高速緩存。近期的芯片又包含另外的容量更大,速度較慢,稱之為L(zhǎng)2-cache,L3-cache的片上高速緩存。多級(jí)高速緩存之間的一致性是由硬件實(shí)現(xiàn)的。Linux忽略這些硬件細(xì)節(jié)并假定只有一個(gè)單獨(dú)的高速緩存。

處理器的cr0寄存器的CD標(biāo)志位用來(lái)啟用或禁用高速緩存電路。這個(gè)寄存器中的NW標(biāo)志指明高速緩存是使用通寫(xiě)還是回寫(xiě)策略。

除了通用硬件高速緩存之外, 80x86處理器還包含了另外一個(gè)稱之為翻譯后備緩沖器或TLB(Translation Lookaside Buffer,有些書(shū)上也把這組寄存器叫做“聯(lián)想存儲(chǔ)器”)的高速緩存用于加快線性地址的轉(zhuǎn)換。當(dāng)一個(gè)線性地址被第一次使用時(shí),通過(guò)慢速訪問(wèn)RAM中的頁(yè)表計(jì)算出相應(yīng)的物理地址。同時(shí),物理地址被存放在一個(gè)TLB表項(xiàng)(TLB entry)中,以便以后對(duì)同一個(gè)線性地址的引用就可以快速地得到轉(zhuǎn)換,如圖。

例如CPU給出有效地址為(D,P,W),它把頁(yè)號(hào)P送入輸入寄存器,隨后立即和TLB各單元的頁(yè)號(hào)進(jìn)行比較,如與某個(gè)單元中的頁(yè)號(hào)相匹配,則把該單元中的塊號(hào)B送入輸出寄存器。這樣,就可以用(D,B,W)訪問(wèn)相應(yīng)的主存單元。

在多處理系統(tǒng)中,每個(gè)CPU都有自己的TLB,這叫做該CPU的本地TLB。與硬件高速緩存相反,TLB中的對(duì)應(yīng)項(xiàng)不必同步,這是因?yàn)檫\(yùn)行在現(xiàn)有CPU上的進(jìn)程可以使同一線性地址與不同的物理地址發(fā)生聯(lián)系。

當(dāng)CPU的cr3控制寄存器被修改時(shí),硬件自動(dòng)使本地TLB中的所有項(xiàng)都無(wú)效,這是因?yàn)樾碌囊唤M頁(yè)表被啟用而TLB指向的是舊數(shù)據(jù)。

做嵌入式系統(tǒng)開(kāi)發(fā),經(jīng)常要接觸硬件。做嵌入式開(kāi)發(fā)對(duì)數(shù)字電路和模擬電路要有一定的了解。這樣才能深入的研究下去。下面我們簡(jiǎn)單的介紹嵌入式開(kāi)發(fā)中的一些硬件相關(guān)的概念。

總線(Bus)

在嵌入式系統(tǒng)中一定會(huì)有一塊處理器芯片,此外,還有其它的芯片作為外部設(shè)備(后面簡(jiǎn)稱外設(shè)),這些芯片與處理器協(xié)作實(shí)現(xiàn)產(chǎn)品的功能。復(fù)雜的產(chǎn)品往往是由大量的芯片組成的。那么不可避免的是我們需要將所有的外設(shè)與處理器進(jìn)行相連,最為簡(jiǎn)單的是將所有的外設(shè)都采用獨(dú)立(注意是獨(dú)立)的信號(hào)線連接至處理器,這樣的好處是容易理解,但問(wèn)題是:不可行。

因?yàn)樘幚砥餍酒枰鎏嗟木€了,從芯片的生產(chǎn)和產(chǎn)品的生產(chǎn)角度來(lái)看都不實(shí)際。加之,處理器(在此我們假設(shè)處理器是單核的,而不是多核的)處理事務(wù)在微觀上是串行的,也就是說(shuō)在某一時(shí)刻如果要對(duì)外設(shè)進(jìn)行讀寫(xiě)操作,那只可能是對(duì)大量外設(shè)中的一個(gè)進(jìn)行,即多個(gè)外設(shè)不可能在微觀上被處理器同時(shí)訪問(wèn)。

需要注意的是,這里提出了微觀這一概念,這是為了區(qū)別于宏觀。從宏觀上來(lái)講,一個(gè)處理器中可以有多個(gè)任務(wù)同時(shí)運(yùn)行,但這些任務(wù)在微觀上卻是一個(gè)一個(gè)運(yùn)行的(后面會(huì)用串行來(lái)描述這里所說(shuō)的“一個(gè)一個(gè)”),多任務(wù)的串行運(yùn)行實(shí)現(xiàn)是由操作系統(tǒng)扮演著重要的角色來(lái)實(shí)現(xiàn)的。

回到我們的話題,即然將每個(gè)外設(shè)采用獨(dú)立的信號(hào)線連到處理器不可行,且處理器在單一時(shí)間內(nèi)只會(huì)對(duì)一個(gè)外設(shè)進(jìn)行訪問(wèn),那我們能不能采用共享的信號(hào)線將所有的芯片連在一起呢?這就是總線概念的由來(lái)。通俗的說(shuō),如果我們周?chē)惺畟€(gè)家庭,為了讓這十個(gè)家庭每?jī)蓚€(gè)之間都能往來(lái),我們并不需要為每?jī)蓚€(gè)家庭修一條單獨(dú)(注意是單獨(dú))的路(如果這樣,要修45條路),而是可以修一條大路,然后,每個(gè)家都與大路相連。

對(duì)于總線,我們往往說(shuō)總線是處理器的,而其它的外設(shè)是掛在總線上的。那有一個(gè)問(wèn)題,我們每一時(shí)間只能訪問(wèn)掛在總線上的一個(gè)外設(shè),那如何區(qū)分這些外設(shè)呢?和我們的路一樣,我們需要用地址來(lái)區(qū)分每一個(gè)家庭,在總線上,也是采用地址來(lái)進(jìn)行區(qū)分的。

這樣,總線就根據(jù)其功能分為兩類了。一類是地址總線,這一總線上的數(shù)據(jù)只會(huì)是從處理器向外設(shè)“流”,是單向的。另一類則是數(shù)據(jù)總線,用來(lái)將數(shù)據(jù)從處理器傳送到外設(shè)(從處理器的角度來(lái)說(shuō)是寫(xiě)操作)或者是將數(shù)據(jù)從外設(shè)傳送到處理器(從處理器的角度來(lái)說(shuō)是讀操作),顯然,數(shù)據(jù)總線是雙向的。也就是說(shuō),在我們的嵌入式系統(tǒng)中同時(shí)存在地址總線和數(shù)據(jù)總線將所有需要與處理器進(jìn)行通訊的芯片連在一起的。

總線是有寬度的,正如我們的路分為“三車(chē)道”或是“四車(chē)道”,我們說(shuō)32位處理器,是指其數(shù)據(jù)總線寬度是32位,也就是“有32輛車(chē)能同時(shí)跑”,顯然,寬度越是寬我們的處理器速度就越是快,因?yàn)槲覀儚耐庠O(shè)芯片存取數(shù)據(jù)的速度會(huì)更快,這就是為什么我們的計(jì)算機(jī)向64位發(fā)展的原因。同樣的,地址總線也是有寬度的,對(duì)于32位處理器其最大寬度也就是32位。

總線的概念有了,那接下來(lái)的一個(gè)問(wèn)題是,即使是每一個(gè)外設(shè)都有一個(gè)地址,那這一地址記在哪里呢?是放在外設(shè)芯片上嗎?如果這樣的話,那就有一個(gè)問(wèn)題,每一類外設(shè)的地址必須是不能重疊的,而當(dāng)一個(gè)產(chǎn)品中需要兩塊一樣的芯片的話,兩塊芯片的地址就無(wú)法區(qū)分了,看來(lái)這樣操作存在問(wèn)題。還有,如果這樣的話每一個(gè)外設(shè)也得與(比如,32根)數(shù)據(jù)總線完全相連,并監(jiān)聽(tīng)數(shù)據(jù)線以了解處理器是不是在“叫”自己,這樣很是復(fù)雜。

此外,地址也有可能因?yàn)橥庠O(shè)種類的增多而用光。總的來(lái)說(shuō)地址不能存放在外設(shè)芯片,那如何讓外設(shè)知道,此時(shí)它是被處理器招換從而需要進(jìn)行讀寫(xiě)訪問(wèn)的呢?答案就是芯片的片選(CS, chip select)信號(hào),或者又號(hào)使能(ENable)信號(hào)。

片選(CS 或EN)

片選信號(hào)對(duì)于外設(shè)芯片來(lái)講,就是一個(gè)(也是一根)通知信號(hào),告訴芯片“嘿,請(qǐng)開(kāi)門(mén),我要放些東西進(jìn)來(lái),或是拿些東西走”,這里的東西只能是數(shù)據(jù),不可能是玉米棒什么的。那有個(gè)問(wèn)題,這個(gè)信號(hào)源從哪里來(lái)呢?顯然,只能從處理器來(lái)。那是不是也是像總線那樣,每一個(gè)芯片都共用一根線連在一起呢?

如果這樣,可能處理器“一叫開(kāi)門(mén)”所有的芯片都將“門(mén)”打開(kāi)了。如果是處理器寫(xiě)數(shù)據(jù),那可能所有的芯片都被寫(xiě)入同樣的數(shù)據(jù)。而取數(shù)據(jù)時(shí),每個(gè)外設(shè)芯片都向外“扔”數(shù)據(jù),這一定會(huì)造成數(shù)據(jù)總線沖突,因?yàn)橛械男酒蚩偩€上“扔”1,有的則“扔”0,這種情況下處理器一定會(huì)“發(fā)瘋”的,因?yàn)樗恢缿?yīng)當(dāng)?shù)玫?還是0。

即然這樣,那顯然不能將所有的片選信號(hào)連在一起了,只能是各芯片的片選信號(hào)獨(dú)立。前面提到了地址總線,我們是采用一根地址線連一個(gè)外設(shè)芯片呢?還是采用其它的方法。如果采用一根地址線連一個(gè)外設(shè)芯片,那可能最多只能掛接32個(gè)芯片了,這顯然不行。

其實(shí),在現(xiàn)實(shí)中,是采用32位的數(shù)字來(lái)表示一個(gè)外設(shè)芯片的地址的,比如1可以表示芯片A,而6534可以表示另外一個(gè)芯片B,等等。由此看來(lái),理論上我們可以表示2的32次方(4294967296)個(gè)設(shè)備,之所以說(shuō)理論上,是因?yàn)橛械脑O(shè)備要占用大量的地址。即然這樣,那還有一個(gè)問(wèn)題,如果將32位的地址總線轉(zhuǎn)換成芯片的一根片選信號(hào)呢?這需要引入譯碼(器)的概念。

譯碼(器)

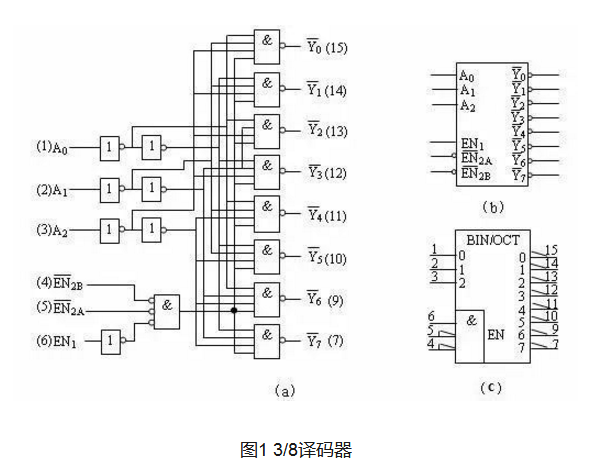

譯碼器將一個(gè)數(shù)據(jù)轉(zhuǎn)換成一根信號(hào)線上的信號(hào),比如3/8譯碼器,可以將一個(gè)位寬是3位的數(shù)據(jù)轉(zhuǎn)換成8根(2的3次方)完全獨(dú)立的信號(hào)線,當(dāng)向數(shù)據(jù)側(cè)寫(xiě)入二進(jìn)制的011時(shí),對(duì)應(yīng)的是8根線的第3根,當(dāng)輸入二進(jìn)制的111時(shí),對(duì)應(yīng)的是8根線中的最后一根。有了譯碼器,處理器的地址線就簡(jiǎn)化了,只要32根地址線加上外面的譯碼器,就可以訪問(wèn)大量的外設(shè)芯片了。外部設(shè)備的選擇問(wèn)題,我們已經(jīng)解決了,現(xiàn)在還得回頭看一看數(shù)據(jù)總線。

在嵌入式系統(tǒng)中,所有芯片的數(shù)據(jù)總線可以理解成是直接相連的。之所以用了“可以理解”一詞,是因?yàn)闉榱颂岣呖偩€的負(fù)載能力,其中會(huì)加入總線驅(qū)動(dòng)器。為了理解,我們看一看我們生活中的自來(lái)水,比如,在北京理論上可能所有的水管是連在一起的,但中間可能為了提高水壓,存在很多小的水站用來(lái)增加供水壓力,而不可能全北京所有的自來(lái)水自接來(lái)自一個(gè)水廠。

即然所有的數(shù)據(jù)總線是連在一起的,那就可能會(huì)有問(wèn)題。當(dāng)向外部設(shè)備寫(xiě)數(shù)據(jù)時(shí),處理器先向地址總線輸送目標(biāo)外設(shè)的地址,地址譯碼器將其轉(zhuǎn)換成一根信號(hào)的片選信號(hào)送到了目標(biāo)外設(shè),目標(biāo)外設(shè)收到這一信號(hào)后,將“門(mén)”打開(kāi)。接下來(lái)處理器將要傳送到外設(shè)的數(shù)據(jù)往數(shù)據(jù)總線上一放,由于只有目標(biāo)外設(shè)芯片打開(kāi)了“門(mén)”,所以數(shù)據(jù)只會(huì)進(jìn)入到目標(biāo)外設(shè),而其它的外設(shè)什么也不會(huì)收到。很好!處理器向外寫(xiě)數(shù)據(jù)應(yīng)當(dāng)沒(méi)有問(wèn)題,我們接下來(lái)看一看讀。讀的話,由于數(shù)據(jù)是從外設(shè)輸送到處理器的,盡管我們采用和寫(xiě)一樣的方法打開(kāi)目標(biāo)外設(shè)的“門(mén)”,但此時(shí),其它的外設(shè)也在數(shù)據(jù)總線上,它們有可能處于1也可能處于0,是不是會(huì)影響處理器讀取目標(biāo)外設(shè)的數(shù)據(jù)呢?結(jié)果當(dāng)然不會(huì),但我們得引入另一個(gè)概念:高阻態(tài)。

高阻態(tài)

很顯然,當(dāng)處理器從目標(biāo)外設(shè)讀數(shù)據(jù)時(shí),我們希望其它沒(méi)有被選上的芯片的數(shù)據(jù)總線不會(huì)對(duì)目標(biāo)外設(shè)所要傳送的數(shù)據(jù)有影響,那怎么辦呢?實(shí)際上,當(dāng)芯片沒(méi)有被選中時(shí),其數(shù)據(jù)總線都處于高阻態(tài)。所謂的高阻態(tài),我們可以理解成這一管腳在外設(shè)芯片內(nèi)部是斷開(kāi)的,如此一來(lái),顯然不會(huì)對(duì)處理器從目標(biāo)外設(shè)讀取數(shù)據(jù)造成任何的影響了。我們說(shuō)當(dāng)一個(gè)芯片沒(méi)有被選中或是沒(méi)有被使能時(shí),其數(shù)據(jù)總線一定是處于高阻態(tài)的。前面用了“門(mén)”的開(kāi)和關(guān)來(lái)打比方,那“門(mén)”是指什么呢?是指外設(shè)的數(shù)據(jù)總線,片選信號(hào)的作用就是控制將外設(shè)的數(shù)據(jù)總線與處理器的數(shù)據(jù)總線相連或是斷開(kāi)。更多的關(guān)于高阻態(tài)的講解可參看前面寫(xiě)的文章《高阻態(tài)和三態(tài)門(mén)》。

驅(qū)動(dòng)

總線上的數(shù)據(jù)是誰(shuí)放上去的我們就說(shuō)誰(shuí)是那一時(shí)刻的驅(qū)動(dòng)者。也就是說(shuō),當(dāng)處理器向外設(shè)寫(xiě)數(shù)據(jù)時(shí),它是在驅(qū)動(dòng)數(shù)據(jù)總線的,而當(dāng)處理器從目標(biāo)外設(shè)讀取數(shù)據(jù)時(shí),目標(biāo)外設(shè)是在驅(qū)動(dòng)數(shù)據(jù)總線的。對(duì)于地址總線,因?yàn)橹豢赡軓奶幚砥飨蚰繕?biāo)外設(shè)寫(xiě),所以地址總線永遠(yuǎn)是由處理器驅(qū)動(dòng)的。當(dāng)一個(gè)芯片沒(méi)有被選中時(shí),我們說(shuō)它并不驅(qū)動(dòng)數(shù)據(jù)總線。

三態(tài)門(mén)

前面我們說(shuō)到外設(shè)芯片的數(shù)據(jù)總線在沒(méi)有被選中時(shí)其處于高阻態(tài),當(dāng)被選中時(shí),其電平可能是高(1)或是低(0)。如此一來(lái),我們說(shuō)外設(shè)的數(shù)據(jù)總線其芯片管腳是屬于三態(tài)門(mén)的,即存在高電平、低電平和高阻態(tài),三個(gè)狀態(tài)。更多的關(guān)于三態(tài)門(mén)的講解可參看前面寫(xiě)的文章《高阻態(tài)和三態(tài)門(mén)》。

電平的有效性

前面我們了解了什么是片選信號(hào),也講到了三態(tài)門(mén),需要指出的是片選信號(hào)通常不是三態(tài)門(mén),其只存在兩個(gè)狀態(tài),即高電平或是低電平。前面我們也說(shuō)了,片選信號(hào)是用來(lái)“開(kāi)門(mén)”的,而片選信號(hào)又有高和低電平,那到底是高電平表示“開(kāi)門(mén)”呢?還是低電平?對(duì)于這一問(wèn)題,我們稱如果一個(gè)電平對(duì)于一個(gè)片選信號(hào)表示“開(kāi)門(mén)”那么它就是這一信號(hào)的有效電平。比如,對(duì)于一個(gè)片選信號(hào),如果低電平表示“開(kāi)門(mén)”,那么我們說(shuō)這個(gè)片選信號(hào)是低電平有效的。雖然,在這里我們用片選信號(hào)來(lái)解釋電平的有效性,但是很多信號(hào)都存在有效性的問(wèn)題,比如,后面我們將要談的讀信號(hào)和寫(xiě)信號(hào)都存在有效性問(wèn)題。

時(shí)序

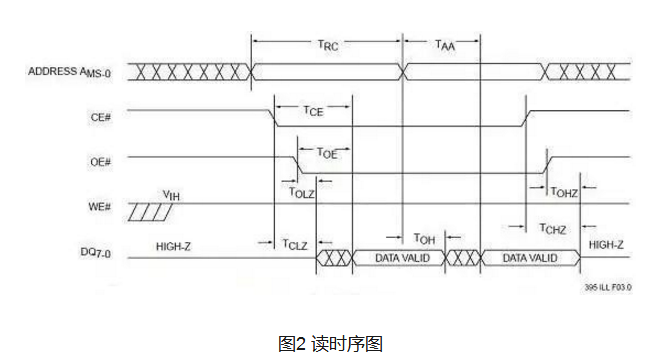

在前面我們說(shuō)到當(dāng)處理器要向外設(shè)芯片寫(xiě)數(shù)據(jù)時(shí),需要先將所需訪問(wèn)的外設(shè)的地址放在地址總線上,然后,由譯碼器將地址總線上的數(shù)據(jù)轉(zhuǎn)換成片選信號(hào),片選信號(hào)則使能目標(biāo)外設(shè)芯片,接下來(lái)處理器寫(xiě)數(shù)據(jù)到數(shù)據(jù)總線上,從而完成一個(gè)寫(xiě)操作。顯然,在處理器將數(shù)據(jù)寫(xiě)到數(shù)據(jù)總線之前地址線上的數(shù)據(jù)必須一直保留一段時(shí)間,否則的話譯碼器不能長(zhǎng)時(shí)間的使片選信號(hào)有效。當(dāng)完成了數(shù)據(jù)的寫(xiě)操作后,處理器就不需要保證地址總線上的地址有效了。我們可以看出,這一系列的操作都有一定嚴(yán)格的時(shí)間順序的,這稱之為時(shí)序。時(shí)序描述了處理器與外部設(shè)備的交互信號(hào) “規(guī)程”,大家只有按照這一“規(guī)程”來(lái)操作,才能保證處理器與外部設(shè)備之間能正常的通訊。這好比,我們的道路上的紅綠燈,如果我們行人和車(chē)輛不按照其指示來(lái)通行的話,就會(huì)出現(xiàn)事故。通常,采用時(shí)序圖來(lái)描述芯片之間通訊的信號(hào)“規(guī)程”。

從圖中我們可以看出ADDRESS是表示地址總線的,DQ是表示數(shù)據(jù)總線的,CE是片選信號(hào),且是低電平有效,其寬度要保證在進(jìn)行讀操作時(shí)總是有效的。學(xué)會(huì)看時(shí)序圖對(duì)于做嵌入式系統(tǒng)開(kāi)發(fā)非常有幫助,因?yàn)槲覀儾豢杀苊獾囊c芯片打交道。在時(shí)序圖中,通常會(huì)標(biāo)識(shí)很多的時(shí)間需求信息。在寫(xiě)啟動(dòng)代碼時(shí)需要初始化各地址空間的片選地址寄存器和讀寫(xiě)時(shí)序,時(shí)序的配置依據(jù)就是來(lái)自于外設(shè)芯片的時(shí)間需求,這是芯片手冊(cè)很重要的一部分內(nèi)容。當(dāng)一個(gè)地址空間中存在多個(gè)外設(shè)芯片時(shí),我們需要考慮到其中最慢的外設(shè)芯片的時(shí)間需求,否則的話有的芯片就不能正常工作。

讀信號(hào)

當(dāng)處理器需要從外設(shè)芯片讀取信號(hào)時(shí),除了需要產(chǎn)生片選信號(hào)外,還需要告訴外設(shè)芯片這是一個(gè)讀操作,而不是一個(gè)寫(xiě)操作,這是通過(guò)讀信號(hào)來(lái)實(shí)現(xiàn)的。

寫(xiě)信號(hào)

前面講了讀信號(hào),我想對(duì)于寫(xiě)信號(hào)也就不難理解了,這個(gè)信號(hào)用于告訴外設(shè)芯片,這是一個(gè)向外設(shè)芯片寫(xiě)數(shù)據(jù)的操作。

I/O端口

前面提到了外設(shè)(芯片)),現(xiàn)在是對(duì)外設(shè)進(jìn)行分類的時(shí)候了。大體上外設(shè)分為兩類,一類是存儲(chǔ)器外設(shè),而另一類是非存儲(chǔ)器外設(shè),后者常被稱之為I/O設(shè)備,這里的I/O是Input/Output的簡(jiǎn)寫(xiě),即輸入、輸出。可見(jiàn),I/O外設(shè)是一個(gè)非常寬泛的概念。對(duì)于存儲(chǔ)器外設(shè),其特點(diǎn)是,它所占用的空間是連續(xù)的一片。比如,SDRAM內(nèi)存就是屬于存儲(chǔ)器外設(shè),如果其容量是8M字節(jié),那么其占用的地址空間也會(huì)是8M的。

與存儲(chǔ)器外設(shè)所不同的是,I/O外設(shè)所點(diǎn)用的地址一般都很少。比如一個(gè)I/O外設(shè)可能存在多個(gè)控制寄存器,這些控制寄存器從處理器來(lái)看就是多個(gè)I/O端口(地址),向這個(gè)地址寫(xiě)數(shù)據(jù)就是向外設(shè)所對(duì)應(yīng)的寄存器寫(xiě)數(shù)據(jù),反之,也可以是讀。比如,一個(gè)串口芯片可能存在多個(gè)寄存器,一個(gè)用來(lái)查詢芯片的狀態(tài),一個(gè)用來(lái)設(shè)置芯片的功能,另一個(gè)用來(lái)讀取芯片從串口線所收到的數(shù)據(jù),最后,還有一個(gè)用來(lái)向芯片寫(xiě)數(shù)據(jù)以向串口線上發(fā)送數(shù)據(jù)。對(duì)于這一串口芯片的寄存器,從處理器的角度來(lái)看,都是獨(dú)立的I/O端口。

I/O端口存在讀、寫(xiě)性問(wèn)題,有的端口是只讀的,有的端口是只寫(xiě)的,還有的端口是即可讀也可寫(xiě),其讀寫(xiě)性是由外設(shè)芯片的寄存器所決定的,在芯片的數(shù)據(jù)手冊(cè)中能找到。需要指出的是,有些存儲(chǔ)器外設(shè)也存在I/O端口,以對(duì)其進(jìn)行一定的控制。從I/O端口這一名字來(lái)看,對(duì)于處理器來(lái)說(shuō),就是對(duì)從外面讀入數(shù)據(jù)或是向外面輸出數(shù)據(jù)的一個(gè)接口總稱。

中斷

中斷從硬件的角度來(lái)看就是一個(gè)能產(chǎn)生高、低電平的一根信號(hào)線,但理解它需要從處理器的角度出發(fā)。我們說(shuō)過(guò)了,處理器從微觀上看,所做的工作是按順序進(jìn)行的,其對(duì)程序的處理只能是一條指令一條指令的執(zhí)行。如果存在需要對(duì)外設(shè)芯片進(jìn)行訪問(wèn),而有可能從處理器發(fā)出讀、寫(xiě)命令后,由于外設(shè)通常比處理器慢很多,所以外設(shè)芯片需要一些時(shí)間來(lái)準(zhǔn)備好所需的數(shù)據(jù)。在這種情況下,如果處理器一直等外設(shè)芯片的返回?cái)?shù)據(jù)再執(zhí)行后續(xù)的指令的話,將耗費(fèi)寶貴的時(shí)間,這些時(shí)間完全可以用來(lái)做其它的工作。

別忘了,從宏觀上看來(lái)處理器常常是多任務(wù)的,任務(wù)是指操作系統(tǒng)所提供的調(diào)度單位。當(dāng)一個(gè)任務(wù)因?yàn)榈却庠O(shè)芯片的數(shù)據(jù)而阻塞時(shí),我們可以切換到另外的任務(wù),從而提高處理效率。這就有一個(gè)問(wèn)題,當(dāng)處理器去處理另一個(gè)任務(wù)時(shí),如果外設(shè)芯片的數(shù)據(jù)好了的話,如果告訴處理器呢?對(duì)了!就是通過(guò)中斷信號(hào)。中斷信號(hào)的高、低電平可以用來(lái)表示是否有中斷需要處理器注意以處理特定的事件(比如,外設(shè)數(shù)據(jù)準(zhǔn)備好了的事件)。

由此看來(lái),中斷的引入能大大的提高處理器的運(yùn)用效率。為了使用處理器上的中斷,一開(kāi)始我們需要初始化好處理器的中斷控制器,比如安裝好所需的中斷服務(wù)程序或稱之為ISR(Interrupt Service Routine),然后,打開(kāi)中斷屏蔽位。中斷服務(wù)程序中需要做如下的操作:

1. 從外設(shè)讀入或向外設(shè)寫(xiě)數(shù)據(jù)。讀還是寫(xiě)通常需要讀取外設(shè)的中斷狀態(tài)寄存器來(lái)決定。

2. 清除外設(shè)的中斷信號(hào)。我們知道,中斷信號(hào)是由外設(shè)芯片驅(qū)動(dòng)的,為了告訴外設(shè)芯片,處理器已經(jīng)處理完了所需做的工作,那么處理器需要通過(guò)一定的方式通知外設(shè)芯片。這種方式就是向外設(shè)芯片的寄存器中的某一位寫(xiě)入一個(gè)數(shù)據(jù),比如,可能是寫(xiě)入1表示清中斷,也可能是寫(xiě)入0表示清中斷,這通常在外設(shè)的數(shù)據(jù)手冊(cè)中能查到。當(dāng)外設(shè)收到了處理器的清中斷請(qǐng)求后,其就會(huì)驅(qū)動(dòng)中斷線使其無(wú)效。比如,一個(gè)外設(shè)的中斷線是當(dāng)其為低電平表示有中斷,將其從低電平變?yōu)楦唠娖骄褪球?qū)動(dòng)為無(wú)效。

3. 清除處理器的中斷信號(hào)標(biāo)識(shí)。處理器中往往也會(huì)保存外部中斷信號(hào)是否發(fā)生過(guò),當(dāng)我們處理完了外設(shè)芯片的中斷時(shí),我們也需要清除處理器上的標(biāo)識(shí),從而為下一次中斷做準(zhǔn)備。需要注意的是,清外設(shè)的中斷必須發(fā)生在請(qǐng)?zhí)幚砥髦袛鄻?biāo)識(shí)之前!

中斷還存在一個(gè)觸發(fā)方式問(wèn)題。有兩種觸發(fā)方式 ,一種是電平觸發(fā),另一種是沿觸發(fā)。電平觸發(fā)是指電平的高低表示外設(shè)是否有中斷,而沿觸發(fā)則是能過(guò)中斷線上的電平的升或降來(lái)表示的,顯然,存在兩種沿觸發(fā)方式。一種是中斷線從低電平變?yōu)楦唠娖剑覀兎Q之為上升沿觸發(fā),另一處是中斷線從高電平轉(zhuǎn)換為低電平,我們稱之為下降沿觸發(fā)。總的來(lái)說(shuō)中斷的觸發(fā)方式有電平觸發(fā)、上升沿觸發(fā)和下降沿觸發(fā)。電平觸發(fā)方式中處理中中斷設(shè)置很重要的一個(gè)步驟。

萬(wàn)用表通常是用來(lái)查看電平的高低、電阻的大小等的,是常用且必不可少的工具之一。在嵌入式系統(tǒng)開(kāi)發(fā)中,我們常用的是數(shù)字萬(wàn)用表。

電平(Level)

在數(shù)字電路中,分為高電平和低電平,分別用1和0表示。一個(gè)數(shù)字電路的管腳,總是存在一個(gè)電平的,要么高要么低,或者說(shuō)要么1要到0(其實(shí),還有另一種狀態(tài))。

在嵌入式系統(tǒng)開(kāi)發(fā)中,我們不可避免的要與外設(shè)芯片打交道。調(diào)試驅(qū)動(dòng)程序時(shí),除了需要完全看明白芯片的數(shù)據(jù)手冊(cè),且在軟件高度的過(guò)程中,還需要看我們所期望的信號(hào)電平是否發(fā)生在芯片上。比如,我們?cè)趯?xiě)驅(qū)動(dòng)程序時(shí),需要通過(guò)寫(xiě)I/O端口來(lái)對(duì)外設(shè)芯片進(jìn)行操作,當(dāng)寫(xiě)相應(yīng)的I/O端口時(shí),我們知道所對(duì)應(yīng)芯片的片選信號(hào)應(yīng)當(dāng)有效,有時(shí),我們需要驗(yàn)證是否按預(yù)期發(fā)生了,這就需要用到示波器。一般的示波器是能同時(shí)觀測(cè)兩個(gè)信號(hào)線的信號(hào)狀態(tài)的。示波器都提供一定的功能,比如設(shè)置信號(hào)撲捉的方式等等。示波器很重要的一個(gè)參數(shù)據(jù)是其采集頻率,根據(jù)Nyquist采集定理,如果我們想用示波器查看頻率是100M赫茲的信號(hào),那么其采樣頻率必須至少是其兩倍,即200M赫茲。有人可能會(huì)問(wèn):為什么不用萬(wàn)用表來(lái)看呢?因?yàn)槿f(wàn)用表的采集頻率很底,無(wú)法采集到很快的信號(hào)變化。

邏輯分析儀

簡(jiǎn)單的說(shuō)邏輯分析器就是具有很多信號(hào)通道的示波器。通過(guò)邏輯分析儀,我們可以看到地址總線和數(shù)據(jù)總線上的數(shù)據(jù)。邏輯分析儀都提供一定的編程能力,用于編程什么時(shí)候開(kāi)始對(duì)總線上的數(shù)據(jù)進(jìn)行采集。

-

寄存器

+關(guān)注

關(guān)注

31文章

5361瀏覽量

120877 -

cpu

+關(guān)注

關(guān)注

68文章

10898瀏覽量

212535 -

Linux

+關(guān)注

關(guān)注

87文章

11333瀏覽量

210054

原文標(biāo)題:要想弄懂Linux內(nèi)核的工作原理,就必須懂點(diǎn)基本的硬件知識(shí)

文章出處:【微信號(hào):gh_c472c2199c88,微信公眾號(hào):嵌入式微處理器】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于80X86系列嵌入式的GPRS應(yīng)用是什么

80X86微處理器

80X86CPU

80X86微機(jī)原理及接口技術(shù)實(shí)驗(yàn)教程(2012版)

80x86指令系統(tǒng)的指令大全詳細(xì)資料說(shuō)明

X86匯編語(yǔ)言從實(shí)模式到保護(hù)模式PDF電子書(shū)免費(fèi)下載

80X86微機(jī)原理及接口技術(shù)和實(shí)驗(yàn)教程詳細(xì)資料說(shuō)明

通過(guò)了解寄存器的功能與作用去揭秘CPU核心技術(shù)

CPU的工作模式

45個(gè)寄存器、CPU核心技術(shù)大揭秘(下)

Intel 80x86系列CPU保護(hù)模式下最核心的部件中幾個(gè)寄存器的作用

Intel 80x86系列CPU保護(hù)模式下最核心的部件中幾個(gè)寄存器的作用

評(píng)論