在本文中,我們不涉及關于EMC的設計建議。然而,在組件水平上,所使用的技術所固有的“鎖存”現象是唯一考慮的因素。

CMOS結構封裝括一個PNPN可控硅類型單元,由VDD和VSS之間的寄生晶體管產生。當寄生可控硅被擾動激活,導致了μC的電源短路,并導致內部結構的破壞時,就會出現一種延遲現象。以下的條件可能會導致“鎖存”:

ü輸入/輸出電壓的電壓高于VDD或低于VSS的電壓。

ü電源電壓VDD比VDDMax高

ü電源VDD急劇變化。

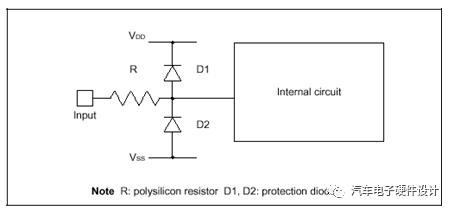

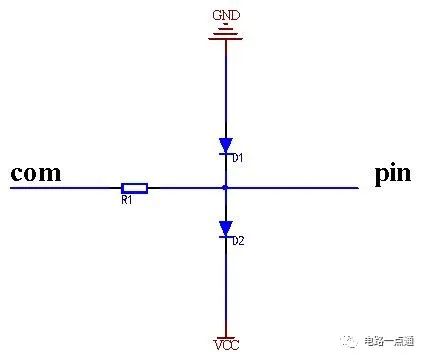

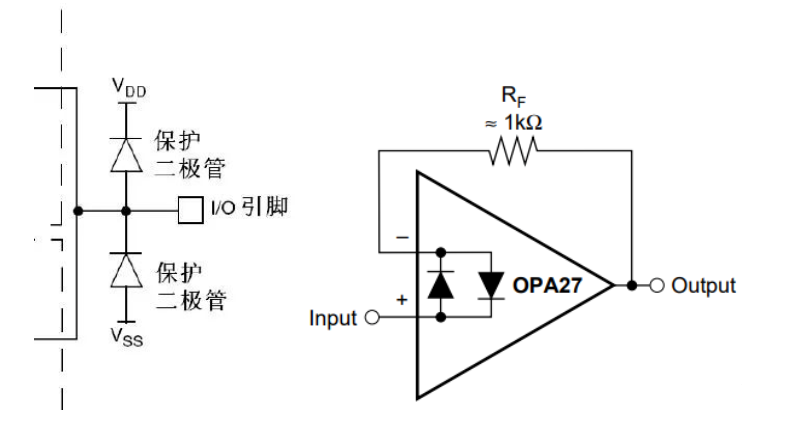

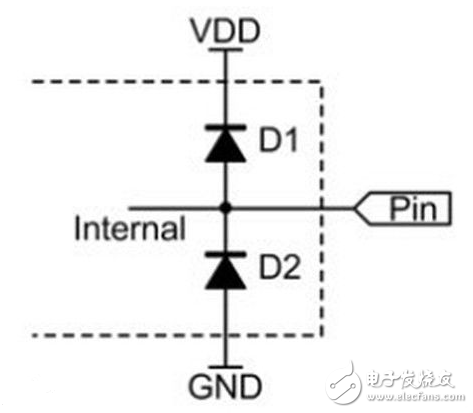

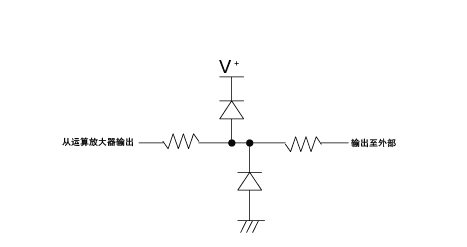

μC有對靜電保護,輸入是在內部配置保護網絡,通過對VDD和VSS并聯鉗位二極管和串聯電阻進行保護。

然而,這種內部保護電路必須在設計層面上的預防措施來完成。建議:

ü保持μC在其額定范圍內的電源電壓。

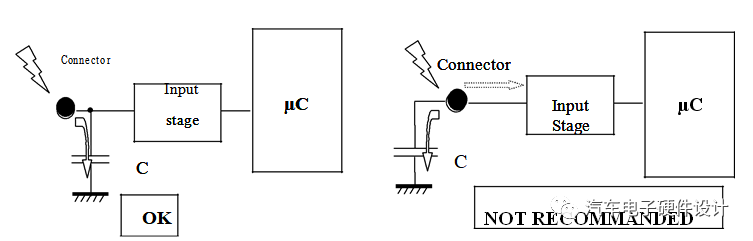

ü在連接器的引腳上直接放置一個靜電電容,以得到保護。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

CMOS

+關注

關注

58文章

5729瀏覽量

235779 -

二極管

+關注

關注

147文章

9676瀏覽量

167007 -

emc

+關注

關注

170文章

3944瀏覽量

183469

原文標題:MCU健壯性設計之EMC / ESD的要求

文章出處:【微信號:QCDZYJ,微信公眾號:汽車電子工程知識體系】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

二極管鉗位保護電路講解

二極管,作為一個基本的電子元器件,在許多電子電路系統項目中均有所應用;然而通過芯片哥拜訪的許多硬件開發工程師,發現一些二極管常用的經典電路還有不被熟悉,不被使用;因此芯片哥就和小伙伴們一起研究下一個被工程師忽視的二極管

發表于 07-10 09:29

?1876次閱讀

鉗位二極管保護電路圖 TVS鉗位二極管保護原理詳解

鉗位二極管其實就是TVS 管,也就是瞬態抑制二極管的簡稱(Transient Voltage Suppressor)。它是在穩壓

發表于 08-18 09:06

?5425次閱讀

TVS鉗位二極管鉗位保護原理與ESD防護介紹

數量級、漏電流小、瞬態功率大、無噪聲等特點,因此在信號系統內得到廣泛的應用及認可。 下面來先了解一下兩個二極管反向串聯時候是怎工作的,如下圖D1和D2兩個二極管反向串聯在一起,這屬于

發表于 02-28 13:47

肖特基二極管的作用和工作原理 肖特基二極管串聯和并聯作用

肖特基二極管的作用和工作原理 肖特基二極管串聯和并聯作用? 肖特基二極管是一種重要的半導體器件,它和普通的硅

VDD和VSS并聯鉗位二極管和串聯電阻進行保護

VDD和VSS并聯鉗位二極管和串聯電阻進行保護

評論