在嵌入式系統研發領域,隨著產品AI化升級進程,原先設計常規數字系統的FPGA硬件工程師和系統軟件設計師們都不得不面臨技術轉型的問題。那么在AI時代, FPGA廠家與傳統的數字系統軟硬件工程師們該如何轉型,才能更好地順應市場的需求?

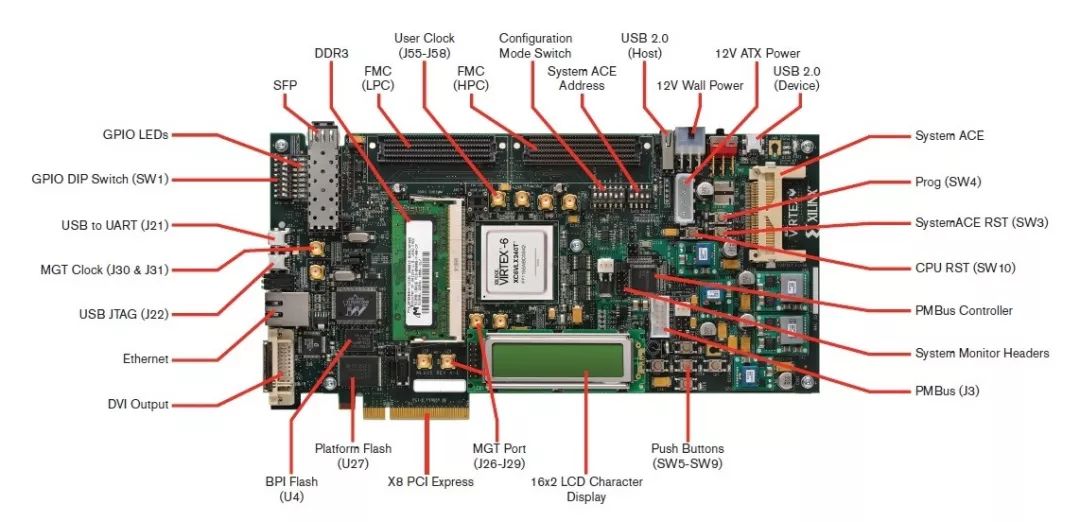

FPGA自誕生起一直在高速復雜計算領域里占有極大的優勢,借助于計算機輔助設計工具通過Verilog編程,設計者可以很方便地將一個通用結構的FPGA芯片構造成一個規模宏大的并行的計算結構,這個結構能以通用CPU無法比擬的高速進行極其復雜的數據處理。在有實用價值的圖像分析、語音理解等模式識別的處理計算中,通常需要在幾個毫秒之內對一幅圖像的所有像素逐點進行卷積計算,分析、比較計算結果,得到可靠的結論。算法研究工作者通常用普通計算機的軟件來處理靜態數據,得到理論結果,但實際應用中如此慢的響應速度根本無法滿足實際工程的需求。最近二十多年來,圖像分析、語音理解等模式識別研究的算法理論研究已逐步成熟,引起了工業界的興趣,大量的研究經費轉向如何設計可以高速進行復雜數據處理的并行計算機結構,并研發實用的AI系統。因此近二十多年來,FPGA芯片和Verilog設計/驗證方法得到了飛速的發展。

在圖像處理方面,如人臉識別、指紋識別、語音識別方面的機器人,其AI表現也十分搶眼。 在這一類機器人的計算系統中許多極其復雜的計算工作,絕大部分都是由FPGA結構實現的。而且FPGA可以與各種不同的存儲器、各種不同類型的并行接口或是計算機接口,如PCIe等方便地連接,它也可以把機器人與計算機網絡和廣大的知識庫融為一體,構成極其龐大、響應迅速的AI知識系統。

根我所知,許多AI研究工作者習慣于用軟件進行算法研究,他們中的大多數人用靜態的圖像或靜態的聲音(錄下來的聲音)做語音理解或者翻譯方面的工作。在整個過程中,雖然數據處理的計算速度比較慢,但還是可以得到可靠的分析處理結果。但是在實際工程應用當中,這樣慢的處理速度顯然沒有多大實用價值,因為在許多場合,響應根本無法用于實際場合。隨著研究工作向設計實際系統轉換,我建議軟件系統的工程師們應該學會如何使用FPGA,以及如何用FPGA做復雜計算的加速。其實對計算機科學和工程專業畢業的軟件工程師而言,只要有數字電路的基礎知識,學習Verilog HDL語言并不困難,學會RTL級別Verilog的編程來構造可綜合的并行迭代計算結構并不困難,只需要花費一兩個月就能上手。

而對于那些在嵌入式系統工作多年的硬件工程師或只有一些簡單接口設計經驗的FPGA工程師而言,雖然不是一個專職研究處理算法的軟件編程專家,但他們必須抽一些時間來理解算法,幫助算法工程師把電路結構改變得更加合理,令計算瓶頸變成寬敞的通道。在AI時代,特別是AI進入應用的新時代,一個真正的硬件工程師不僅應該熟練掌握Verilog的語言,學會如何用Verilog語言編寫可綜合的并行結構,在規定的時間間隔內完成算法要求的計算工作量,并且學會如何設計硬件,讓硬件與算法軟件配合,更有效率地完成算法要求的多種計算任務。把原來算法研究中完全用軟件實現的計算過程,變成用軟件和硬件配合實現的過程,把整個計算結構改造成一個可配置的高速處理的結構,專門針對某一領域的人工智能產品,讓這個硬件有更大的市場,這是非常有意義的!

總而言之,對今天的AI嵌入式系統的設計師而言,必須軟硬兼備才能成為一個優秀的工程師。換言之,軟件人員要往硬件方向轉,學習硬件知識,硬件工程師也必須向軟件工程師靠攏,理解算法的執行過程,為AI算法設計新的計算結構和數據通路。這是因為現在AI的軟件編程并不是簡單地編寫一個程序得到一個計算結果,還必須考慮計算的速度是不是足夠夠快。所以實質上是一個如何設計合理的并行結構計算加速核心硬件,以達到實時全面完成算法要求的問題。

轉型勢在必行,FPGA工程師要理解新任務、掌握新工具

深維科技 CEO 樊平

對FPGA產品的需求:

1.硬件性能的提升:盡管FPGA在數據中心應用處于一個快速增長過程,但總體規模還不是很大,這里面有一些限制,也是FPGA廠商需要努力提升的地方。 首先是價格問題,FPGA的大規模部署需要FPGA硬件成本盡快降下來,這個要靠工藝進步以及市場規模來解決;其次是存儲訪問帶寬,HBM技術以及CCIX是代表性的方向。

2.軟件工具的提升:FPGA需要軟件工具來輔助工程師完成設計過程,在新的應用領域對設計的內容、流程、驗證方法等都提出了新的需求,例如AI應用客戶希望具備高層次的模型定制能力,但是目前還沒有廠商可以提供成熟的方案。這也為新的工具提供商提供了機會。

3.生態系統:GPU獲得了廣泛的認同和應用,這與CUDA長期的演進和積累密不可分。新興應用領域大都有流行的設計框架和開源項目。FPGA一般作為高性能計算硬件來加速現有項目,所以需要和這類設計框架進行融合,也需要大量基礎庫/IP來支持用戶快速完成設計。所以一個成熟的生態系統至關重要,目前這塊也還是非常薄弱。

對FPGA工程師的需求:

1.理解新任務:傳統FPGA工程師面對的是硬件的設計問題,但AI等應用與應用系統關系密切,不單純是FPGA片上邏輯設計的問題。工程師往往需要了解上層軟件如何與FPGA片上系統的集成與優化問題。

2.掌握新工具:FPGA主流廠商很早就開始布局新興市場的應用,一個主要工作就是提升FPGA設計開發抽象層次,OpenCL/HLS語言就是典型代表,一般情況下可以提升數倍開發效率。所以FPGA工程師需要充分掌握這類新的工具,以保障自己能有足夠的效率面對行業需求。

3.抓住新機遇:新興應用領域不僅僅是FPGA市場的簡單擴充,它也為FPGA應用帶來新的商業模式,以FaaS為代表的應用形式,為FPGA開發人員帶來眾多新的商業機遇。

Achronix的Speedcore IP具有支持先進人工智能技術的正確功能組合

Achronix 半導體公司市場營銷副總裁 Steve Mensor

人工智能(AI)應用要求高性能,并且在許多情況下,低延遲能夠成功地響應條件和需求的實時變化。它們還要求功耗盡可能的低從而意味著無法使用,其解決方案是將機器學習放在供電和制冷能力充足的云服務器端。對這些嵌入式系統的進一步要求是,即使在沒有網絡連接到云端的情況下也都能隨時工作并且準備好做出響應。這些因素的組合要求在硬件設計方法上做出改變。

人工智能要求謹慎地平衡數據通路的性能、內存延遲和吞吐量,這就需要用一種方法來將盡可能多的功能放到專用集成電路(ASIC)或系統級芯片(SoC)上。過添加eFPGA技術,則提供了市場需要的一種解決方案,來將靈活性以及客制化邏輯單元支持能力結合在一起。

作為專為嵌入到SoC和ASIC之中而設計的硅知識產權(IP),Achronix的Speedcore eFPGA IP是一種高度靈活的解決方案,它支持高性能機器學習應用中需要的數據吞吐量。通過借助其可切分的架構,Speedcore IP為設計人員提供了滿足其應用要求的能力來實現eFPGA功能的混合和匹配。Speedcore IP的核心功能包括基于四輸入查找表(LUT)的邏輯單元、用于寄存器文件和類似應用并面向邏輯單元的小型存儲器(LRAM)、較大的單元塊存儲器(BRAM)和可配置的數字信號處理器(DSP)模塊。根據應用的要求,Speedcore基于縱列的架構可提供準確混合資源的能力。

FPGA工程師要這樣擁抱AI

資深嵌入式軟件工程師 楊鑫

FPGA本身作為一種可編程的邏輯器件,其最突出的特性在于可編程的邏輯部分,這與傳統CPU的順序執行方式有著本質區別,與ASIC相比又有著較好的靈活性,在AI產業興起之前,就一直是ASIC設計的前期驗證手段。但現在FPGA器件的發展已經跨越了可編程這個特性,現在的FPGA器件往往擁有遠比通用芯片更高的I/O帶寬和內存帶寬例如高達40Gbps的serdes接口,以及HBM2等超高速內存接口,這些接口使得FPGA在通信領域有著非常廣泛的應用。

現如今,由于很多AI產品對內存帶寬和互聯互通性有著相當高的要求,在較輕運算量的情況下,FPGA的可應用場景有了非常大的突破,所以很多小批量、快迭代的產品,其最佳開發方式反而變成了FPGA,而非ASIC或者GPU等等,因此FPGA開發人員,只要多熟悉AI技術、熟悉AI應用需求,仍然可以在AI行業游刃有余,不斷打造新的傳奇。

現在的圖像處理和數據的傳輸、分配這些事情在人工智能開發方面發揮著重要作用,在AI時代需要FPGA工程師尤其是做軟件算法和做硬件設計的人要優勢互補。

產品設計好后還要與原來的計算機與服務器連接在一塊兒,那么還需要做系統級設計。這對FPGA的軟件工程師、硬件工程師都是一個新的挑戰。希望FPGA工程師們成功轉型,為AI時代能設計出更好的產品助力。

-

FPGA

+關注

關注

1629文章

21758瀏覽量

604240 -

AI

+關注

關注

87文章

31111瀏覽量

269435

原文標題:AI時代FPGA廠商與FPGA工程師該如何轉型?

文章出處:【微信號:mcuworld,微信公眾號:嵌入式資訊精選】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

工業 4G?路由器賦能遠程醫療,守護生命線

連接器:工廠中的生命線,默默無聞的紐帶

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog vhdl fpga

AI for Science:人工智能驅動科學創新》第4章-AI與生命科學讀后感

城市生命線守護者 確保16萬戶家庭用水安全,打造穩定供水網

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區別?

一網統管政企聯動:計訊構建城市生命線安全智能體的應急管理革新

【招聘】verilog vhdl FPGA

水電氣安全監測解決方案|守護城市生命線

筑牢城市生命線,漫途綜合管理平臺全面護航

筑牢城市生命線,綜合管理平臺全面護航

掌握 Verilog FPGA設計和驗證方法是AI時代系統設計師的生命線

掌握 Verilog FPGA設計和驗證方法是AI時代系統設計師的生命線

評論