用SPICE仿真高精度數模轉換器

在這篇文章中,我們將重點講述系統性能預測及如何避免設計失敗。可立即映入小編腦海中能避免這些失敗的術語就是“仿真”。當前,除了數模轉換器(DAC)之外,用戶可以在SPICE仿真工具中建模并仿真模擬信號鏈組件中的絕大多數組件。借助于針對高精度DAC的SPICE模型,在實現實際硬件前,電路板工程師不再需要完全依賴于手算結果。

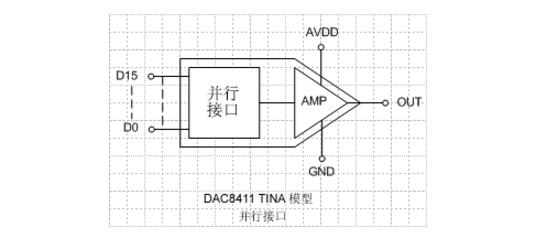

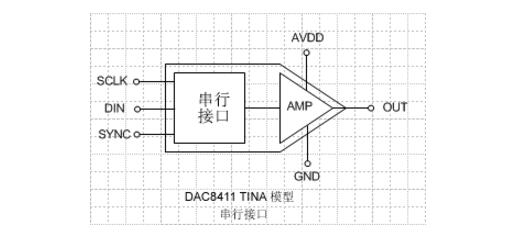

我們可提供兩款不同的SPICE模型。其中的一個使用簡單的n位寬并行接口,如圖1中所示,此模型與所有TINA-TI版本器件兼容。而另外一款模型使用一個串行SPI接口,如圖2中所示,他與工業用TINA-TI器件兼容。兩款不同的模型包括針對DAC和輸出放大器的重要直流特性,諸如偏移誤差、增益誤差、輸出電壓到電源軌擺幅、溫度漂移和靜態電流。其他交流參數特性包括轉換速率、穩定時間、加電毛刺脈沖和穩定性。SPI接口模型還完全復制了數字接口,并且可被用來仿真到DAC輸入的數字信號鏈。

圖1–DAC8411模型(并行)

圖2–DAC8411模型(串行)

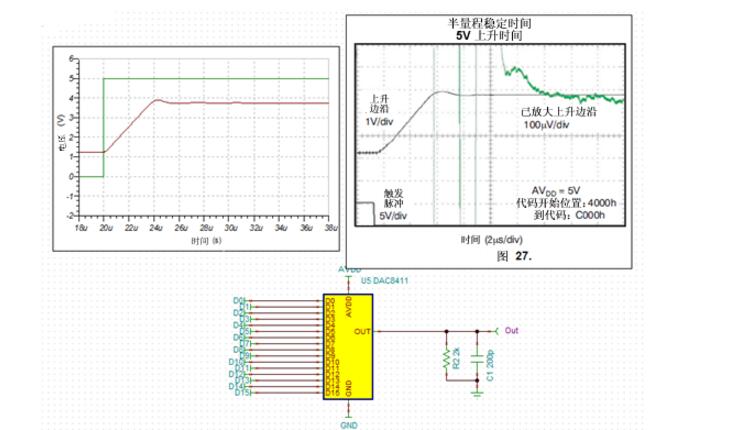

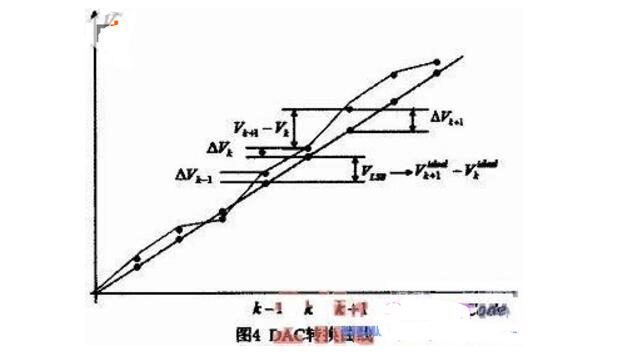

預測和推斷DAC或運算放大器在驅動特定負載時的運行方式是所有設計的一個重要方面。我們來看一個示例,在這個示例中我們用DAC8411SPICE模型來模擬穩定時間。

圖3左側顯示DAC輸出的瞬態仿真,代碼步長從?滿量程到?滿量程。在這個仿真中,DAC正在驅動一個與200pF電容器并聯的2kΩ電阻負載-同樣的負載被用來指定數據表中的穩定時間。SPICE模型準確地復制了圖3右側顯示的數據表中的典型特性曲線的穩定時間。

圖3–DAC8411瞬態仿真

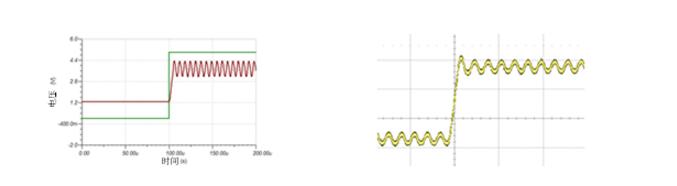

但是,如果你驅動的負載與數據表中指定的負載不同的話該怎么辦呢?圖4左側顯示了一個仿真。在這個仿真中,DAC輸出上被施加了一個更大的值為20nF電容負載。在這個情況下,瞬態仿真顯示出在DAC輸出上有相當大的振鈴,或者說是振蕩,其原因是輸出放大器在其上有較大電容負載時所表現出的不穩定性。所提供的完整SPICE模型有助于較早地捕捉到此類問題,這樣的話,在首次原型機設計時就可以將補償組件包含在內。

圖4–DAC841120nF電容負載時的瞬態仿真

總的來說,針對高精度DAC的最新SPICE模型主要是為工程師和設計人員提供一個獨特的方法來仿真整個模擬信號鏈,盡早發現問題并且縮短上市時間。下面的兩個TI高精度設計可以使你動態地了解全新的DACSPICE模型:

1、TIPD158-低成本回路供電4-20mA發射器電磁兼容性/電磁干擾(EMC/EMI)性能已經測試

2、TIPD160-基于數字可調倍乘數模轉換器(MDAC)的狀態可變濾波器

高精度數模轉換器(DAC)測試靜態測試方法研究

1、基于過零檢測的DAC靜態測試

1.1低精度ADC不能直接用來測試高精度DAC的原因

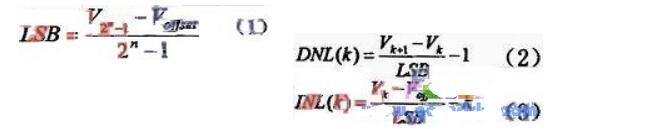

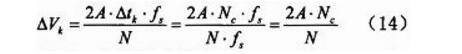

對于DAC的靜態測試,通常測試DNL、INL這兩個參數值,方法是輸入代碼k,k=0,1,2…2n-1。得到DAC輸出的電平值Vk。計算DNL、INL的公式如下:

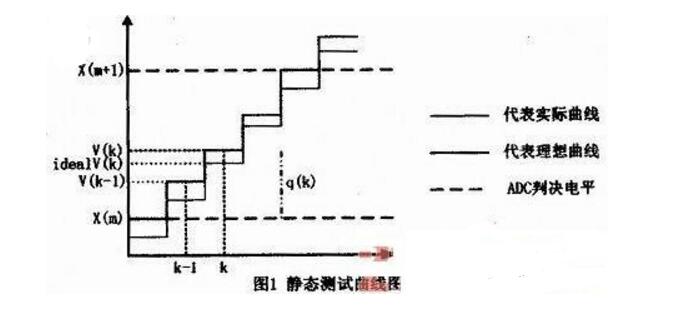

假如用精度低于DAC的ADC對其直接測試,如圖1所示,由于低精度ADC引入的量化誤差q(k),我們無法分辨輸入代碼k和k-1對應的確切電壓值。這種情況下的靜態參數測試就失去了意義。

1.2過零檢測

過零點檢測法是一種經典的調制域分析方法,它通過記錄過零點的時間得到過零點的時間間隔,可以用于識別精度低于ADC步長的微弱信號。圖2簡要地描述了測試系統框圖:待測DAC輸出的電壓Vk,校準儀提供一個標準的參考正弦波f(t)=Asin(ωt+φ),將直流電壓Vk加在參考正弦波上,將結果信號輸入高速ADC。即:

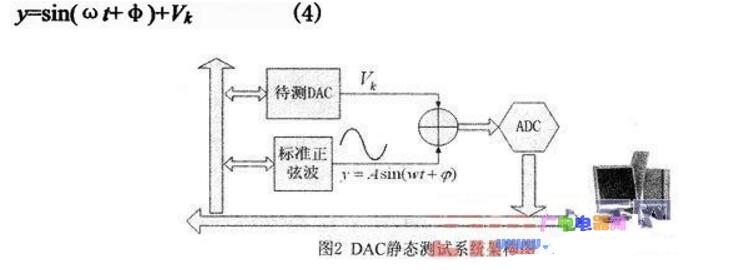

式(4)在時域圖上的表現如圖3所示。

圖中,虛線表示標準參考信號f(t)=Asin(ωt+φ),實線為疊加之后的信號,可以看出,tk1、tk2、tk3時刻為過零點,Vk的大小由△tk決定。△tk的值可以通過測量過零點tk1、tk2、tk3得到,Vk的表達式可以推導如下:

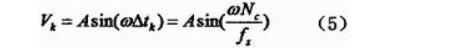

其中,Nc為在時間間隔△tk內的采樣點數,fs為設置的ADC的采樣率。

1.3測試方法的弊端

利用以上方法,可以得到DAC輸出電壓的值Vk,進而求出靜態參數DNL、INL的大小。需要關注的是:為了得到過零點序列,參考正弦波的幅值A必須大于DAC的滿量程電壓范圍;同樣由式(5)得到ADC的最低采樣率:

△V幅值分辨率,通過式(6)可以看出:為了確保測試的準確性,△V應該盡可能地小,并且在其他條件不變的情況下Nc的值越大越好。因為這種方法的本質在于將幅度上的高精度測試轉移到時間上來。因此采樣率越高,測量結果越準確,但是采樣率與測試設備息息相關,不可能無限制提高。這種情況下,如果沒有設備能夠提供足夠高的采樣率,那么只能降低信號頻率f。但是降低信號頻率f將帶來另一個問題,就是測試時間的成倍增加。

在文獻中作者曾對16位且幅值為±10V的DAC進行了實測,采用泰克TDS7404B數字示波器作為采集信號用的ADC。其主要參數為:8位分辨率、20GS/s的最高采樣率。設置△V=LSB/40,Nc=5,正弦波頻率f=100Hz,幅值A=11V。通過式(6)得到的采樣率高達5GS/s。每次測10個Vk對其做平均,這樣每測一個Vk花費的時間是0.1s,即便擁有這樣的超高采樣率的設備,完整地測一個16位的DAC所需要的時間也至少需要兩個小時。

2、提出的方法

從降低測試時間的角度考慮:首先,從圖3中可以看到,利用正弦波作為參考波形至少需要3個過零點才能得到DAC的輸出電壓值,其次,為了降低檢測每個過零點所需要的時間,最直接的方法就是提高參考信號的頻率f,但是由于設備條件的限制,采樣率fs不能再提高。從式(6)中可以看出,Nc、△V都是約定值,不可變動,唯一能改變的就是參考正弦波幅值A,但A的最小值也受到限制,因為一旦A小于被測DAC的量程范圍,DAC中大于A的輸出電壓將無法測得。實際上,A的限制是因為我們需要測試每一個代碼對應的輸出電壓值。

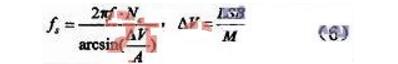

但事實上,我們并不需要測試每一個Vk。對靜態測試而言,主要是了解被測DAC的線性度,如圖4所示。影響DNL的主要是相鄰兩個輸入代碼的輸出電平幅值之差與理想步長之間的偏差,即Vk+1-Vk與LSB之差。將DNL、INL的計算公式適當變化如下:

由圖4和式(7)、(9)可以看出,只要知道輸入代碼的實際電壓與理想電壓的差值,一樣能計算出DAC的靜態參數。

基于以上認識,設計了如下的測試系統架構模型。

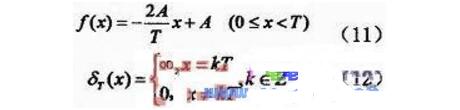

設參考鋸齒波的信號 ,其中:

,其中:

參考斜坡的信號可以表示為: , []為取整函數。

, []為取整函數。

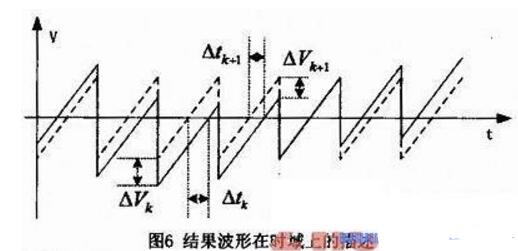

令DUT產生的信號為g‘(x),經過疊加的均勻抖動上升的鋸齒信號為f(x)*δT(x)+g(x),ADC采集的信號就是f(x)*δT(x)+g(x)-g’(x)。顯然,g(x)-g‘(x)的值代表了△Vk的大小,而△Vk很小,低精度的ADC是無法將其反映出來的。通過借助參考鋸齒波形在時域上的過零點分布卻能夠表達出來。

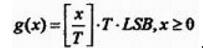

如果被測DAC表現出完美的靜態特性,那么ADC會恢復出參考鋸齒波信號,如果一旦被測DAC的輸出電壓Vk與理想值存在偏差(如圖4),則會在時域圖上明顯地反映出來,如圖6所示。

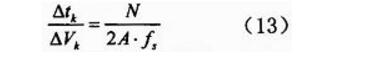

圖中△Vk代表了在輸入代碼為k時,實際測量電平與這一點的理想電平的差值,虛線代表參考鋸齒波信號,實線表示被測DAC與參考信號的差分信號。用一個雙通道的ADC同時對兩種信號進行采集,通過檢測過零點,得到△tk、△tk+1的值,不難看出:

N代表鋸齒波一個周期內的采樣點,A表示鋸齒波的幅值,然后有:

結果證明,在上述方法中,知道鋸齒波的幅值以及△tk內的采樣點數Nc,便可得到△tk的值,在這種方法中,并不需要知道每一個Vk的值,也可以輕松地獲得DNL和INL的值。

3、仿真實驗

為了驗證此方法的可靠性,本文采用Labview虛擬儀器進行仿真測試。仿真中采用8位DAC產生標準的斜坡波形和鋸齒波形,將兩種信號的加法形式作為參考波形,設置隨機白噪聲點逐點加到標準斜坡波形上,使得LSB的范圍限制為,以便用程序計算出實際仿真的DNL和INL的大小。程序的最終目的在于,將提出方法測試所得的結果和真實計算結果的偏差做一個比較。

通過編寫測試程序,可以得到以下規律:

(1)ADC的采樣率越高,實際測試得到的DNL和INL會更加接近真實的計算結果;

(2)參考鋸齒波的幅值越小,測試的結果會越精確;

(3)ADC位數與測試精度幾乎沒有關系。

需要注意的是,增加采樣點數會使測試時間增加,因此ADC的采樣率不可以無限制提高,但是可以根據測試的實際情況對其作最佳評估。關于幅值的設定,其最低值必須使得每個差分鋸齒波都有過零點。然后設置程序來比較標準鋸齒波的過零點和差分鋸齒波的過零點數,當兩者不同時,程序中的指示燈報警。

在仿真測試中,設置DAC范圍為10V,幅值為80mV;產生的斜坡中,每個輸入代碼重復100次,設置采樣率為1k,采集256000個點。設置ADC的分辨率為2位。得到結果如圖6所示。

通過比較圖6中兩個波形的過零點之間的采樣數,比較最終得到的INL值與計算所得INL值:圖7a.實際的INL值,b.用本方法測得的INL值。

4、結束語

本文對高精度DAC的動態測試提出了新的評估方法,這個方法通過比較參考鋸齒波與實際得到的鋸齒波在時域上的過零點,精確地獲得了DAC的靜態參數INT、DNL的值。并且在Labview仿真測試系統中進行了驗證,結果證明了此方法的有效性和實用性。

-

SPICE

+關注

關注

6文章

182瀏覽量

42580 -

數模轉換器

+關注

關注

14文章

1013瀏覽量

83188 -

DAC8411

+關注

關注

1文章

4瀏覽量

8756

發布評論請先 登錄

相關推薦

一種典型的高精度數模轉換器方案

LTC2757:高精度數模轉換器設計方案

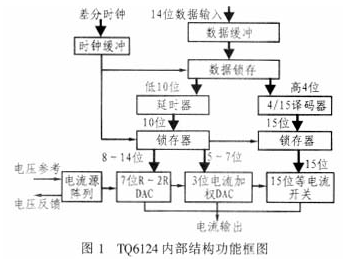

高精度數模轉換器TQ6124芯片的性能特點、結構與應用分析

數模轉換器AD5542技術介紹

用SPICE仿真高精度數模轉換器

數模轉換器的高精度

ADI推出AD5791高精度20位數模轉換器

高速高精度數模轉換器AD7671結構及原理

如何用SPICE來仿真高精度數模轉換器?

如何用SPICE來仿真高精度數模轉換器?

評論