和很多的串行傳輸協(xié)議一樣,一個(gè)完整的PCIe體系結(jié)構(gòu)包括應(yīng)用層、事務(wù)層(Transaction Layer)、數(shù)據(jù)鏈路層(Data Link Layer)和物理層(Physical Layer)。其中,應(yīng)用層并不是PCIe Spec所規(guī)定的內(nèi)容,完全由用戶根據(jù)自己的需求進(jìn)行設(shè)計(jì),另外三層都是PCIe Spec明確規(guī)范的,并要求設(shè)計(jì)者嚴(yán)格遵循的。

一個(gè)簡(jiǎn)化的PCIe總線體系結(jié)構(gòu)如上圖所示,其中Device Core and interface to Transaction Layer就是我們常說(shuō)的應(yīng)用層或者軟件層。這一層決定了PCIe設(shè)備的類型和基礎(chǔ)功能,可以由硬件(如FPGA)或者軟硬件協(xié)同實(shí)現(xiàn)。如果該設(shè)備為Endpoint,則其最多可擁有8項(xiàng)功能(Function),且每項(xiàng)功能都有一個(gè)對(duì)應(yīng)的配置空間(Configuration Space)。如果該設(shè)備為Switch,則應(yīng)用層需要實(shí)現(xiàn)包路由(Packet Routing)等相關(guān)邏輯。如果該設(shè)備為Root,則應(yīng)用層需要實(shí)現(xiàn)虛擬的PCIe總線0(Virtual PCIe Bus 0),并代表整個(gè)PCIe總線系統(tǒng)與CPU通信。

事務(wù)層(Transaction Layer):接收端的事務(wù)層負(fù)責(zé)事務(wù)層包(Transaction Layer Packet,TLP)的解碼與校檢,發(fā)送端的事務(wù)層負(fù)責(zé)TLP的創(chuàng)建。此外,事務(wù)層還有QoS(Quality of Service)和流量控制(Flow Control)以及Transaction Ordering等功能。

數(shù)據(jù)鏈路層(Data Link Layer):數(shù)據(jù)鏈路層負(fù)責(zé)數(shù)據(jù)鏈路層包(Data Link Layer Packet,DLLP)的創(chuàng)建,解碼和校檢。同時(shí),本層還實(shí)現(xiàn)了Ack/Nak的應(yīng)答機(jī)制。

物理層(Physical Layer):物理層負(fù)責(zé)Ordered-Set Packet的創(chuàng)建于解碼。同時(shí)負(fù)責(zé)發(fā)送與接收所有類型的包(TLPs、DLLPs和Ordered-Sets)。當(dāng)前在發(fā)送之前,還需要對(duì)包進(jìn)行一些列的處理,如Byte Striping、Scramble(擾碼)和Encoder(8b/10b for Gen1&Gen2, 128b/130b for Gen3& Gen4)。對(duì)應(yīng)的,在接收端就需要進(jìn)行相反的處理。此外,物理層還實(shí)現(xiàn)了鏈路訓(xùn)練(Link Training)和鏈路初始化(Link Initialization)的功能,這一般是通過(guò)鏈路訓(xùn)練狀態(tài)機(jī)(Link Training and Status State Machine,LTSSM)來(lái)完成的。

需要注意的是,在PCIe體系結(jié)構(gòu)中,事務(wù)層,數(shù)據(jù)鏈路層和物理層存在于每一個(gè)端口(Port)中,也就是說(shuō)Switch中必然存在一個(gè)以上的這樣的結(jié)構(gòu)(包括事務(wù)層,數(shù)據(jù)鏈路層和物理層的)。一個(gè)簡(jiǎn)化的模型如下圖所示:

關(guān)于事務(wù)層,數(shù)據(jù)鏈路層和物理層的詳細(xì)的功能圖標(biāo)如下圖所示:

-

總線

+關(guān)注

關(guān)注

10文章

2914瀏覽量

88713 -

PCIe

+關(guān)注

關(guān)注

15文章

1285瀏覽量

83724 -

數(shù)據(jù)鏈路層

+關(guān)注

關(guān)注

0文章

60瀏覽量

12060

原文標(biāo)題:【博文連載】PCIe掃盲——PCIe總線體系結(jié)構(gòu)入門

文章出處:【微信號(hào):ChinaAET,微信公眾號(hào):電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

無(wú)線傳感器網(wǎng)絡(luò)的體系結(jié)構(gòu)分析

DDR總線的體系結(jié)構(gòu)

淺析PCI體系結(jié)構(gòu)

嵌入式微處理器體系結(jié)構(gòu)

Microarchitecture指令集體系結(jié)構(gòu)

了解體系結(jié)構(gòu) - 介紹 Arm 體系結(jié)構(gòu)

Arm的DRTM體系結(jié)構(gòu)規(guī)范

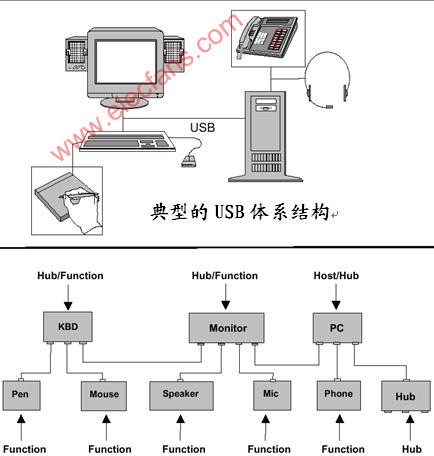

USB體系結(jié)構(gòu)概述

LTE體系結(jié)構(gòu)

網(wǎng)絡(luò)體系結(jié)構(gòu),什么是網(wǎng)絡(luò)體系結(jié)構(gòu)

ARM體系結(jié)構(gòu)與程序設(shè)計(jì)

軟件體系結(jié)構(gòu)的分析

Oracle體系結(jié)構(gòu)講解

一個(gè)簡(jiǎn)化的PCIe總線體系結(jié)構(gòu)

一個(gè)簡(jiǎn)化的PCIe總線體系結(jié)構(gòu)

評(píng)論