商用現貨型FPGA被認為是解決目前空間應用對處理能力需求不斷增加的唯一途徑,由于其對多比特翻轉的敏感性,需要針對空間應用的單粒子效應采取專門的設計加固技術。提出了基于用戶邏輯層、配置存儲器層和控制層3個層級的容錯技術框架。在用戶邏輯層,提出了一種新型的低開銷的FTR策略用于用戶邏輯的錯誤檢測;在配置存儲器級,提出了基于模塊和幀的動態部分可重構策略用于處理配置存儲器的錯誤;在控制級,以Xilinx ZYNQ片上系統型FPGA為目標,利用其嵌入的硬核處理器進行基于檢查點和卷回體制的電路狀態保存和恢復。整個容錯技術框架在7級流水的LEON3開源器處理器中進行了故障注入的試驗驗證,試驗結果顯示在增加85%的LUT資源和125%的觸發器資源使用條件下,99.997%注入的故障得到了及時糾正。

0 引言

商用芯片擁有比宇航級芯片更強的處理能力,但是容易受到單粒子效應的影響。已經有不少學者開展了相關的研究工作,主要是通過持續的全局配置刷新來緩解配置存儲器中的錯誤數據位。在此基礎上,提出基于動態部分重構(Dynamic Partial Reconfiguration,DPR)技術對特定區域電路進行重配置,既減少了配置時間,又提高了效率。

另一種可行的處理方式就是在配置存儲器內部進行錯誤檢測和編碼糾正,通常可以檢測2位錯誤糾正1位錯誤(Single Error Correction and Double-Error Detection,SEC-DED),但是無法應對多比特翻轉(Multiple bit Upset,MBU)的情況[5]。對于用戶邏輯電路的容錯設計主要有兩種方式:一種是進行三模冗余(Triple Modular Redundancy,TMR)設計,主要缺點是代價大;另一種方法是在用戶邏輯電路中只進行錯誤檢測,采用復制比較(Duplication With Comparison,DWC)技術,對所有邏輯資源進行復制,增加比較器對結果進行比較。為了進一步減少資源利用,提出在用戶邏輯電路中進行錯誤檢測的同時,通過增加一個層級對電路狀態進行保存和恢復。

根據上面的分析,目前針對FPGA的軟錯誤技術主要涉及用戶邏輯層、配置存儲器層和控制層,不同的技術可針對不同的場景,在資源、功耗之間沒有針對特殊應用實現針對性的優化。因此,本文在此基礎上提出了基于三層級低開銷的系統性的緩解FPGA中MBU問題的技術框架,并通過Xilinx ZYNQ平臺針對開源的LEON3處理器軟核進行了故障注入的仿真驗證。

1 三層級軟錯誤緩解技術框架

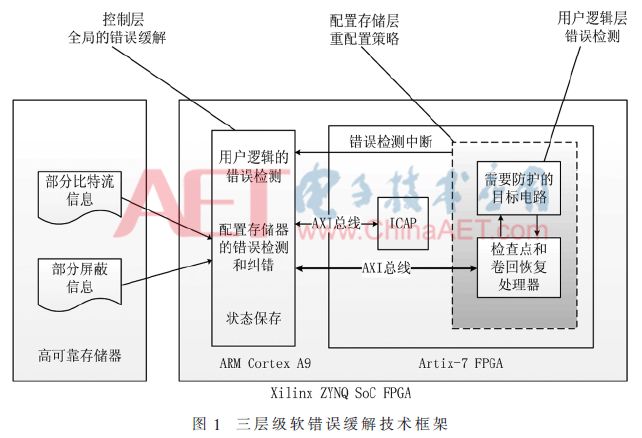

以最少的資源開銷、最低功耗和最短的處理延遲時間為優化目標,通過在用戶邏輯層、配置存儲器層和控制層3個層級的有效協同,提出了系統性的緩解商用現貨型FPGA空間應用面臨的MBU能力問題的軟錯誤緩解技術框架,其基于Xilinx ZYNQ SoC(System-on-Chip)的容錯技術框架如圖1所示。

用戶邏輯層選擇的冗余策略直接影響上層的架構。例如,使用TMR技術進行軟錯誤緩解,需要200%以上的資源開銷,不太適用于對資源和功耗都嚴格受限的空間應用環境,需要以面積和功耗的降低為優化目標,同時盡可能地減少延遲。

配置存儲器層選擇的策略的延遲和功耗主要依賴于重配置的粒度和檢糾錯能力,后者主要取決于是對整個配置數據還是只是對內置的糾錯編碼的冗余信息進行讀取和寫回。

在控制層,主要考慮的因素也是延遲和功耗,可采用檢查點(check pointing)和卷回(rollback)體制,主要的設計參數就是檢查點設置的周期。

2 用戶邏輯層

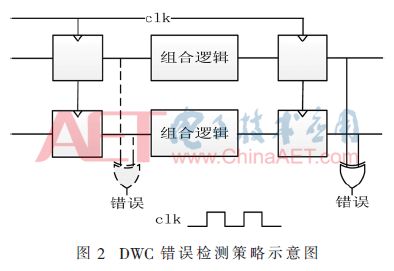

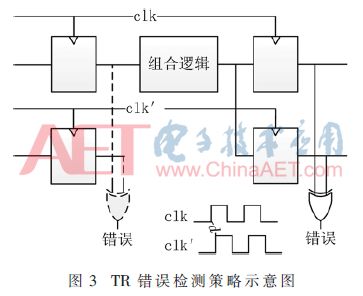

在用戶邏輯層,有兩種較為通用的錯誤檢測方法是:一種是DWC技術,這是一種全硬件備份策略;另一種就是時間冗余(Temporal Redundancy,TR)技術。圖2中的組合邏輯和時序邏輯都有兩個獨立的路徑,可以在每個觸發器的輸出進行比較,這樣檢測延遲時間最短。圖3中采用的是TR技術體制,只對時序邏輯進行冗余,通常是基本電路采用一個時鐘,一個延遲時間d的時鐘提供給冗余的觸發器,這樣整個電路的保持時間約束最壞情況是d,建立時間約束不變。該策略可用于在組合邏輯資源開銷很低的情況下同時檢測時序邏輯中的單粒子翻轉和組合邏輯中的單粒子瞬態現象(Single-Event Transients,SET)造成的錯誤。

延遲時間d首先要保證能夠檢測到組合邏輯中全部的SET,因此必須大于SET的最大持續時間。隨著工藝尺寸的減少,SET持續時間在增加,對于30 MeV·cm2/mg的LET和130 nm工藝,SET的持續時間為0.2~0.8 ns,Xilinx ZYNQ采用了28 nm工藝技術,延遲在2 ns左右。同時,隨著延遲d的增加,需要增加更多延遲布線資源,容易造成競爭冒險現象,極大地降低了最高時鐘工作頻率。因此,對于高達2 ns的延遲,TR策略的使用十分受限。

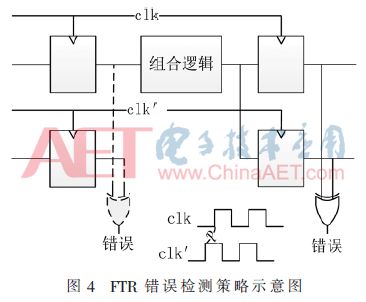

為了改進TR策略的適用范圍,提出了圖4所示的前向時間冗余(Forward Temporal Redundancy,FTR)策略,其與TR的主要區別是延遲是反向的,用于觸發器比較的時鐘相位提前,電路的保持時間沒有變化,但是建立時間約束更加嚴酷。因此,從clk到clk′時鐘域的最大傳播延遲減少了d。FTR是一種低功耗和低面積的解決方案,不存在冒險競爭條件。

3 配置存儲器層

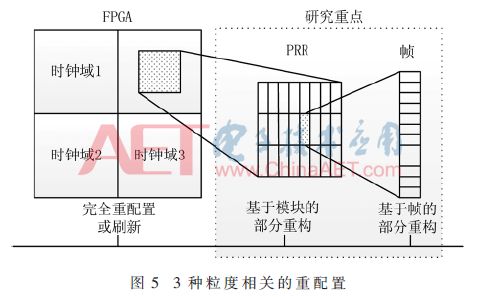

對于配置存儲器的重構或者刷新主要有3種不同粒度的操作,如圖5所示,第一種就是完全重配置或者刷新,效率比較低;第二種是基于模塊的部分重構,適用電路局限在部分重構區域(Partially Reconfigurable Region,PRR);第三種是最好的操作粒度,即基于幀的部分重構,幀是基于地址表的最小單位,對于Xilinx ZYNQ平臺,包括101個32 bit字,每一個幀通過對應的幀地址(Frame Address Register,FAR)進行訪問,可提供最快的錯誤檢測能力。

為提高檢糾錯效率,提出了在配置存儲器層組合使用基于模塊和基于幀的DPR方法:首先,準確定位用戶邏輯電路的資源位置,同時提取相應部分的比特流信息,然后實現快速的檢錯。基于幀的回讀可以用于檢測PRR內部所有錯誤。比特流信號中不僅包括配置位,也包括用戶存儲器單元,這些都可能在電路運行過程中狀態進行改變。這些對應比特位必須在回讀時通過.mask文件進行屏蔽。

上述方法特別適用于用戶電路可以分成多個獨立的小PRR的情況,對區域位置定位越準確,PRR越小,延遲就越少,電路的性能也越穩定。

同時,對于硬件錯誤的處理可以通過比特流的重定位技術,只需要小容量的外部存儲器對部分比特流進行存儲。

另一種通用的配置存儲器保護策略是Xilinx提供的IP核,對整個配置存儲器進行監視和錯誤糾正,這個核在Xilinx ZYNQ中不進行容錯設計就需要900個查找表和 700個觸發器,資源開銷較大。

Xilinx的FPGA支持多種刷新和配置途徑,為了盡可能減少延遲,提高系統的可靠性,優選ICAP接口。

4 控制層

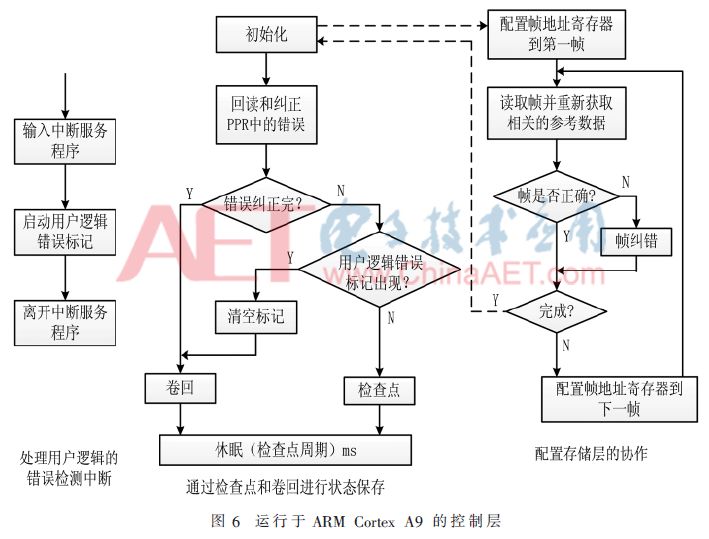

控制層主要完成兩個任務:協調處理和狀態保存。協調處理功能主要分為兩部分,一部分與用戶邏輯層有關,用于處理用戶邏輯中檢測到的錯誤;另一部分與配置存儲層有關,用于配置存儲器中錯誤的糾正。狀態保存專門用于支持檢查點和回滾操作,圖6所示為基于Xilinx ZYNQ平臺的完整算法描述。

檢查點和回滾操作可以通過3種方式實現。第一種是利用FPGA的BRAM存儲狀態信息,為保證這些信息不會被更改,必須采用合適的保護機制,通常采用內建的SEC-DED-EDAC,不能針對MBU情況。第二種方法是在更高層級進行處理,使用回讀捕獲特性,通過處理器直接從配置邏輯單元中重新獲取狀態信息。但是這種方法需要進行專門的布局設計,否則可能造成大的延遲開銷。最后一種方法是通過內部數據總線進行傳輸,比如AXI,可以在多PRR的模塊設計中進行共享,與第二種方法類似,重新獲取的狀態數據可以使用具備更高糾錯能力的軟件編碼進行糾錯,或者存儲到對單粒子免疫的存儲器中來保證數據的正確性,這些數據也可以傳回來支持卷回操作。

根據延遲和功耗的折中,選擇一個優化的檢查點的周期參數,處理器按照時間周期執行任務,這個參數需要根據應用需求進行調整。對于硬實時系統,檢查點周期可以減少為0,最小的延遲邊界通過回讀的時間確定。使用硬核處理器進行控制的方法由于減少了對單粒子敏感的FPGA資源的使用,可提高系統整體的可靠性。

5 利用開源的LEON3處理器核的測試結果

本文采用開源LEON3處理器軟核作為基本程序進行測試,其狀態單元主要包括程序計數器、寄存器文件和數據存儲器,需要通過檢查點和回滾操作進行保護。基于Xilinx ZYNQ XC7Z010-1CLG400C平臺進行測試。

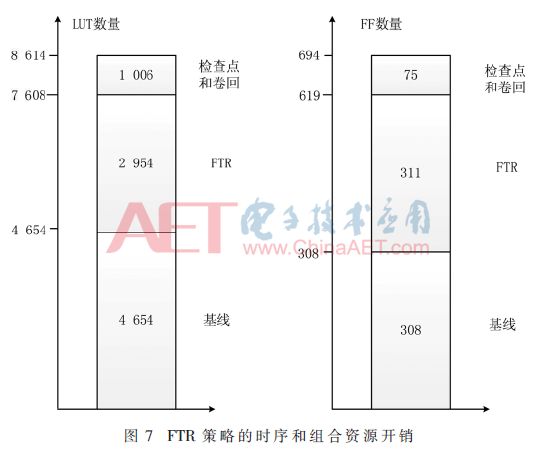

在用戶邏輯層對不同的冗余策略進行量化比較,表1所示為比較的結果。從表中可以看出,FTR策略的結果最好,功耗低,面積開銷低,適合空間應用,實現了性能和代價之間的最好平衡。由于更加嚴格地建立時間約束,與TR相比,FTR策略可以運行的最高工作頻率更大。

圖7所示為全部緩解技術實現需要的資源開銷比較,從圖中可以看出采用FTR策略,只增加了63%的組合邏輯和101%的時序邏輯資源。

在配置存儲器層,位置確定更準確,更能體現FTR的優勢,只需要34 μs就可以糾正一個幀中的錯誤,LEON3處理器包括2 640幀,在90 ms內就可以實現整個PRR的回讀,通過優化ICAP端口的速度可以進一步減少時間,最高可以運行到300 MHz。

在控制層,狀態信息保存在程序計數器中,寄存器文件和數據存儲器中,通過檢查點和卷回操作進行保護,并通過AXI總線與硬核處理器連接。這種策略對需要傳輸的數據量比較敏感,通常片上數據存儲器只有幾KB,更大的容量需求通過片外存儲器提供,片外存儲器可以采用復雜檢糾錯編碼。

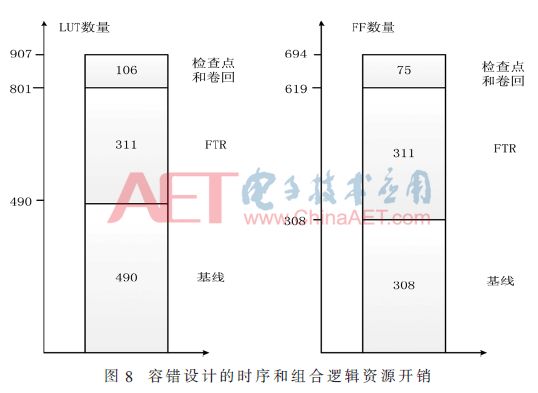

圖8顯示22%的組合邏輯和24%的時序邏輯開銷用于檢查點和卷回處理程序。

通過故障注入對整個軟件緩解技術框架的有效性進行了驗證。首先讀取幀對應的地址信息,然后對其中的一個比特位進行翻轉,最后把幀數據寫回,從而產生一個錯誤。通過Xilinx產生的.ebd和.ll文件可以找出有效使用的比特信息,試驗結果表明99.997%注入的軟錯誤得到糾正。

6 結論

為了滿足低成本高性能空間應用處理平臺的面積和功耗要求,提出了基于三層級的以功耗、面積、可靠性和延遲特性為目標的優化模型。以LEON3開源處理器軟核為基準程序,通過增加85%的組合邏輯和125%時序邏輯資源開銷,實現了冗余和狀態的保存,比單純的DWC體制更優。通過故障注入的仿真實驗,驗證了該框架可有效糾正99.997%的軟錯誤,具備MBU的緩解能力。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604360 -

存儲器

+關注

關注

38文章

7514瀏覽量

164004

原文標題:【學術論文】基于三層級低開銷的FPGA多比特翻轉緩解技術

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB四層板與三層板的區別是什么

三層架構的原理及作用_三層架構怎么用

基于三層級低開銷的系統性的緩解FPGA中MBU問題的技術框架

基于三層級低開銷的系統性的緩解FPGA中MBU問題的技術框架

評論