減少PCB設(shè)計上電磁干擾(EMI)的最佳方法之一就是靈活地使用運算放大器。遺憾的是,在許多應(yīng)用中,運算放大器的這個作用通常被忽略了。這可能是源于“運放易受EMI的影響,且必須采取額外的措施來增強其對噪聲的抗干擾性”這樣一種成見。

汽車、工業(yè)、醫(yī)療和許多其它應(yīng)用經(jīng)常會用到一些敏感的模擬電路,這些電路在其工作環(huán)境中必須能完成它們的功能,同時還要保持對噪聲干擾免疫。許多這些干擾由位于同一印刷電路板(PCB)上附近的“噪聲”電路引發(fā),這些噪聲會耦合到PCB及其電路上的電纜接口。

減少PCB設(shè)計上電磁干擾(EMI)的最佳方法之一就是靈活地使用運算放大器(簡稱“運放”)。遺憾的是,在許多應(yīng)用中,運算放大器的這個作用通常被忽略了。這可能是源于“運放易受EMI的影響,且必須采取額外的措施來增強其對噪聲的抗干擾性”這樣一種成見。盡管許多以前生產(chǎn)的器件確實是這樣,但設(shè)計師可能沒意識到,新近的運放通常具有比前世代更好的EMI免疫性能。設(shè)計師也可能不了解,或沒考慮運放電路可以為減少其系統(tǒng)和PCB設(shè)計中的噪音所提供的關(guān)鍵優(yōu)勢。本文回顧EMI的來源,并討論了有助于減輕敏感PCB設(shè)計上的近場EMI的運放特性。

EMI源、受擾電路和耦合機制

EMI是由無意且常常以不期望的方式?jīng)_擊二級電路(second electrical circuit)的電噪聲源引起的干擾。在所有情況下,干擾噪聲信號都是電壓、電流、電磁輻射這三者之一,或噪聲源以這三種形態(tài)的某種組合耦合到受擾電路。

EMI不限于射頻干擾(RFI)。 “較低”頻率范圍內(nèi)低于射頻的頻段存在強大的EMI源,如開關(guān)穩(wěn)壓器、LED電路和工作在幾十到幾百千赫范圍內(nèi)的電機驅(qū)動器。60Hz線電路噪聲是另一個例子。噪聲源通過四種可能的耦合機制中的一種,或多種將噪聲傳遞到受擾電路。四種方式中的三種被認(rèn)為是近場耦合,包括:傳導(dǎo)耦合、電場耦合和磁場耦合。第四種機制是遠(yuǎn)場輻射耦合,其中電磁能在多個波長上輻射。

差模噪聲的有源濾波

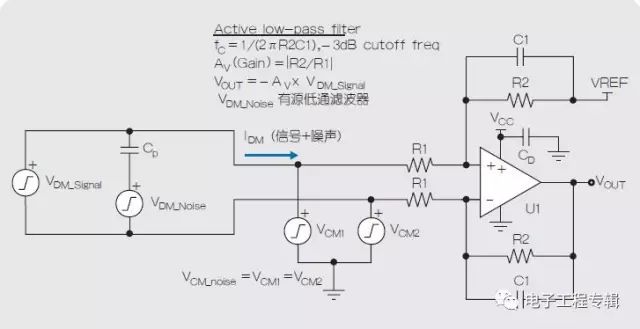

有源運放濾波器可以在電路帶寬內(nèi)顯著降低PCB上的EMI和噪聲,但在許多設(shè)計中它們未被充分利用。期望的差模(DM)信號可以被頻帶限制,而不需要的DM噪聲被濾除掉。圖1顯示了通過寄生電容(CP)耦合到輸入信號中的DM噪聲。組合信號和噪聲由一階有源低通濾波器接收。差分運放電路的低通截止頻率被設(shè)置為僅高于由R2和C1確定的所需信號帶寬。

較高的頻率以20dB/decade的幅度衰減。如果需要更大衰減,則可以使用高階有源濾波器(例如,-40或-60 dB/decade)。

推薦使用< 1%容差的電阻。同樣,具有極好溫度系數(shù)(NPO、COG)和5%(或< 5%)容差的電容器可獲得最佳的濾波器性能。

圖1:DM和CM輸入噪聲施加于有源運放濾波器

降低輸入共模噪聲

圖1中,共模(CM)噪聲源也在電路輸入端產(chǎn)生噪聲。CM噪聲可被描述為在兩個運放輸入端是公共(或相同)的噪聲電壓,并且不是運放試圖測量或調(diào)節(jié)的預(yù)期差模信號的一部分。CM噪聲可以多種方式發(fā)生。一個示例是:一個系統(tǒng),其中一個電路的接地參考電壓與其接口的第二個電路處于不同的電壓電位。“接地”電壓的差異可以是毫伏級或若干伏水平,并且也可能發(fā)生在許多不同的頻率。電壓的這些差異會導(dǎo)致意外的壓降并可能干擾連接電路的電流流動。

具有眾多電路的汽車、飛機和大型建筑物通常易受這種類型的干擾。

運放的一個關(guān)鍵優(yōu)點是它們的差分輸入級架構(gòu),以及在配置為差分放大器時抑制CM噪聲的能力。為每個運放指定了共模抑制比(CMRR),但電路的總CMRR還必須包括輸入和反饋電阻的影響。電阻變化強烈影響CMRR。因此,需要容差為0.1%、0.01%或更好的匹配電阻、才能實現(xiàn)應(yīng)用所需的CMRR。雖然使用外部電阻可以實現(xiàn)良好的性能,但使用具有內(nèi)部微調(diào)電阻的儀器或差分放大器也是一種選擇。例如,INA188是具有內(nèi)部微調(diào)電阻和104dB高CMRR的儀表放大器。

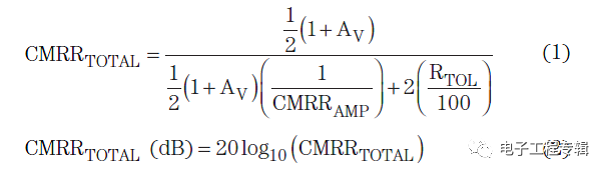

在圖1中,如果噪聲在電路的有效帶寬內(nèi),則CM噪聲(VCM_noise = VCM1 = VCM2)可被運放電路的CMRR所抑制。抑制水平取決于R2 / R1選擇的精確匹配電阻。公式1可用于確定CMRRTOTAL,它包括數(shù)據(jù)手冊中規(guī)定的電阻容差(RTOL)和運放CMRR的影響。例如,如果運放數(shù)據(jù)手冊給定其CMRR(dB)= 90dB,則(1/CMRRAMP)= 0.00003。在許多電路中,電阻容差成為實現(xiàn)目標(biāo)CMRRTOTAL的主要限制因素。

方程式1是從參考文獻(xiàn)1所描述的理想運放的CMRR等式中導(dǎo)出,其中CMRRAMP項被假定為非常大(無窮大)。對于理想運放,(1/CMRRAMP)項為零,CMRRTOTAL僅由電阻和AV確定。CMRRTOTAL可以使用公式2轉(zhuǎn)換為dB。

其中AV =運放的閉環(huán)增益,RTOL = R1和R2的容差%(例如,0.1%,0.01%,0.001%),CMRRAMP =數(shù)據(jù)表規(guī)范中以十進制格式表示的CMRR(不是dB)。

提高對RFI和其它高頻EMI的抗擾度

如前所述,有源濾波和CMRR可以可靠地降低器件頻帶限制范圍內(nèi)的電路噪聲,包括高至MHz范圍的DM和CM EMI。然而,暴露于高于預(yù)期工作頻率范圍的RFI噪聲可能會導(dǎo)致器件的非線性行為。運放在其高阻抗差分輸入級最易受RFI影響,因為DM和CM RFI噪聲可由內(nèi)部二極管(由硅上的p-n結(jié)形成)整流。這種整流產(chǎn)生一個小的直流電壓或偏移,被放大并可能在輸出端表現(xiàn)為錯誤的直流偏移。

根據(jù)系統(tǒng)的精度和靈敏度,這可能會產(chǎn)生不良的電路性能或行為。

幸運的是,使用兩種方法之一可提高運放對RFI的免疫力(或降低易感性)。第一個也是最好的選擇是使用EMI硬化(EMI-hardened)的運放,它包括內(nèi)部輸入濾波器,可以抑制數(shù)十MHz至高達(dá)千MHz范圍內(nèi)的噪聲。

TI目前提供80多種EMI硬化器件,可以通過TI運放參數(shù)搜索引擎搜索“EMI Hardened”找到。

第二個選擇是將外部EMI/RFI濾波器添加到運放的輸入。如果設(shè)計需要使用不包括內(nèi)部EMI濾波器的器件,這可能是唯一選擇。

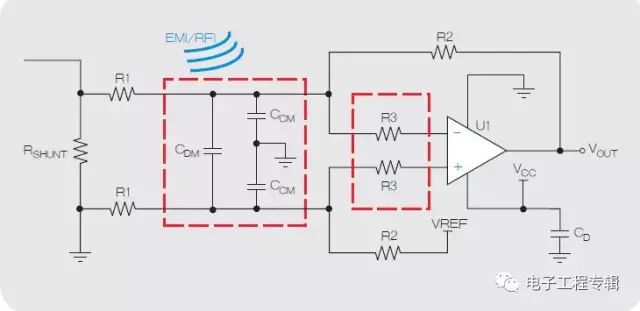

圖2顯示了使用外部DM和CM濾波器的標(biāo)準(zhǔn)差分放大器配置,其針對的是更高的EMI頻率。

圖2:無源EMI/RFI輸入濾波器提高了高頻抗擾度

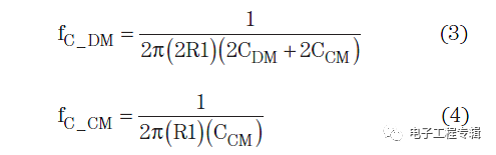

沒有輸入濾波器時,電路增益為|R2/R1|。如果添加了無源輸入濾波器,通常需要R3電阻來防范CDM電容降低放大器的相位裕度。DM低通濾波器由R1電阻、CDM和兩個CCM電容組成。

CM低通濾波器使用R1電阻和兩個CCM電容。

DM和CM濾波器(fC_DM和fC_CM)的-3dB截止頻率的等式如下所示。 fC_DM設(shè)置為運放電路的期望帶寬以上的頻率,并且通常首先確定CDM。然后將CCM電容選擇為比CDM小至少十倍,以將其對fC_DM的影響降至最低,且還因為CCM電容針對較高頻率。所以,fC_CM將被設(shè)置為高于fC_DM的頻率。請注意,EMI硬化器件可用于取代紅色線框所包圍的器件,簡化了設(shè)計。

低輸出阻抗減小干擾

運放的另一個重要特性是其極低的輸出阻抗,在大多數(shù)配置中通常為幾歐姆或更小。要了解如何有益于降低EMI,請考慮EMI如何影響低阻抗和高阻抗電路。

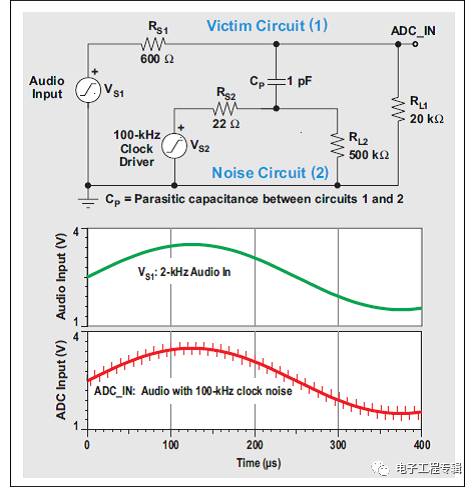

圖3中的圖表示兩個電路。第一個是模數(shù)轉(zhuǎn)換器(ADC)的輸入音頻電路,它包括1VP-P,2kHz正弦波(VS1)、600Ω源阻抗(RS1)和一個20kΩ負(fù)載阻抗(RL1)。諸如600Ω的源阻抗常見于麥克風(fēng)等音頻應(yīng)用;高輸入阻抗(如20 k)常見于音頻ADC。第二個電路是驅(qū)動3.3V時鐘信號(VS2)的100 kHz時鐘源,串聯(lián)終端電阻為22Ω(RS2),負(fù)載阻抗為500 kΩ(RL2)。高阻抗負(fù)載表示另一個器件的數(shù)字輸入。

在實際系統(tǒng)中,100至400 kHz范圍內(nèi)的I2C串行總線時鐘在音頻ADC和電路中很常見。雖然I2C時鐘通常以突發(fā)(不連續(xù))方式驅(qū)動,但此模擬顯示了在時鐘驅(qū)動時可能產(chǎn)生的影響。在高密度音頻和信息娛樂PCB設(shè)計中,在敏感音頻走線附近的時鐘走線的的確確會出現(xiàn)。只需幾個pF的寄生PCB電容就可發(fā)生電容耦合、并將時鐘噪聲電流注入到受擾音頻信號中。圖3是僅使用1pF的寄生電容進行的仿真示例。

圖3:時鐘噪聲源和音頻受擾電路

Audio input: 音頻輸入Victim circuit: 受擾電路Clock driver: 時鐘驅(qū)動器Noise circuit: 噪聲電路ADC Input: ADC輸入Parasitic capacitance between circuits 1 and 2: 電路1與電路2之間的寄生電容Audio with 100kHz clock noise: 伴隨有100kHz時鐘噪聲的音頻Time: 時間

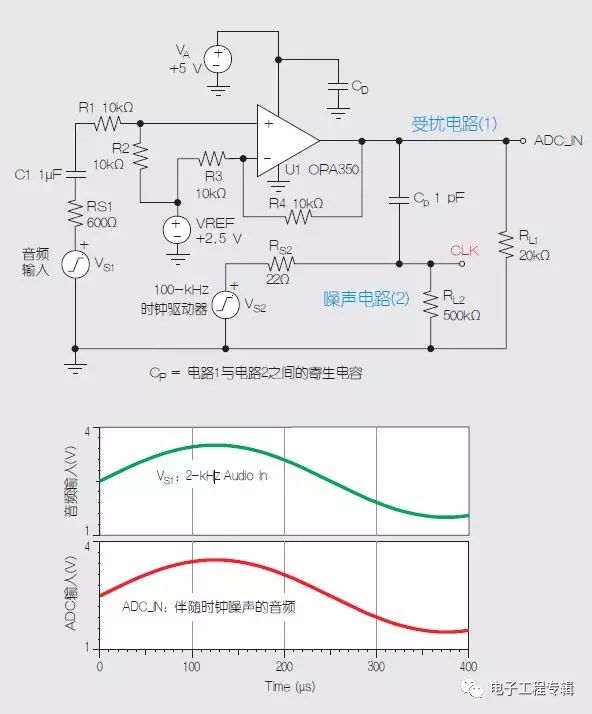

音頻電路如何降低噪聲? 事實證明,降低受擾電路的阻抗是降低其對耦合噪聲敏感性的一種方法。 對于具有較高源阻抗(> 50Ω)的電路,可以通過最小化與電路負(fù)載相關(guān)的源阻抗來降低耦合噪聲。在圖4中,同相配置的OPA350被添加到電路中以緩沖信號并將源阻抗與負(fù)載隔離開來。與600Ω相比,運放的輸出阻抗非常低,這顯著降低了時鐘噪聲。

圖4:可以減小時鐘源EMI的運放電路

別忘了去耦的重要性

在電源引腳添加去耦電容對于高頻EMI噪聲的濾除及增強運放電路的抗擾度非常有益。本文中的所有示圖都顯示出去耦電容CD是電路的一部分。雖然探究去耦問題會馬上進入深水區(qū),但有一些適用于任何設(shè)計的很好的“經(jīng)驗法則”。特別是選擇具有以下特性的電容:(a)非常好的溫度系數(shù),如X7R、NPO或COG(b)極低的等效串聯(lián)電感(ESL)(c)所需頻譜范圍內(nèi)的最低阻抗(d)1至100nF范圍內(nèi)的電容值通常很給力,但上述標(biāo)準(zhǔn)(b)和(c)比電容值(d)更重要。

電容的位置和走線連接與所選電容一樣重要。將電容盡可能靠近電源引腳。電容與PCB電源/接地的連接應(yīng)盡可能短,可采用短走線或過孔連接。

結(jié)論

運放可以幫助減小PCB上的近場EMI,并強化系統(tǒng)設(shè)計。以下是任何設(shè)計都要考慮的一些要點:

使用仔細(xì)選擇的有源濾波器配置降低電纜/電路的輸入DM噪聲(圖1)。

通過選擇具有高CMRR的運放并使用精密匹配電阻,減少電纜/電路的輸入CM噪聲(圖1,等式1、2)。

通過選擇EMI硬化器件或使用外部無源EMI/RFI濾波器,進一步增強對高頻EMI或RFI(DM/CM噪聲)的免疫力(圖2)。

當(dāng)將信號驅(qū)動到PCB上的其它電路時,使用運放輸出的低阻抗來降低耦合噪聲。

最后,通過對運放和所有其它電路應(yīng)用適當(dāng)?shù)娜ヱ畈呗詠斫档碗娫丛肼暋?/p>

-

pcb

+關(guān)注

關(guān)注

4322文章

23124瀏覽量

398507 -

運算放大器

+關(guān)注

關(guān)注

215文章

4951瀏覽量

173126 -

emi

+關(guān)注

關(guān)注

53文章

3593瀏覽量

127808

原文標(biāo)題:使用運算放大器來減少PCB上的近場EMI

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

減少PCB板電磁干擾的4個設(shè)計技巧

PCB設(shè)計:降低噪聲與電磁干擾的24個竅門

這幾招教你解決PCB設(shè)計中的電磁干擾(EMI)問題

解決高速PCB設(shè)計EMI(電磁干擾)的九大規(guī)則

PCB EMI的定義和設(shè)計技巧

教你減少PCB板電磁干擾的設(shè)計技巧

PCB設(shè)計中降低噪聲與電磁干擾的竅門

降低噪聲與電磁干擾的PCB設(shè)計24個竅門

如何降低PCB板設(shè)計時的電磁干擾EMI

PCB設(shè)計中的EMC/EMI問題分析

4個設(shè)計絕招教你減少PCB板電磁干擾

減少PCB設(shè)計上電磁干擾(EMI)的最佳方法之一

減少PCB設(shè)計上電磁干擾(EMI)的最佳方法之一

評論