在高速電路中,任何一個組成部分都會影響到電路的性能,對于PCB材料而言,不管是對電路的實際性能還是對高速信號完整性完整性的仿真都有非常顯著的影響。信號完整性仿真的精度,很大程度上都是依賴于仿真的建模和模型的準確性。本文是關于PCB材料參數的提取的介紹。本文作者是深圳市中澤凌電子有限公司的總經理黃春行。本文的原始標題是《One-pole Debye/Cole-Cole模型對多頻點復介電常數擬合》,有興趣的工程師可以參考本文嘗試做一下。

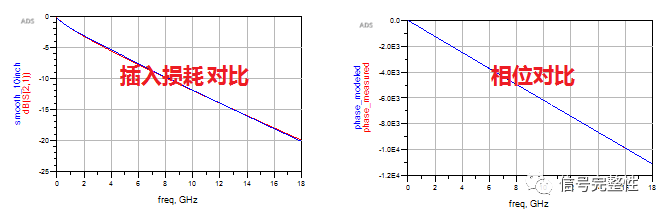

當然,對于PCB材料參數的提取的方法很多,目前業界采用ADS擬合提取是一種主流的方式。下圖是小編前段時間做的一個項目PCB參數的提取,然后對比測試和仿真的結果,10inch的傳輸線,在關注的頻率范圍之內對比的結果都非常的準確:

下面還是請看黃總的推導文章吧:

一、模型公式

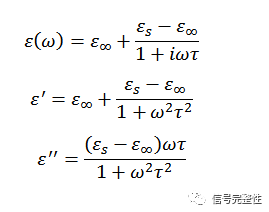

One-pole Debye模型:

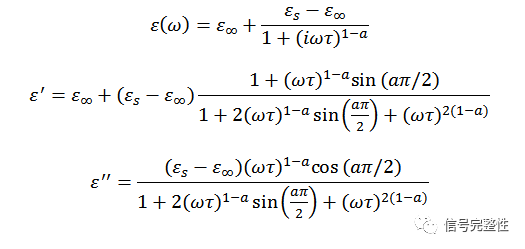

One-poleCole-Cole模型

不難發現,當Cole-Cole模型參數a=0,該模型退化為Debye模型。

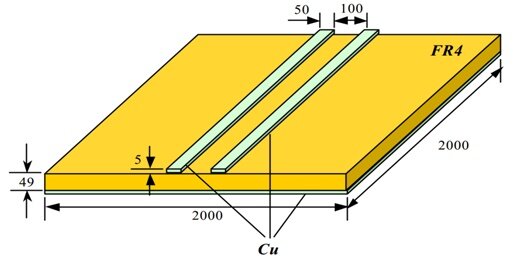

二、帶狀線法測量PCB介質的復介電常數

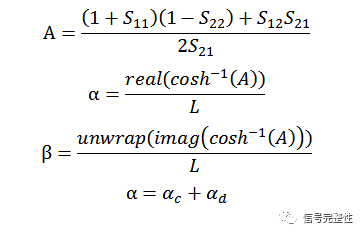

采用帶狀線法測量PCB介質的復介電常數,將測量得到的S參數矩陣轉換為ABCD矩陣,

其中,ac為導體損耗,ad為介質損耗

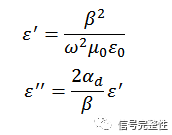

根據上式計算板材復介電常數:

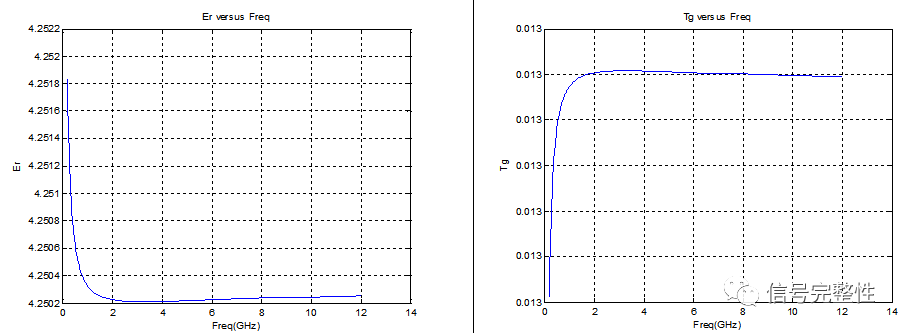

備注:該S參數為仿真獲得,板材介電常數設為常數,不滿足因果性要求。

從提取結果來看,Er與Tg是含有大量頻點的數據,但是,通常來說,一階Debye模型輸入只能輸入兩個頻點的結果數值,其余頻點的數值就被忽略了。

三、One-PoleDebye模型擬合多頻點復介電常數

假設:

1、 采用One-PoleDebye模型擬合板材復介電常數,主要關注模型損耗擬合精度

2、 介電常數Er與正切損耗角tg擬合在損耗公式體現,允許有一定的偏差,且對于高速鏈路的無源指標處理與有源仿真幾乎沒有影響。

目標函數:

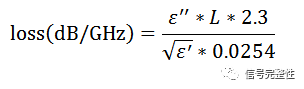

1、實際介質損耗函數:實際通道插損進行擬合處理,取出頻率f一次方的擬合系數,根據該系數,計算出通道實際介質損耗 ;

2、定義介質損耗擬合函數:

3、定義誤差函數

對于One-Pole Debye模型或One-PoleCole-Cole模型,通過搜索未知參數

?,采用最小二乘法非線性曲線擬合,使得誤差函數E最小。

?,采用最小二乘法非線性曲線擬合,使得誤差函數E最小。

值得注意的是:

1、由于誤差函數定義與搜索參量之間的是非線性,絕大部分情況下找到的是局部最優解,而不是全局最優解,因此提供一個合理的初始值,對于求解到滿足精度要求的結果也非常重要。

2、如果重點考慮有源仿真的影響,可以引入仿真信號功率譜密度在各頻點的權重,實現對不同頻點權重的處理。

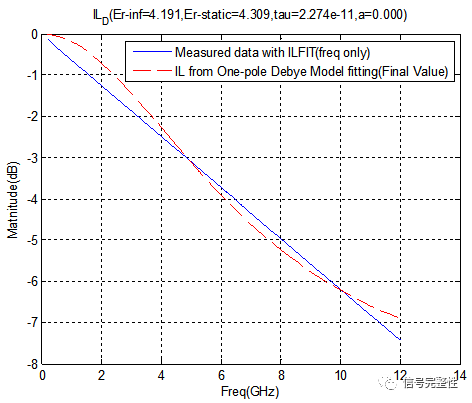

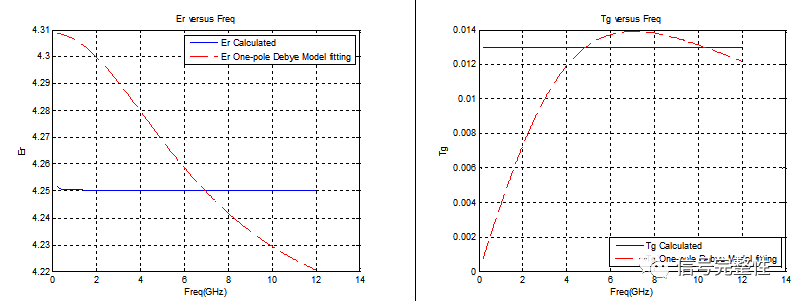

3.1 One-Pole Debye模型擬合結果:

從板材損耗擬合結果來看,One-Pole Debye擬合結果并不是特別好。這是主要由于One-PoleDebye模型可調整參數比較有限,同時,正切損耗角Tg在低頻區間,偏離測試值較大,導致低頻介質損耗過小。

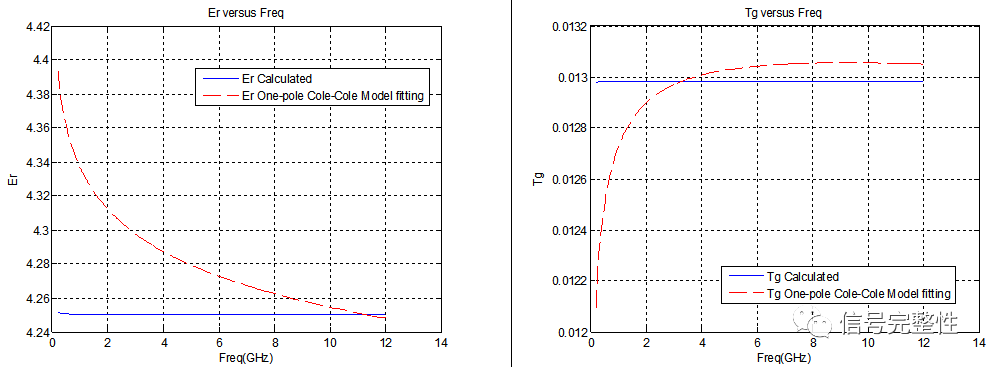

3.2 One-PoleCole-Cole模型擬合結果:

從板材損耗擬合結果來看,One-Pole Cole-Cole擬合結果非常好。這是主要由于One-PoleCole-Cole模型的參數a,對弛豫時間進行調整,可以使得模型更好適配板材頻域特性,同時,正切損耗角Tg在低頻區間,偏離測試值也非常小。

-

pcb

+關注

關注

4322文章

23126瀏覽量

398572 -

信號完整性

+關注

關注

68文章

1410瀏覽量

95522

原文標題:【干貨】一種PCB材料參數提取方法

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于pcb焊接技術介紹

PCB板材質及參數介紹

關于S參數的基本知識介紹

常用PCB基板材料特性介紹

高速SI應用中對各種層壓材料進行介電常數和介電損耗精確提取的方法

分享關于PCB設計技巧的詳細介紹

高溫PCB:材料清單和材料選擇

IPC關于PCB材料選擇的建議

如何使用EMS for Solidworks提取PCB結構的寄生參數

什么是PCB材料?什么是柔性PCB材料?

趣探實驗室 | 設計仿真——參數模型提取

關于PCB材料參數的提取的介紹

關于PCB材料參數的提取的介紹

評論