大家好,又到了每日學(xué)習(xí)的時(shí)候了。自1985年問世以來,FPGA這種可編程邏輯器件憑借在性能、上市時(shí)間、成本、穩(wěn)定性和長(zhǎng)期維護(hù)方面的優(yōu)勢(shì),在通信、醫(yī)療、工控和安防等領(lǐng)域占有一席之地。特別是近兩年,隨著云計(jì)算、高性能計(jì)算和人工智能的繁榮,擁有先天優(yōu)勢(shì)的FPGA更是得到了前所未有的關(guān)注。近幾年隨著國家開始大力發(fā)展實(shí)業(yè),國內(nèi)集成電路行業(yè)發(fā)展越來越好,隨之由于用戶對(duì)性能的要求越來越高,F(xiàn)PGA的可編程、高速度、低功耗、較低的二次開發(fā)成本的優(yōu)越特性,帶動(dòng)了FPGA行業(yè)的發(fā)展,有很多同學(xué)們開始自學(xué)FPGA。

首先,先來了解一下FPGA,F(xiàn)PGA:Field-Programmable Gate Array,中文名字:現(xiàn)場(chǎng)可編程門陣列。FPGA由六部分組成:可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核。英特爾首席執(zhí)行官科再奇曾這樣描述:“你可以把FPGA想象成一堆gate,能夠隨時(shí)編程。FPGA可以用作多個(gè)領(lǐng)域的加速器,例如在加密的同時(shí)進(jìn)行面部搜索,并能在微秒內(nèi)重新編程。其成本遠(yuǎn)低于大規(guī)模單個(gè)定制部件,并具有更高的靈活性。”

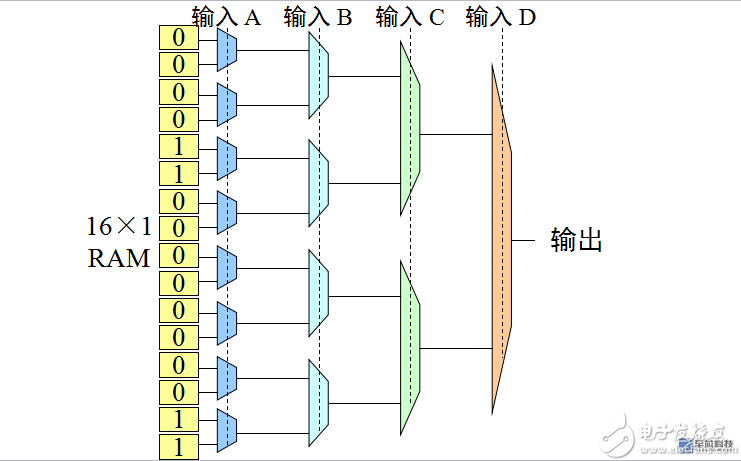

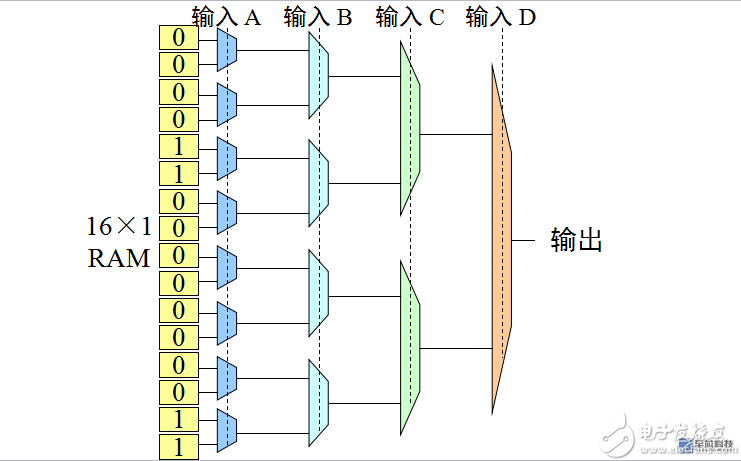

FPGA是可編程器件,與傳統(tǒng)邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,具有不同的結(jié)構(gòu),F(xiàn)PGA利用小型查找表(16×1RAM)來實(shí)現(xiàn)組合邏輯,每個(gè)查找表連接到一個(gè)D觸發(fā)器的輸入端,觸發(fā)器再來驅(qū)動(dòng)其他邏輯電路或驅(qū)動(dòng)I/O,由此構(gòu)成了既可實(shí)現(xiàn)組合邏輯功能又可實(shí)現(xiàn)時(shí)序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內(nèi)部靜態(tài)存儲(chǔ)單元加載編程數(shù)據(jù)來實(shí)現(xiàn)的,存儲(chǔ)在存儲(chǔ)器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實(shí)現(xiàn)的功能,F(xiàn)PGA允許無限次的編程。

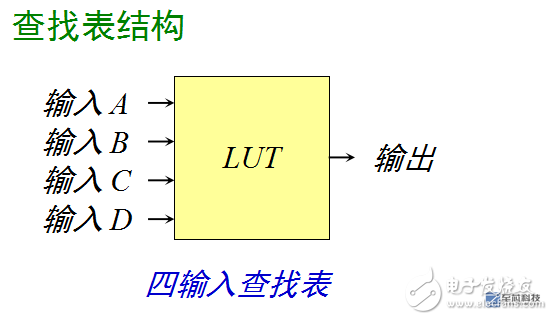

下圖為四輸入查找表結(jié)構(gòu)。

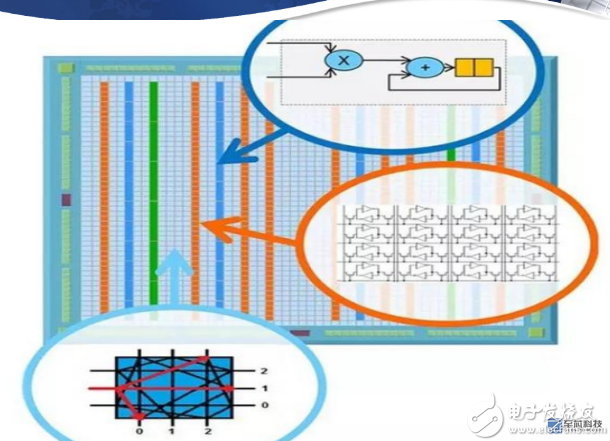

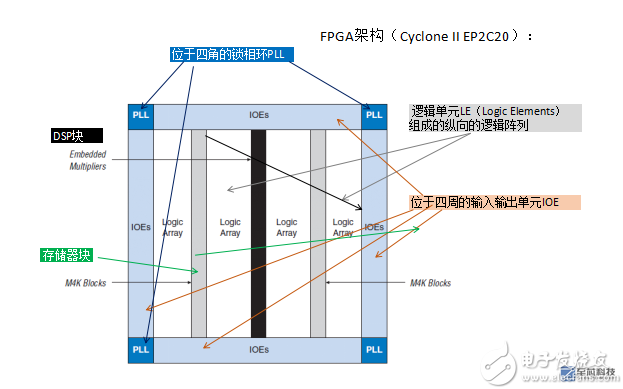

? ? ? ?下圖為FPGA架構(gòu)(舉例 ?Intel AlteraCyclone II EP2C20)

? ? ? ?下圖為FPGA架構(gòu)(舉例 ?Intel AlteraCyclone II EP2C20)

關(guān)于FPGA概念以及結(jié)構(gòu)等等的介紹就到這里,如果大家還想要詳細(xì)了解,可以自己去查閱資料。接下來,咱們就來聊聊初學(xué)FPGA時(shí)需要注意哪些知識(shí)點(diǎn)或者小細(xì)節(jié),希望對(duì)大家的學(xué)習(xí)有所幫助。

***************************************************************************************************************************

***區(qū)別一下軟硬件幾種類型***

***************************************************************************************************************************

***通用應(yīng)用軟件***

a. 軟件匯編語言(Assembly Language)是面向機(jī)器的程序設(shè)計(jì)語言。

b. 主要關(guān)心邏輯和抽象,關(guān)心代碼量大了之后復(fù)雜度可控。硬件資源較多,硬件性能差別較大,不需要針對(duì)特定資源設(shè)計(jì)。

c. 邏輯分層較多,來源于抽象的性能損耗可以接受。甚至于現(xiàn)在很多主流語言構(gòu)建在虛擬機(jī)和解釋器上。

d. 非實(shí)時(shí)。

e. 不需要了解底層硬件原理。

***************************************************************************************************************************

***嵌入式軟件(面向硬件編程)***

a. 時(shí)序可控。大部分場(chǎng)景要求實(shí)時(shí),因?yàn)橐獫M足硬件時(shí)序。非搶占的任務(wù)調(diào)度和中斷隊(duì)列都會(huì)引入定時(shí)的偏差。

b. 資源開銷可控。因?yàn)榍度胧接布h(huán)境大多只有有限的 RAM 和 Flash 資源。

c. 針對(duì)特定硬件環(huán)境設(shè)計(jì)。

d. 所有代碼上的抽象和優(yōu)化都必須是零損耗或者損耗可控(可以參考 rust 語言)。比較典型的是 GC 會(huì)引入嚴(yán)重的時(shí)序和資源不可控,所以系統(tǒng)語言很少使用。

***************************************************************************************************************************

***數(shù)字邏輯電路設(shè)計(jì)(硬件描述性語言)***

a. 數(shù)字電路設(shè)計(jì)不是編程,是設(shè)計(jì)的時(shí)候先有電路,再用語言描述出來。

b. 時(shí)序要求更嚴(yán),需要考慮建立時(shí)間和保持時(shí)間,及隨之而來的亞穩(wěn)態(tài)。

c. Coding style 會(huì)明顯的影響電路性能。邏輯都一樣,但是 DFF 的位置不一樣,就可能導(dǎo)致時(shí)序不滿足。

d. 并行化。執(zhí)行順序不再是 CPU 的順序執(zhí)行,而是多個(gè)并行的流水線。比如快速傅立葉 FFT。比如路由器的 CAM,單次動(dòng)作完成整表查表。

***************************************************************************************************************************

1. FPGA學(xué)習(xí)時(shí)使用的 VHDL 和 verilog HDL 不是編程語言,而是一種可綜合的硬件描述語言,我們?cè)诿枋龅臅r(shí)候一定要明白所要設(shè)計(jì)的是一個(gè)怎樣的電路。

2. 當(dāng)今社會(huì)做開發(fā)用的 Verilog HDL 語言偏多,Verilog HDL 支持兩種進(jìn)程 initial 和 always 進(jìn)程,前者只能用在TB(TestBench)中,后者才是可綜合的。

3. 阻塞與非阻塞指都是相對(duì)于進(jìn)程本身而言的,簡(jiǎn)單來講,阻塞用在描述組合邏輯電路,而非阻塞用于時(shí)序邏輯電路。

4. 使用進(jìn)程模塊的電路類型:

組合電路-----對(duì)組合邏輯中使用的所有輸入敏感

例子:

always@(a or b or c)

時(shí)序電路-----僅對(duì)時(shí)鐘和控制信號(hào)敏感

例子:

always @(posedge clk or negedge rst_n)

always既可以描述組合邏輯,也可以描述時(shí)序邏輯。

5. 可以用case語句完成多路選擇器的功能,但是列舉的情況一定要考慮全,否則會(huì)產(chǎn)生Latch。

6. verilog中有兩類子程序:

函數(shù)和任務(wù)

函數(shù)-----根據(jù)輸入返回一個(gè)值

-----產(chǎn)生組合邏輯

-----用在表達(dá)式中:assign mult_out=mult(ina,inb);

-----函數(shù)是組合邏輯,不能含有任何延時(shí),事件,或者時(shí)序控制聲明,至少有一個(gè)輸入變量

總是返回一個(gè)變量

-----可以調(diào)用函數(shù),但是不能調(diào)用任務(wù)。

任務(wù)-----可以是組合或者寄存器

-----以聲明的形式調(diào)用任務(wù):stm_out(nxt,first,sel,filter);

-----與其他編程語言中的任務(wù)相似

-----與函數(shù)不同任務(wù)不需要傳遞參數(shù),而函數(shù)要傳遞參數(shù)

-----可以調(diào)用任務(wù)和函數(shù)。

----- 可以含有任何延時(shí),事件,或者時(shí)序控制聲明

-----返回零個(gè)或者多個(gè)數(shù)值

可綜合的verilog語法子集是指用硬件可以實(shí)現(xiàn)的語法。力求用最簡(jiǎn)單的語言實(shí)現(xiàn)最復(fù)雜的硬件電路。

7. 硬件都有相應(yīng)的輸入輸出的接口,或者是輸入或者是輸出,或者是輸入輸出。

8. reg 型是指時(shí)序邏輯里面的一個(gè)寄存數(shù)據(jù)(寄存機(jī)類型),wire 是組合邏輯里面的一條連線(線型)。

9. define 定義了一個(gè)參數(shù),在整個(gè)工程里面都是有效地使用。 parameter 定義的一個(gè)參數(shù)只在當(dāng)前文件里面進(jìn)行使用。

10. 各種邏輯操作符,移位操作符,算術(shù)操作符大多是可綜合的。

11. assign一般是只針對(duì)于組合邏輯,而always語句既可以用于組合邏輯又可以用于時(shí)序邏輯,always模塊的敏感表,如果是電平,則為組合邏輯,如果是沿信號(hào)posedge或者negedge 則為時(shí)序邏輯。

12. begin----end和C語言里面的{}是類似的。

13. for 語句-----循環(huán)因?yàn)榫C合出來的結(jié)果可能比較浪費(fèi)資源,所以就一般用的比較少,但是在一些特定的設(shè)計(jì)中可以起到事半功倍的效果。

14. Total logic element 總共消耗的邏輯單元。

15. 行為級(jí)仿真可以理解為功能仿真(前仿真);布局布線后仿真可以理解為時(shí)序仿真(后仿真)。

16. 時(shí)序邏輯中時(shí)鐘和復(fù)位信號(hào)是必須的。

17. 注意wire賦值的一個(gè)問題如下:

wire[2:0] key_an=key_rst_r&(~key_rst)

其相當(dāng)于如下的一個(gè)賦值語句

wire[2:0] key_an;

assign key_an=key_rst_r&(~key_rst);

其實(shí)現(xiàn)的效果是一樣的。

此種方法為: 脈沖邊沿檢測(cè)法。

18. 實(shí)際工作中,除了描述仿真測(cè)試激勵(lì)(Testbench)時(shí)使用for循環(huán)語句外,極少在RTL級(jí)編碼中使用for循環(huán),這是因?yàn)閒or循環(huán)會(huì)被綜合器展開為所有變量情況的執(zhí)行語句,每個(gè)變量獨(dú)立占用寄存器資源,不能有效的復(fù)用硬件邏輯資源,造成巨大的浪費(fèi)。一般常用case語句代替。

19. FPGA一般觸發(fā)器資源比較豐富,而CPLD組合邏輯資源更豐富。

20. FPGA使用的兩種語言:VHDL 和 verilog HDL 。

VHDL 為美國國防部發(fā)明,用于較多的設(shè)計(jì)人員合作完成的特大型項(xiàng)目(一百萬門以上),語法/結(jié)構(gòu)比較嚴(yán)謹(jǐn),因?yàn)榫帉懗龅哪K風(fēng)格清晰。

verilog HDL 第三方支持工具較多,語法結(jié)構(gòu)比VHDL簡(jiǎn)單,學(xué)習(xí)來比較容易,仿真工具比較好用,測(cè)試激勵(lì)模塊容易編寫。

21. 時(shí)序設(shè)計(jì)的實(shí)質(zhì):電路設(shè)計(jì)的難點(diǎn)在于時(shí)序設(shè)計(jì),實(shí)質(zhì)就是滿足么一個(gè)觸發(fā)器 建立時(shí)間/保持時(shí)間 的要求。

(備注:建立時(shí)間:觸發(fā)器在時(shí)鐘上升沿到來之前,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的最小時(shí)間; 保持時(shí)間: 觸發(fā)器在時(shí)鐘上升沿到來之后,觸發(fā)器在時(shí)鐘上升沿到來之前,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的最小時(shí)間。)

22. 為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間?

因?yàn)橛|發(fā)器內(nèi)部數(shù)據(jù)的形成是需要一定的時(shí)間的,如果不滿足建立和保持時(shí)間,觸發(fā)器將進(jìn)入亞穩(wěn)態(tài),進(jìn)入亞穩(wěn)態(tài)后觸發(fā)器的輸出將不穩(wěn)定,在0和1之間變化,這時(shí)需要經(jīng)過一個(gè)恢復(fù)時(shí)間,其輸出才能 穩(wěn)定,但穩(wěn)定后的值并不一定是你的輸入值。這就是為什么要用兩級(jí)觸發(fā)器來同步異步輸入信號(hào)。這樣做可以防止由于異步輸入信號(hào)對(duì)于本級(jí)時(shí)鐘可能不滿足建立保持時(shí)間而使本級(jí)觸發(fā)器產(chǎn)生的亞穩(wěn)態(tài)傳播到后面邏輯中,導(dǎo)致亞穩(wěn)態(tài)的傳播。

23. 鎖存器(latch)和觸發(fā)器(flip-flop)區(qū)別?

電平敏感的存儲(chǔ)器件稱為鎖存器。可分為高電平鎖存器和低電平鎖存器,用于不同時(shí)鐘之間的信號(hào)同步。

有交叉耦合的門構(gòu)成的雙穩(wěn)態(tài)的存儲(chǔ)原件稱為觸發(fā)器。分為上升沿觸發(fā)和下降沿觸發(fā)。可以認(rèn)為是兩個(gè)不同電平敏感的鎖存器串連而成。前一個(gè)鎖存器決定了觸發(fā)器的建立時(shí)間,后一個(gè)鎖存器則決定了保持時(shí)間。

24. and so on.

最后,我們來簡(jiǎn)單聊一聊FPGA的應(yīng)用范圍。FPAG的應(yīng)用越來越廣泛,航天航空、汽車駕駛、醫(yī)療、廣播、測(cè)量測(cè)試、消費(fèi)電子、工業(yè)控制、計(jì)算機(jī)設(shè)備、武器裝備等等。從應(yīng)用場(chǎng)景角度分析,我們可以看到隨著谷歌的阿爾法狗打敗了人類圍棋冠軍后,深度學(xué)習(xí)已經(jīng)從神壇走下來,越來越多的人開始認(rèn)識(shí)到深度學(xué)習(xí)可能會(huì)改變未來的生活,成為未來科技發(fā)展的方向;而FPGA設(shè)計(jì)工具使其對(duì)深度學(xué)習(xí)領(lǐng)域經(jīng)常使用的上層軟件兼容性更強(qiáng),F(xiàn)PGA正是助力深度學(xué)習(xí)的一大技術(shù)。不同于CPU的是,F(xiàn)PGA和GPU內(nèi)都有大量的計(jì)算單元,因此它們的計(jì)算能力都很強(qiáng)。在進(jìn)行神經(jīng)網(wǎng)絡(luò)運(yùn)算的時(shí)候,兩者的速度會(huì)比CPU快很多。但是GPU由于架構(gòu)固定硬件原生支持的指令固定了,而FPGA則是可編程的。

隨著國家綜合實(shí)力越來越強(qiáng)大,國民經(jīng)濟(jì)越來越好,F(xiàn)PGA從之前的運(yùn)用廣泛的軍工行業(yè)在慢慢延伸到民用行業(yè),并且會(huì)越來越廣泛。

關(guān)于FPGA學(xué)習(xí)的小知識(shí)點(diǎn)我們就說到這里,如果大家還想要詳細(xì)了解,可以留言和樓主一起探討,歡迎各位留言。

加油,各位!好好學(xué)習(xí),天天向上@所有人。

首先,先來了解一下FPGA,F(xiàn)PGA:Field-Programmable Gate Array,中文名字:現(xiàn)場(chǎng)可編程門陣列。FPGA由六部分組成:可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核。英特爾首席執(zhí)行官科再奇曾這樣描述:“你可以把FPGA想象成一堆gate,能夠隨時(shí)編程。FPGA可以用作多個(gè)領(lǐng)域的加速器,例如在加密的同時(shí)進(jìn)行面部搜索,并能在微秒內(nèi)重新編程。其成本遠(yuǎn)低于大規(guī)模單個(gè)定制部件,并具有更高的靈活性。”

FPGA是可編程器件,與傳統(tǒng)邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,具有不同的結(jié)構(gòu),F(xiàn)PGA利用小型查找表(16×1RAM)來實(shí)現(xiàn)組合邏輯,每個(gè)查找表連接到一個(gè)D觸發(fā)器的輸入端,觸發(fā)器再來驅(qū)動(dòng)其他邏輯電路或驅(qū)動(dòng)I/O,由此構(gòu)成了既可實(shí)現(xiàn)組合邏輯功能又可實(shí)現(xiàn)時(shí)序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內(nèi)部靜態(tài)存儲(chǔ)單元加載編程數(shù)據(jù)來實(shí)現(xiàn)的,存儲(chǔ)在存儲(chǔ)器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實(shí)現(xiàn)的功能,F(xiàn)PGA允許無限次的編程。

下圖為四輸入查找表結(jié)構(gòu)。

? ? ? ?下圖為FPGA架構(gòu)(舉例 ?Intel AlteraCyclone II EP2C20)

? ? ? ?下圖為FPGA架構(gòu)(舉例 ?Intel AlteraCyclone II EP2C20)

? ? ? ?

? ? ? ?

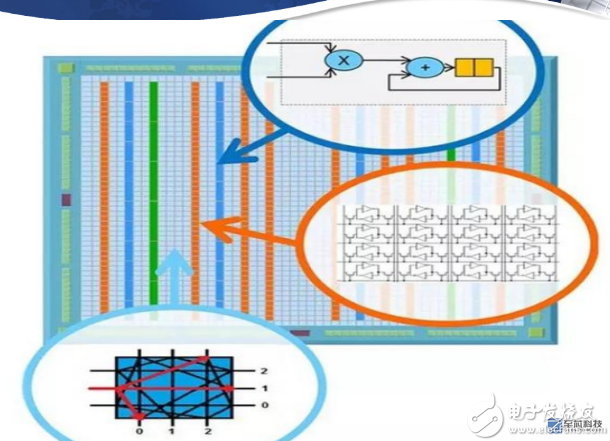

下圖為FPGA的結(jié)構(gòu)

關(guān)于FPGA概念以及結(jié)構(gòu)等等的介紹就到這里,如果大家還想要詳細(xì)了解,可以自己去查閱資料。接下來,咱們就來聊聊初學(xué)FPGA時(shí)需要注意哪些知識(shí)點(diǎn)或者小細(xì)節(jié),希望對(duì)大家的學(xué)習(xí)有所幫助。

***************************************************************************************************************************

***區(qū)別一下軟硬件幾種類型***

***************************************************************************************************************************

***通用應(yīng)用軟件***

a. 軟件匯編語言(Assembly Language)是面向機(jī)器的程序設(shè)計(jì)語言。

b. 主要關(guān)心邏輯和抽象,關(guān)心代碼量大了之后復(fù)雜度可控。硬件資源較多,硬件性能差別較大,不需要針對(duì)特定資源設(shè)計(jì)。

c. 邏輯分層較多,來源于抽象的性能損耗可以接受。甚至于現(xiàn)在很多主流語言構(gòu)建在虛擬機(jī)和解釋器上。

d. 非實(shí)時(shí)。

e. 不需要了解底層硬件原理。

***************************************************************************************************************************

***嵌入式軟件(面向硬件編程)***

a. 時(shí)序可控。大部分場(chǎng)景要求實(shí)時(shí),因?yàn)橐獫M足硬件時(shí)序。非搶占的任務(wù)調(diào)度和中斷隊(duì)列都會(huì)引入定時(shí)的偏差。

b. 資源開銷可控。因?yàn)榍度胧接布h(huán)境大多只有有限的 RAM 和 Flash 資源。

c. 針對(duì)特定硬件環(huán)境設(shè)計(jì)。

d. 所有代碼上的抽象和優(yōu)化都必須是零損耗或者損耗可控(可以參考 rust 語言)。比較典型的是 GC 會(huì)引入嚴(yán)重的時(shí)序和資源不可控,所以系統(tǒng)語言很少使用。

***************************************************************************************************************************

***數(shù)字邏輯電路設(shè)計(jì)(硬件描述性語言)***

a. 數(shù)字電路設(shè)計(jì)不是編程,是設(shè)計(jì)的時(shí)候先有電路,再用語言描述出來。

b. 時(shí)序要求更嚴(yán),需要考慮建立時(shí)間和保持時(shí)間,及隨之而來的亞穩(wěn)態(tài)。

c. Coding style 會(huì)明顯的影響電路性能。邏輯都一樣,但是 DFF 的位置不一樣,就可能導(dǎo)致時(shí)序不滿足。

d. 并行化。執(zhí)行順序不再是 CPU 的順序執(zhí)行,而是多個(gè)并行的流水線。比如快速傅立葉 FFT。比如路由器的 CAM,單次動(dòng)作完成整表查表。

***************************************************************************************************************************

1. FPGA學(xué)習(xí)時(shí)使用的 VHDL 和 verilog HDL 不是編程語言,而是一種可綜合的硬件描述語言,我們?cè)诿枋龅臅r(shí)候一定要明白所要設(shè)計(jì)的是一個(gè)怎樣的電路。

2. 當(dāng)今社會(huì)做開發(fā)用的 Verilog HDL 語言偏多,Verilog HDL 支持兩種進(jìn)程 initial 和 always 進(jìn)程,前者只能用在TB(TestBench)中,后者才是可綜合的。

3. 阻塞與非阻塞指都是相對(duì)于進(jìn)程本身而言的,簡(jiǎn)單來講,阻塞用在描述組合邏輯電路,而非阻塞用于時(shí)序邏輯電路。

4. 使用進(jìn)程模塊的電路類型:

組合電路-----對(duì)組合邏輯中使用的所有輸入敏感

例子:

always@(a or b or c)

時(shí)序電路-----僅對(duì)時(shí)鐘和控制信號(hào)敏感

例子:

always @(posedge clk or negedge rst_n)

always既可以描述組合邏輯,也可以描述時(shí)序邏輯。

5. 可以用case語句完成多路選擇器的功能,但是列舉的情況一定要考慮全,否則會(huì)產(chǎn)生Latch。

6. verilog中有兩類子程序:

函數(shù)和任務(wù)

函數(shù)-----根據(jù)輸入返回一個(gè)值

-----產(chǎn)生組合邏輯

-----用在表達(dá)式中:assign mult_out=mult(ina,inb);

-----函數(shù)是組合邏輯,不能含有任何延時(shí),事件,或者時(shí)序控制聲明,至少有一個(gè)輸入變量

總是返回一個(gè)變量

-----可以調(diào)用函數(shù),但是不能調(diào)用任務(wù)。

任務(wù)-----可以是組合或者寄存器

-----以聲明的形式調(diào)用任務(wù):stm_out(nxt,first,sel,filter);

-----與其他編程語言中的任務(wù)相似

-----與函數(shù)不同任務(wù)不需要傳遞參數(shù),而函數(shù)要傳遞參數(shù)

-----可以調(diào)用任務(wù)和函數(shù)。

----- 可以含有任何延時(shí),事件,或者時(shí)序控制聲明

-----返回零個(gè)或者多個(gè)數(shù)值

可綜合的verilog語法子集是指用硬件可以實(shí)現(xiàn)的語法。力求用最簡(jiǎn)單的語言實(shí)現(xiàn)最復(fù)雜的硬件電路。

7. 硬件都有相應(yīng)的輸入輸出的接口,或者是輸入或者是輸出,或者是輸入輸出。

8. reg 型是指時(shí)序邏輯里面的一個(gè)寄存數(shù)據(jù)(寄存機(jī)類型),wire 是組合邏輯里面的一條連線(線型)。

9. define 定義了一個(gè)參數(shù),在整個(gè)工程里面都是有效地使用。 parameter 定義的一個(gè)參數(shù)只在當(dāng)前文件里面進(jìn)行使用。

10. 各種邏輯操作符,移位操作符,算術(shù)操作符大多是可綜合的。

11. assign一般是只針對(duì)于組合邏輯,而always語句既可以用于組合邏輯又可以用于時(shí)序邏輯,always模塊的敏感表,如果是電平,則為組合邏輯,如果是沿信號(hào)posedge或者negedge 則為時(shí)序邏輯。

12. begin----end和C語言里面的{}是類似的。

13. for 語句-----循環(huán)因?yàn)榫C合出來的結(jié)果可能比較浪費(fèi)資源,所以就一般用的比較少,但是在一些特定的設(shè)計(jì)中可以起到事半功倍的效果。

14. Total logic element 總共消耗的邏輯單元。

15. 行為級(jí)仿真可以理解為功能仿真(前仿真);布局布線后仿真可以理解為時(shí)序仿真(后仿真)。

16. 時(shí)序邏輯中時(shí)鐘和復(fù)位信號(hào)是必須的。

17. 注意wire賦值的一個(gè)問題如下:

wire[2:0] key_an=key_rst_r&(~key_rst)

其相當(dāng)于如下的一個(gè)賦值語句

wire[2:0] key_an;

assign key_an=key_rst_r&(~key_rst);

其實(shí)現(xiàn)的效果是一樣的。

此種方法為: 脈沖邊沿檢測(cè)法。

18. 實(shí)際工作中,除了描述仿真測(cè)試激勵(lì)(Testbench)時(shí)使用for循環(huán)語句外,極少在RTL級(jí)編碼中使用for循環(huán),這是因?yàn)閒or循環(huán)會(huì)被綜合器展開為所有變量情況的執(zhí)行語句,每個(gè)變量獨(dú)立占用寄存器資源,不能有效的復(fù)用硬件邏輯資源,造成巨大的浪費(fèi)。一般常用case語句代替。

19. FPGA一般觸發(fā)器資源比較豐富,而CPLD組合邏輯資源更豐富。

20. FPGA使用的兩種語言:VHDL 和 verilog HDL 。

VHDL 為美國國防部發(fā)明,用于較多的設(shè)計(jì)人員合作完成的特大型項(xiàng)目(一百萬門以上),語法/結(jié)構(gòu)比較嚴(yán)謹(jǐn),因?yàn)榫帉懗龅哪K風(fēng)格清晰。

verilog HDL 第三方支持工具較多,語法結(jié)構(gòu)比VHDL簡(jiǎn)單,學(xué)習(xí)來比較容易,仿真工具比較好用,測(cè)試激勵(lì)模塊容易編寫。

21. 時(shí)序設(shè)計(jì)的實(shí)質(zhì):電路設(shè)計(jì)的難點(diǎn)在于時(shí)序設(shè)計(jì),實(shí)質(zhì)就是滿足么一個(gè)觸發(fā)器 建立時(shí)間/保持時(shí)間 的要求。

(備注:建立時(shí)間:觸發(fā)器在時(shí)鐘上升沿到來之前,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的最小時(shí)間; 保持時(shí)間: 觸發(fā)器在時(shí)鐘上升沿到來之后,觸發(fā)器在時(shí)鐘上升沿到來之前,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的最小時(shí)間。)

22. 為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間?

因?yàn)橛|發(fā)器內(nèi)部數(shù)據(jù)的形成是需要一定的時(shí)間的,如果不滿足建立和保持時(shí)間,觸發(fā)器將進(jìn)入亞穩(wěn)態(tài),進(jìn)入亞穩(wěn)態(tài)后觸發(fā)器的輸出將不穩(wěn)定,在0和1之間變化,這時(shí)需要經(jīng)過一個(gè)恢復(fù)時(shí)間,其輸出才能 穩(wěn)定,但穩(wěn)定后的值并不一定是你的輸入值。這就是為什么要用兩級(jí)觸發(fā)器來同步異步輸入信號(hào)。這樣做可以防止由于異步輸入信號(hào)對(duì)于本級(jí)時(shí)鐘可能不滿足建立保持時(shí)間而使本級(jí)觸發(fā)器產(chǎn)生的亞穩(wěn)態(tài)傳播到后面邏輯中,導(dǎo)致亞穩(wěn)態(tài)的傳播。

23. 鎖存器(latch)和觸發(fā)器(flip-flop)區(qū)別?

電平敏感的存儲(chǔ)器件稱為鎖存器。可分為高電平鎖存器和低電平鎖存器,用于不同時(shí)鐘之間的信號(hào)同步。

有交叉耦合的門構(gòu)成的雙穩(wěn)態(tài)的存儲(chǔ)原件稱為觸發(fā)器。分為上升沿觸發(fā)和下降沿觸發(fā)。可以認(rèn)為是兩個(gè)不同電平敏感的鎖存器串連而成。前一個(gè)鎖存器決定了觸發(fā)器的建立時(shí)間,后一個(gè)鎖存器則決定了保持時(shí)間。

24. and so on.

最后,我們來簡(jiǎn)單聊一聊FPGA的應(yīng)用范圍。FPAG的應(yīng)用越來越廣泛,航天航空、汽車駕駛、醫(yī)療、廣播、測(cè)量測(cè)試、消費(fèi)電子、工業(yè)控制、計(jì)算機(jī)設(shè)備、武器裝備等等。從應(yīng)用場(chǎng)景角度分析,我們可以看到隨著谷歌的阿爾法狗打敗了人類圍棋冠軍后,深度學(xué)習(xí)已經(jīng)從神壇走下來,越來越多的人開始認(rèn)識(shí)到深度學(xué)習(xí)可能會(huì)改變未來的生活,成為未來科技發(fā)展的方向;而FPGA設(shè)計(jì)工具使其對(duì)深度學(xué)習(xí)領(lǐng)域經(jīng)常使用的上層軟件兼容性更強(qiáng),F(xiàn)PGA正是助力深度學(xué)習(xí)的一大技術(shù)。不同于CPU的是,F(xiàn)PGA和GPU內(nèi)都有大量的計(jì)算單元,因此它們的計(jì)算能力都很強(qiáng)。在進(jìn)行神經(jīng)網(wǎng)絡(luò)運(yùn)算的時(shí)候,兩者的速度會(huì)比CPU快很多。但是GPU由于架構(gòu)固定硬件原生支持的指令固定了,而FPGA則是可編程的。

隨著國家綜合實(shí)力越來越強(qiáng)大,國民經(jīng)濟(jì)越來越好,F(xiàn)PGA從之前的運(yùn)用廣泛的軍工行業(yè)在慢慢延伸到民用行業(yè),并且會(huì)越來越廣泛。

關(guān)于FPGA學(xué)習(xí)的小知識(shí)點(diǎn)我們就說到這里,如果大家還想要詳細(xì)了解,可以留言和樓主一起探討,歡迎各位留言。

加油,各位!好好學(xué)習(xí),天天向上@所有人。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605473

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

proteus仿真教程 全...全...全...!不看會(huì)后悔的哦!

proteus仿真教程 全...全...全...!不看會(huì)后悔的哦!{:soso__5663373028670280397_3:}

發(fā)表于 06-28 22:25

很經(jīng)典的labview教程 不看后悔 從零開始

點(diǎn)擊學(xué)習(xí)>>《龍哥手把手教你學(xué)LabVIEW視覺設(shè)計(jì)》視頻教程很經(jīng)典的labview教程不看后悔從零開始

發(fā)表于 11-25 16:57

不看會(huì)后悔的書《51單片機(jī)C語言創(chuàng)新教程.pdf》

不看會(huì)后悔的書《51單片機(jī)C語言創(chuàng)新教程.pdf》

發(fā)表于 07-22 12:03

學(xué)習(xí)FPGA需要留意,很實(shí)用,不看會(huì)后悔哦

大家好,又到了每日學(xué)習(xí)的時(shí)候了。自1985年問世以來,FPGA這種可編程邏輯器件憑借在性能、上市時(shí)間、成本、穩(wěn)定性和長(zhǎng)期維護(hù)方面的優(yōu)勢(shì),在通信、醫(yī)療、工控和安防等領(lǐng)域占有一席之地。特別是近兩年,隨著

發(fā)表于 02-04 11:25

基于FPGA的數(shù)據(jù)無阻塞交換設(shè)計(jì)方案,不看肯定后悔

基于FPGA的數(shù)據(jù)無阻塞交換設(shè)計(jì)方案,不看肯定后悔

發(fā)表于 04-29 06:48

基于EDA技術(shù)的FPGA設(shè)計(jì)計(jì)算機(jī)應(yīng)用,不看肯定后悔

基于EDA技術(shù)的FPGA設(shè)計(jì)計(jì)算機(jī)應(yīng)用,不看肯定后悔

發(fā)表于 05-06 06:24

嵌入式視頻處理系統(tǒng)領(lǐng)域的FPGA驗(yàn)證,不看肯定后悔

嵌入式視頻處理系統(tǒng)領(lǐng)域的FPGA驗(yàn)證,不看肯定后悔

發(fā)表于 05-07 06:18

關(guān)于Assert_param的學(xué)習(xí)筆記分享,不看肯定后悔

關(guān)于Assert_param的學(xué)習(xí)筆記分享,不看肯定后悔

發(fā)表于 06-10 13:59

學(xué)習(xí)FPGA需要留意,很實(shí)用不看會(huì)后悔

學(xué)習(xí)FPGA需要留意,很實(shí)用不看會(huì)后悔

評(píng)論