自1985年首款FPGA誕生以來,F(xiàn)PGA已經(jīng)是一名在電子信息領(lǐng)域征戰(zhàn)了30年的老兵,這名戰(zhàn)功赫赫的老兵如今已經(jīng)正式開赴了一個新的戰(zhàn)場。但是FPGA并不是萬能的。相對于串行結(jié)構(gòu)處理器,其設(shè)計(jì)的靈活性是以工作量的增加為代價(jià)的。FPGA與ARM、DSP(如下圖所示)的比較如下。

一、從語言本身的差異來看,基于Verilog HDL和VHDL的硬件語言與C/C++相比,在代碼靈活性、開發(fā)效率等方面還有較大差距。通常一段十幾行的C語言代碼使用硬件語言實(shí)現(xiàn)后,代碼量會增加到幾十行之多。同時,在進(jìn)行硬件語言描述時,一個合格的FPGA工程師不僅要實(shí)現(xiàn)相應(yīng)的邏輯功能,還要在頭腦里浮現(xiàn)編寫的代碼所生成的邏輯結(jié)構(gòu),并考慮到門延時對系統(tǒng)時序的影響。這樣才能夠設(shè)計(jì)出穩(wěn)定高效的邏輯結(jié)構(gòu),減少后期時序調(diào)整的工作。

二、從語言本身的差異來看,基于Verilog HDL和VHDL的硬件語言與C/C++相比,在代碼靈活性、開發(fā)效率等方面還有較大差距。通常一段十幾行的C語言代碼使用硬件語言實(shí)現(xiàn)后,代碼量會增加到幾十行之多。同時,在進(jìn)行硬件語言描述時,一個合格的FPGA工程師不僅要實(shí)現(xiàn)相應(yīng)的邏輯功能,還要在頭腦里浮現(xiàn)編寫的代碼所生成的邏輯結(jié)構(gòu),并考慮到門延時對系統(tǒng)時序的影響。這樣才能夠設(shè)計(jì)出穩(wěn)定高效的邏輯結(jié)構(gòu),減少后期時序調(diào)整的工作。

三、從工作頻率來看,ARM、DSP等處理器采用的是成熟的內(nèi)核結(jié)構(gòu),具有較好的時序特性,其最高頻率通常為600MHz~1.25GHz。為提高處理能力,TI等芯片廠商采用多核的設(shè)計(jì)方式,設(shè)計(jì)了具有8核DSP、8核ARM的處理器,每個核心的最大工作頻率可 達(dá)1.25GHz,通過設(shè)置可以開啟和關(guān)閉其中的內(nèi)核來靈活地協(xié)調(diào)功耗與處理能力之間的矛盾。目前TI公司正在設(shè)計(jì)具有8核ARM+8核DSP的處理器,來滿足高速系統(tǒng)中集中運(yùn)算的需求。而在FPGA的設(shè)計(jì)中,不同的系統(tǒng)具有不同的最高工作頻率,該頻率可以在編譯報(bào)告中獲得。對于Altera公司的FPGA,通過TimeQuest工具調(diào)整時序,可以提升設(shè)計(jì)工程的最高頻率。一個具有良好設(shè)計(jì)的FPGA工程的最高頻率可達(dá)150MHz以上。

四、從執(zhí)行方式來看,基于嵌入式平臺的C/C++語言在已有的硬件結(jié)構(gòu)中執(zhí)行,只需正確配置相關(guān)寄存器即可。而使用硬件語言的設(shè)計(jì)需自行設(shè)計(jì)硬件結(jié)構(gòu),在生成結(jié)構(gòu)前還要經(jīng)過前仿真、綜合、布局布線、后仿真等步驟,開發(fā)周期較長。這一情況在較為復(fù)雜的FPGA工程設(shè)計(jì)中尤為嚴(yán)重。例如,一個添加了4個DDR2的IP的工程在i5處理器、4G內(nèi)存的計(jì)算機(jī)上,編譯時間甚至在20min以上。

五、從算法應(yīng)用來看,ARM、DSP等處理器中集成了加法器、乘法器等運(yùn)算單元,尤其是在DSP中,可以在一個周期內(nèi)進(jìn)行8×8位甚至16×16位的乘法運(yùn)算。同時,這些處理器還支持浮點(diǎn)運(yùn)算能力。而FPGA對這部分運(yùn)算并不擅長,即使在較為簡單的加法運(yùn)算中,若進(jìn)行加法的兩個數(shù)據(jù)具有較高的位寬,由于傳統(tǒng)的加法中的進(jìn)位方式是串行結(jié)構(gòu),所以在其生成的結(jié)構(gòu)中會產(chǎn)生較長的門延時,從而會降低時序的余量,甚至?xí)档拖到y(tǒng)編譯后的最高工作頻率。

六、從算法設(shè)計(jì)來看,在ARM、DSP等處理器中設(shè)計(jì)算法前,需要提前構(gòu)思算法的流程圖,然后進(jìn)行代碼的編寫。而在FPGA設(shè)計(jì)中,主要包含三種設(shè)計(jì)方式:面向狀態(tài)的設(shè)計(jì),面向活動的設(shè)計(jì)和面向結(jié)構(gòu)的設(shè)計(jì)。

(1)面向狀態(tài)的設(shè)計(jì)是以狀態(tài)機(jī)為代表的設(shè)計(jì)方式,即通過控制信號和時序信號觸發(fā)狀態(tài)機(jī)進(jìn)行狀態(tài)的遷移。狀態(tài)機(jī)的設(shè)計(jì)是FPGA開發(fā)中必不可少的環(huán)節(jié),這部分內(nèi)容將 在7.2.2節(jié)中詳細(xì)敘述。

(2)面向活動的設(shè)計(jì)是以數(shù)據(jù)流和流程圖為代表的設(shè)計(jì)方式。尤其是在傳輸系統(tǒng)、實(shí)時算法設(shè)計(jì)中,常使用基于數(shù)據(jù)流的設(shè)計(jì)方式。常見的數(shù)據(jù)流的操作方式包括數(shù)據(jù)的寄存器同步緩沖、數(shù)據(jù)傳遞、數(shù)據(jù)運(yùn)算與流水設(shè)計(jì)、數(shù)據(jù)的存取等。

(3)面向結(jié)構(gòu)的設(shè)計(jì)常用于較大的系統(tǒng)設(shè)計(jì)中,用于描述模塊與模塊、單元與單元之間的互聯(lián)關(guān)系,主要包括數(shù)據(jù)信號與控制信號。根據(jù)不同的層次描述,主要可以分為系統(tǒng)級結(jié)構(gòu)描述、寄存器級結(jié)構(gòu)描述、門級結(jié)構(gòu)描述等。

為了解決這些硬件工程師所面臨的問題,Altera Xilinx等FPGA公司不遺余力地對開發(fā)平臺進(jìn)行了完善,如下以Altera的解決方案為例。

對于第一點(diǎn)提及的設(shè)計(jì)語言的問題,Altera推出了Qsys(SOPC)等片上軟核,使工程師在FPGA中同樣可以使用更為靈活的C語言進(jìn)行編程。Qsys(SOPC)中包含了片內(nèi)、片外存儲器、定時器及各種接口等IP,使工程師可以按需定制自己的片內(nèi)處理器。使用這種方式,在一定程度上緩解了硬件描述語言開發(fā)周期過長的缺點(diǎn),也成為一種對FPGA系統(tǒng)進(jìn)行前期功能驗(yàn)證的有效手段。

對于第二點(diǎn)提及的通用模塊或接口占用開發(fā)周期的問題,Altera和供應(yīng)商設(shè)計(jì)了大量具有知識產(chǎn)權(quán)的IP(Intellectual Property,知識產(chǎn)權(quán)),包括運(yùn)算類、通信類、數(shù)字信號處理類、門類、輸入/輸出類、接口類、JTAG擴(kuò)展類、存儲類等多種類別。這些IP是經(jīng)過嚴(yán)格測試和優(yōu)化過的,其中部分IP免費(fèi),上面提到的SOPC中應(yīng)用的大部分IP都是免費(fèi)的。

值得注意的是,盡管大部分基本功能的IP可以在不同系列的FPGA間通用,依然有一些IP并不支持所有系列的FPGA,使用這些IP在不同系列的FPGA間進(jìn)行工程移植時需要注意。所使用的IP是否支持當(dāng)前芯片,可以在Quartus II的MegWizard管理器中查閱,也可以在官網(wǎng)中查閱。Altera支持的所有IP及其適用系列可參考以下網(wǎng)址:http://www. altera.com.cn/products/ip/ip-index.jsp。

對于第三點(diǎn)提到的工作頻率的問題,不同的處理器具有不同的應(yīng)用領(lǐng)域。在高速數(shù)據(jù)處理過程中,ARM、DSP等固然可達(dá)到較高的工作頻率,然而相對于FPGA,其高速的優(yōu)勢僅體現(xiàn)在串行結(jié)構(gòu)的算法中。在FPGA的設(shè)計(jì)中,可利用其硬件設(shè)計(jì)的靈活性,采用并行算法或?qū)⒋兴惴ǜ脑鞛椴⑿兴惴ǎ缓笤贔PGA中實(shí)現(xiàn)。經(jīng)測試,在工作頻率為1GHz的DSP中(TMS320C6416),對SDRAM中分辨率為2048×2048的圖像進(jìn)行中值濾波后重新寫入SDRAM,耗時為7s;而在FPGA中,完全可以在圖像輸入時進(jìn)行實(shí)時處理,僅消耗幾個時鐘周期的處理,近似可認(rèn)為0延時—實(shí)時。

對于第四點(diǎn)提及的編譯時間過長的問題,Altera致力于開發(fā)新版本的平臺,提升編譯效率的同時,增加了增量編譯的功能。配合區(qū)域鎖定,可以鎖定已編譯過且在后續(xù)修改中沒有改動過的模塊,對這部分模塊不進(jìn)行重新編譯,從而可減少編譯時間。

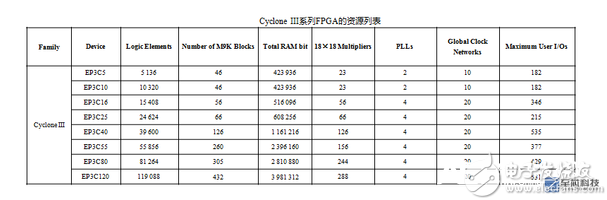

對于第五點(diǎn)提及的運(yùn)算能力的問題,Altera FPGA中內(nèi)嵌了多個DSP塊。每個DSP塊中包含加法器和乘法器結(jié)構(gòu),根據(jù)系列不同,具有不同的數(shù)據(jù)位寬。多個DSP塊中的加法器和乘法器可以互相拼接,從而支持更高位寬的運(yùn)算。結(jié)合相關(guān)的運(yùn)算類IP,可以流水線的形式完成運(yùn)算,每個周期輸出一次計(jì)算結(jié)果。表1.10為Cyclone III系列FPGA的資源列表。可以看到,與DSP相比,Cyclone III的乘法器資源還是比較豐富的,這使得在FPGA內(nèi)部進(jìn)行并行運(yùn)算成為可能。

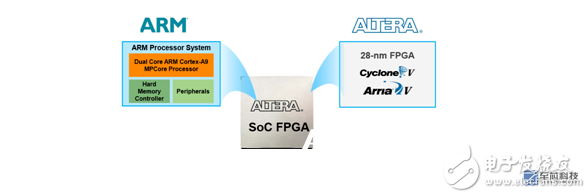

最后,Altera又推出了嵌入了雙核28nm的ARM Cortex-A9的FPGA,同時以足夠的DSP塊和足夠的乘法器資源,完善了FPGA+DSP+ARM架構(gòu),并以單片SoC FPGA的模式,解決了過往FPGA力所不能及的缺陷,解決了未來多IC集成的前瞻性問題,如圖1.28所示。而這卻僅僅只是一個開始,在未來Altera FPGA的發(fā)展中,更多的以實(shí)現(xiàn)FPGA+DSP+ARM為架構(gòu),并行實(shí)現(xiàn)高速運(yùn)算,解決過去的難題,不斷地突破極限。在未來的數(shù)字系統(tǒng)設(shè)計(jì)中,這必然是一種趨勢。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21777瀏覽量

604686 -

時序

+關(guān)注

關(guān)注

5文章

391瀏覽量

37368

發(fā)布評論請先 登錄

相關(guān)推薦

對比ARM、DSP,深入了解FPGA

對比ARM、DSP,深入了解FPGA

評論