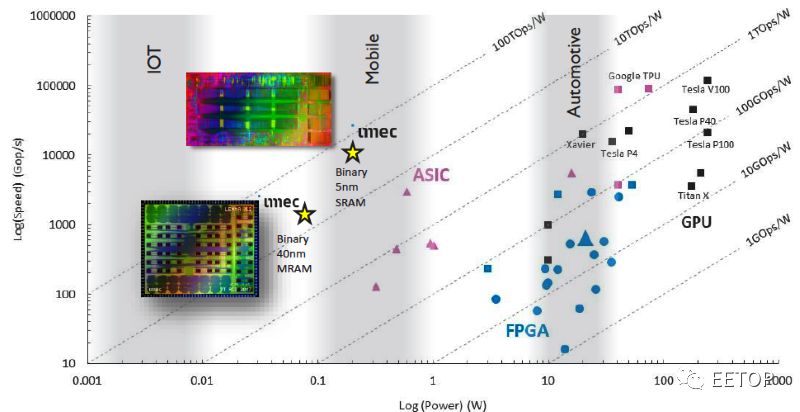

比利時研究機構Imec在近日舉行的年度技術論壇(ITF BELGIUM 2018)上透露,該機構正在打造一款采用單位元精度的深度學習推論(inference)芯片原型;Imec并期望在明年收集采用創新資料型態與架構──采用存儲器內處理器(processor-in-memory,PIM),或是Analog存儲器結構(analog memory fabric)──的客戶端裝置有效性資料。

學術界已經研究PIM架構數十年,而該架構越來越受到資料密集的機器演算法歡迎,例如新創公司Mythic以及IBM Research都有相關開發成果。許多學術研究機構正在實驗1~4位元的資料型別(data type),以減輕深度學習所需的沉重存儲器需求;到目前為止,包括Arm等公司的AI加速器商用芯片設計都集中在8位元或更大容量的資料型別,部分原因是編程工具例如Google的TensorFlow缺乏對較小資料型別的支援。

Imec擁有在一家晶圓代工廠制作的40nm制程加速器邏輯部份,而現在是要在自家晶圓廠添加一個MRAM層;該機構利用SRAM模擬此設計的性能,并且評估5nm節點的設計規則。此研究是Imec與至少兩家匿名IDM業者伙伴合作、仍在開發階段的專案,從近兩年前展開,很快制作了采用某種電阻式存儲器(ReRAM)的65nmPIM設計原型。

該65nm芯片并非鎖定深度學習演算法,雖然Imec展示了利用它啟動一段迷人的電腦合成音樂;其學習模式是利用了根據以音樂形式呈現、從感測器所串流之資料的時間序列分析(time-series analysis)。而40nm低功耗神經網路加速器(Low-Energy Neural Network Accelerator,LENNA)則會鎖定深度學習,在相對較小型的MRAM單元中運算與儲存二進位權重。

Imec技術團隊的杰出成員Diederik Verkest接受EE Times采訪時表示:「我們的任務是定義出我們應該利用新興存儲器為機器學習開發什么樣的半導體技術──或許我們會需要制程上的調整,」以取得最佳化結果。該機構半導體技術與系統部門執行副總裁An Steegen則表示:「AI會是制程技術藍圖演化的推手,因此Imec會在AI (以及PIM架構)方面下很多功夫──這方面的工作成果將會非常重要。」

Imec聲稱其LENNA芯片在推論任務上的表現將超越現有的CPU與GPU

確實,如來自英國的新創公司Graphcore執行長Nigel Toon所言,AI標志著「運算技術的根本性轉變」;該公司將于今年稍晚推出首款芯片。Toon在Imec年度技術論壇上發表專題演說時表示:「今日的硬體限制了我們,我們需要某種更靈活的方案…我們想看到能根據經驗調整的(神經網路)模型;」他舉例指出,兩年前Google實習生總共花了25萬美元電費,只為了在該公司采用傳統x86處理器或Nvidia GPU的資料中心嘗試最佳化神經網路模型。

實現復雜的折衷平衡

Imec希望LENNA能在關于PIM或Analog存儲器架構能比需要存取外部存儲器的傳統架構節省多少能量方面提供經驗;此外該機構的另一個目標,是量化采用二進制方案在精確度、成本與處理量方面的折衷(tradeoff)。

加速器芯片通常能在一些熱門的測試上提供約90%的精確度,例如ImageNet競賽;Verkest表示,單位元資料型別目前有10%左右的精度削減,「但如果你調整你的神經網路,可以達到最高85%~87%的精確度。」他原本負責督導Imec的邏輯制程微縮技術藍圖,在Apple挖腳該機構的第一個AI專案經理之后,又兼管AI專案。

Verkest表示,理論上Analog存儲器單元應該能以一系列數值來儲存權重(weights),但是「那些存儲器元件的變異性有很多需要考量之處;」他指出,Imec的開發專案將嘗試找出能提供最佳化精度、處理量與可靠度之間最佳化平衡的精度水準。

而Toon則認為聚焦于資料型別是被誤導了:「低精度并沒有某些人想得那么嚴重,存儲器存取是我們必須修正之處;」他并未詳細介紹Graphcore的解決方案,但聲稱該公司技術可提供比目前采用HBM2存儲器的最佳GPU高40倍的存儲器頻寬。

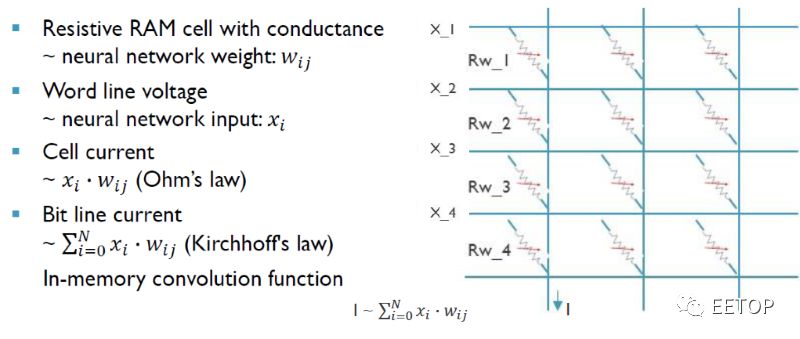

在芯片架構方面,Imec的研究人員還未決定他們是要設計PIM或采用Analog存儲器結構;后者比較像是一種Analog SoC,計算是在Analog區塊處理,可因此減少或免除數位-Analog轉換。不同種類的神經網路會有更適合的不同架構,例如卷積神經網路(CNN)會儲存與重復使用權重,通常能以傳統GPU妥善運作;歸遞神經網路(RNN)以及長短期記憶模型(long short-term memories,LSTMs)則傾向于在使用過后就拋棄權重,因此更適合運算式存儲器結構

Imec可能會以存儲器結構來打造LENNA,讓運算留在Analog功能區塊

新的平行架構非常難編程,因此大多數供應商正在嘗試建立在TensorFlow等現有架構中攝取程式碼的途徑。而Graphcore則是打造了一種名為Poplar的軟體層,旨在以C++或Python語言來完成這項工作;Toon表示:「我們把在處理器中映射圖形(graphs)的復雜性推到編譯器(也就是扮演該角色的Poplar)。」

Graphcore的客戶很快就會發現該程序會有多簡單或是多困難;這家新創公司預計在年中將第一款產品出貨給一線大客戶,預期他們會在今年底采用該款芯片執行大型云端供應商的服務。Toon聲稱,其加速器芯片將能把CNN的速度提升五至十倍,同時間采用RNN或LSTM的更復雜模型則能看到100倍的效能提升。

-

存儲器

+關注

關注

38文章

7517瀏覽量

164070 -

加速器

+關注

關注

2文章

804瀏覽量

37967 -

AI芯片

+關注

關注

17文章

1898瀏覽量

35121

原文標題:Imec等多家公司正力促AI芯片設計最佳化

文章出處:【微信號:eetop-1,微信公眾號:EETOP】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一款采用單位元精度的深度學習推論(inference)芯片原型

一款采用單位元精度的深度學習推論(inference)芯片原型

評論