第一階段:入門(mén) -> 熟練克服心理恐懼– 代碼這么寫(xiě)可以編譯通過(guò)– 下載程序不會(huì)燒毀電路板建立思維定勢(shì)– “事非經(jīng)過(guò)不知易”學(xué)會(huì)了便是“自古華山一條路”

沒(méi)用過(guò)便是“亂花漸欲迷人眼

第二階段:提高 -> 精通EDA工具——從感性認(rèn)識(shí)到理性認(rèn)識(shí)– 站在EDA工具的角度理解FPGA開(kāi)發(fā)流程EDA工具各個(gè)流程的意義,各個(gè)階段的輸入輸出EDA工具輸出的報(bào)告:Infor和warningHDL語(yǔ)言——積累設(shè)計(jì)模式– 跨時(shí)鐘域處理電路– 有限狀態(tài)機(jī)電路– 特定領(lǐng)域的數(shù)據(jù)通路電路– 片上總線(xiàn)FPGA芯片——從邏輯特性到物理特性

– 搞定時(shí)序分析和約束– 看懂RTL視圖和Technology視圖第三階段:從業(yè) -> 專(zhuān)業(yè)從產(chǎn)品需求出發(fā)認(rèn)識(shí)你的芯片– 芯片之內(nèi)深刻理解FPGA底層結(jié)構(gòu)與應(yīng)用場(chǎng)合的對(duì)應(yīng)關(guān)系– 芯片之外FPGA外圍支持電路以及高速接口FPGA與軟件接口的設(shè)計(jì)和調(diào)試做出你的產(chǎn)品– 公司業(yè)務(wù)– 項(xiàng)目流程– 領(lǐng)域知識(shí)

個(gè)人的成長(zhǎng)+成功的項(xiàng)目給剛剛從業(yè)的FPGA工程師的幾點(diǎn)忠告– 珍視你的第一份工作從工作中學(xué)習(xí),在工作中成長(zhǎng)記工作日志,寫(xiě)博客– FPGA工程師學(xué)點(diǎn)軟件,學(xué)點(diǎn)“不可綜合語(yǔ)句”數(shù)據(jù)的分析和可視化工具之間的“膠水”– 使用Linux OS腳本

免費(fèi)工具開(kāi)源精神

第二部分:FPGA開(kāi)發(fā)中的敏捷實(shí)踐FPGA開(kāi)發(fā)本質(zhì)上是敏捷的– 相對(duì)于芯片開(kāi)發(fā):靈活 + 快速 = 敏捷

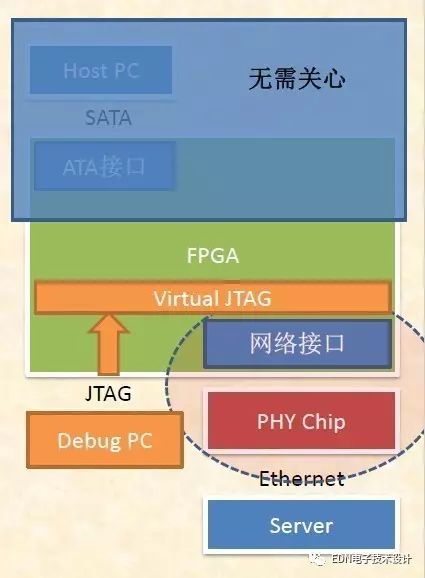

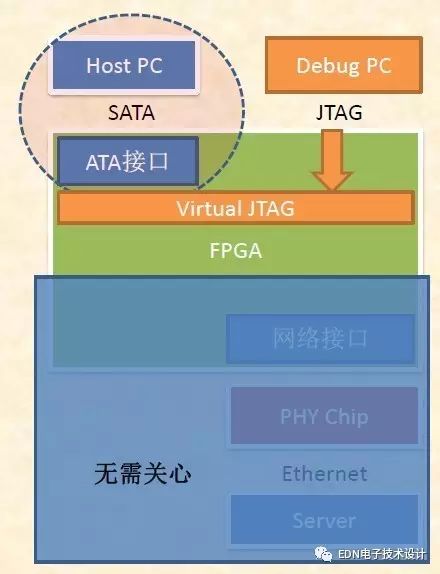

可以隨時(shí)更新– 更短的迭代周期可以上板驗(yàn)證 – 更快的反饋速度敏捷開(kāi)發(fā)的思想需要結(jié)合FPGA的自身特點(diǎn)– 相對(duì)于軟件開(kāi)發(fā):上板調(diào)試代價(jià)更高 – 仿真驗(yàn)證的必要性距離真實(shí)世界更近 – 開(kāi)發(fā)驗(yàn)證、調(diào)試工具的必要性? 驗(yàn)證、調(diào)試工具不是最終產(chǎn)品的一部分? 開(kāi)發(fā)工具、積累工具,合理重用刻意地模仿芯片或者軟件開(kāi)發(fā)都是不可取的案例分享案例一:用Virtual JTAG加速上板驗(yàn)證

– 問(wèn)題1:缺少外部芯片的仿真模型。– 解決1:用VJ虛擬出一個(gè)“串口控制臺(tái)”,通過(guò)接口邏輯層,向外部芯片發(fā)送“寫(xiě)”和“讀”命令。驗(yàn)證接口邏輯層,積累操作外部芯片的腳本。通過(guò)這一接口,把最終產(chǎn)品中需要用狀態(tài)機(jī)來(lái)實(shí)現(xiàn)的控制電路,暫時(shí)替換為可以用PC機(jī)軟件來(lái)實(shí)現(xiàn)的腳本;把FPGA上的硬件調(diào)試轉(zhuǎn)化為了PC端軟件調(diào)試,加速了調(diào)試過(guò)程。– 敏捷思想:把項(xiàng)目中的風(fēng)險(xiǎn),在早期的迭代中加以解決。

– 問(wèn)題2:外部設(shè)備行為復(fù)雜,測(cè)試向量覆蓋率不夠、仿真速度慢。– 解決2:用VJ設(shè)計(jì)一個(gè)真實(shí)行為捕獲模塊,豐富測(cè)試向量。用VJ虛擬未實(shí)現(xiàn)的關(guān)鍵邏輯模塊,上板測(cè)試調(diào)試。– 敏捷思想:反思回顧,發(fā)現(xiàn)開(kāi)發(fā)瓶頸,持續(xù)改進(jìn)方法、工具。提早集成、提早測(cè)試。案例二:FPGA開(kāi)發(fā)中引入回歸測(cè)試和持續(xù)構(gòu)建

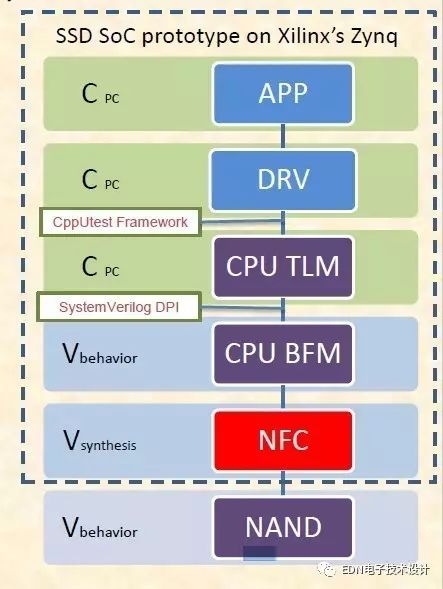

– 問(wèn)題1:軟件的驅(qū)動(dòng)層(C)和FPGA的接口層(V)需要測(cè)試和調(diào)試FPGA需要回歸測(cè)試來(lái)保證持續(xù)開(kāi)發(fā)的質(zhì)量– 解決1:用SystemVerilog DPI連接C和Verilog用CppUtest測(cè)試框架搭建FPGA回歸測(cè)試環(huán)境– 敏捷思想:回歸測(cè)試

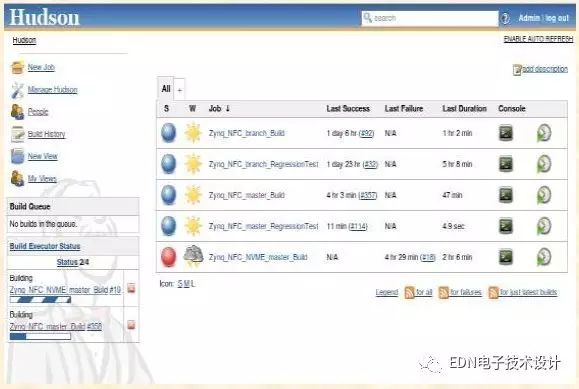

– 問(wèn)題2:多人協(xié)作開(kāi)發(fā)中代碼的質(zhì)量保證FPGA需要自動(dòng)構(gòu)建來(lái)實(shí)現(xiàn)及時(shí)發(fā)布– 解決2:用Tcl腳本實(shí)現(xiàn)項(xiàng)目編譯、仿真的自動(dòng)化用Hudson CI來(lái)實(shí)現(xiàn)多個(gè)仿真、編譯工程的自動(dòng)構(gòu)建和健康度報(bào)告– 敏捷思想:每日構(gòu)建

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603432 -

芯片

+關(guān)注

關(guān)注

455文章

50817瀏覽量

423681 -

EDA工具

+關(guān)注

關(guān)注

4文章

267瀏覽量

31794

原文標(biāo)題:如何成長(zhǎng)為一名優(yōu)秀的FPGA 工程師?

文章出處:【微信號(hào):edn-china,微信公眾號(hào):EDN電子技術(shù)設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA工程師的成長(zhǎng)軌跡分析

FPGA工程師的成長(zhǎng)軌跡分析

評(píng)論