之所以把物理層電氣部分的文章放在鏈路初始化與訓(xùn)練文章的后面,是因?yàn)檫@一部分涉及到一些相關(guān)的概念,如Beacon Signal、LTSSM等等。

前面已經(jīng)多次提及,由于本次連載的文章主要是基于Gen2的,所以關(guān)于Gen3的相關(guān)內(nèi)容只會提及,但是并不會深入的介紹,如果有興趣的可以自行閱讀Gen3的Spec。

關(guān)于鏈路初始化與訓(xùn)練的文章中提到過,PCIe Spec規(guī)定,支持新的標(biāo)準(zhǔn)的PCIe設(shè)備必須能夠向前兼容。即Gen2的設(shè)備必須同時支持2.5GT/s和5GT/s,但是,需要注意的是,Gen3的設(shè)備必須支持2.5GT/s和8GT/s,而5GT/s卻是可選的。

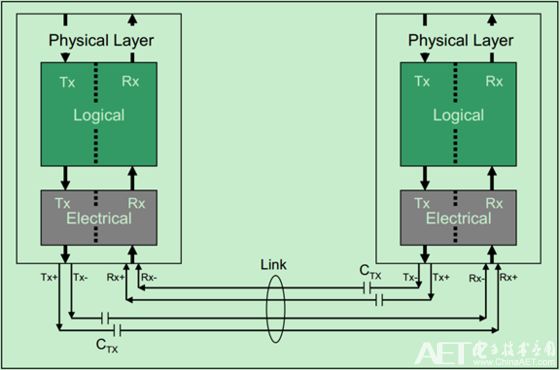

PCIe Spec規(guī)定,PCIe設(shè)備必須是Short-Circuit Tolerant的,這可以讓PCIe卡支持熱插拔的功能。此外,由于PCIe總線是一種高速的差分總線,因此,其收發(fā)兩端是交流耦合的(AC-Coupled)。一般情況下,靠近發(fā)送端的鏈路上放置電容來濾除直流信號,如下圖所示:

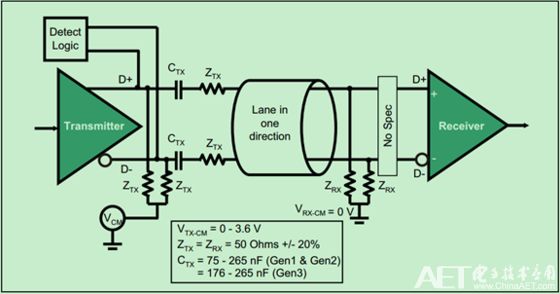

詳細(xì)的差分收發(fā)對模型如下圖所示:

當(dāng)然,如果PCIe設(shè)備把電容集成到Silicon(芯片)中,也是可以的(不過一般不會這么做,因?yàn)樵谛酒瑑?nèi)部集成大電容成本很高)。使用交流耦合的另一個優(yōu)勢是,可以允許鏈路兩端的設(shè)備使用不同的電源和地。

注:關(guān)于半導(dǎo)體中的電容,以及芯片周圍的一堆退耦電容是什么鬼,打算找個時間單獨(dú)寫一篇文章來詳細(xì)地聊一聊。

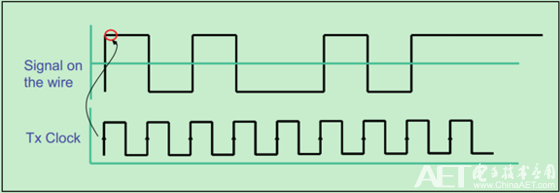

需要注意的是,PCIe總線采用的是嵌入式時鐘,即只有數(shù)據(jù)Lane,并沒有時鐘Lane(具體在前面的文章中已經(jīng)詳細(xì)地介紹過了)。也就是說,以Gen1為例,雖然2.5GT/s使用的時鐘為2.5GHz,但是從數(shù)據(jù)Lane上來看,“似乎”只有1.25GHz,如下圖所示:

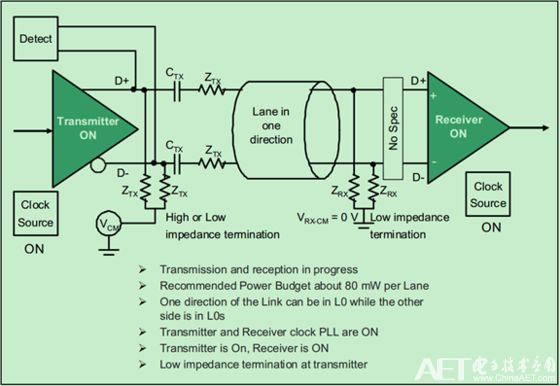

L0模式下的鏈路結(jié)構(gòu)圖(狀態(tài)圖)如下:

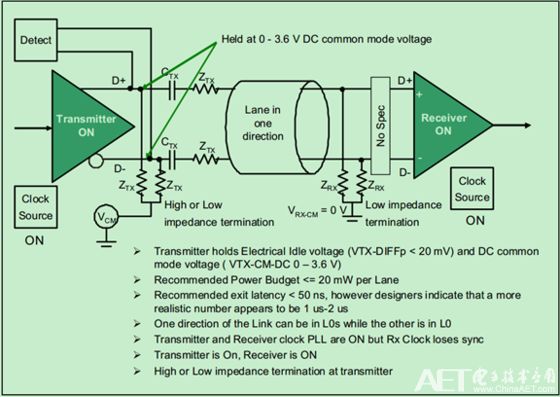

L0s模式下的鏈路結(jié)構(gòu)圖(狀態(tài)圖)如下:

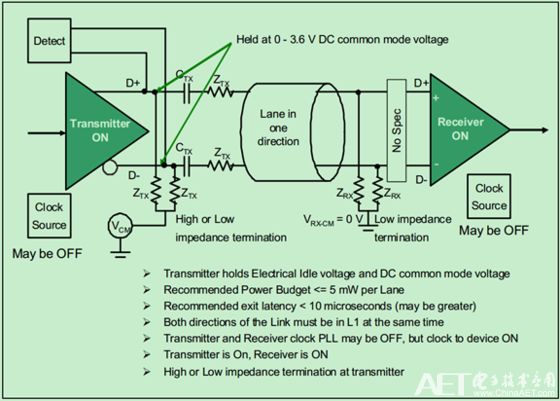

L1模式下的鏈路結(jié)構(gòu)圖(狀態(tài)圖)如下:

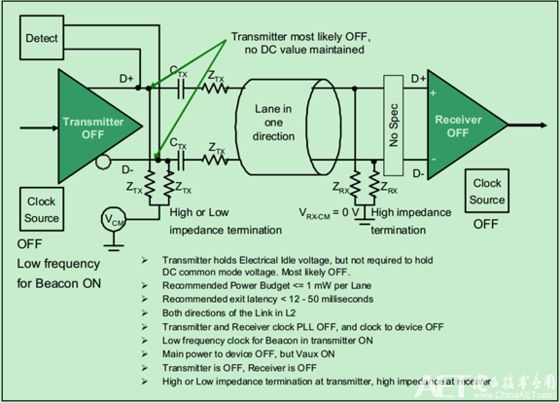

L2模式的鏈路結(jié)構(gòu)圖(狀態(tài)圖)如下:

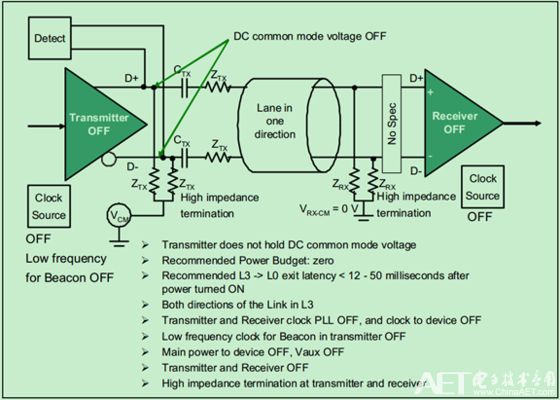

L3模式的鏈路結(jié)構(gòu)圖(狀態(tài)圖)如下:

-

芯片

+關(guān)注

關(guān)注

455文章

50816瀏覽量

423674 -

PCIe

+關(guān)注

關(guān)注

15文章

1239瀏覽量

82658 -

物理層

+關(guān)注

關(guān)注

1文章

150瀏覽量

34372

原文標(biāo)題:【博文連載】PCIe掃盲——物理層電氣部分基礎(chǔ)(一)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

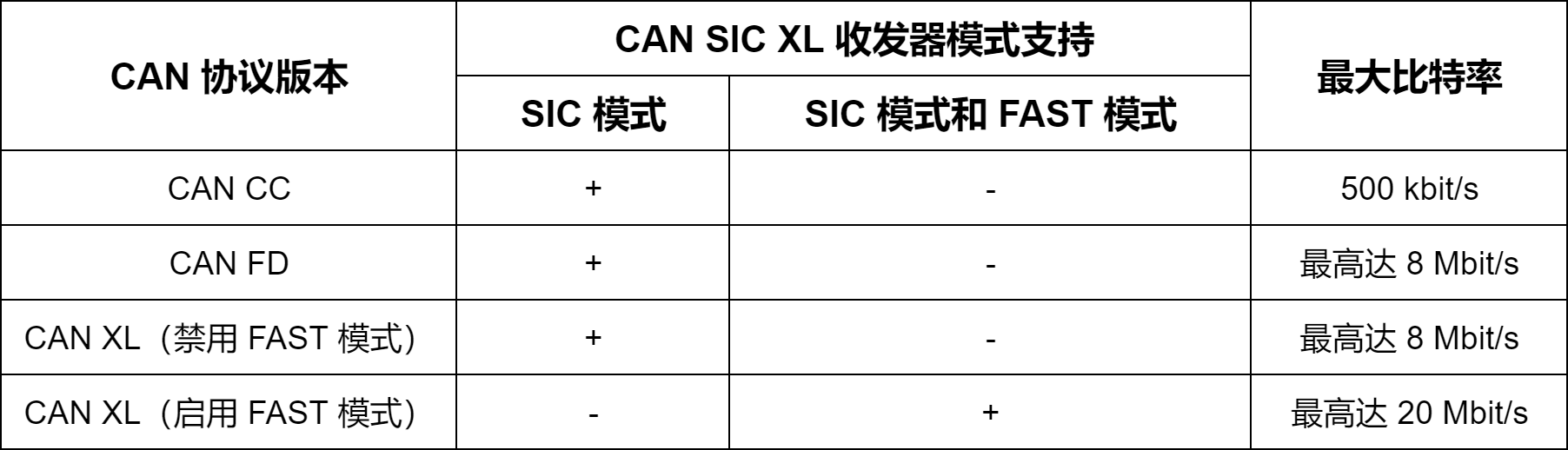

CAN總線不同的物理層

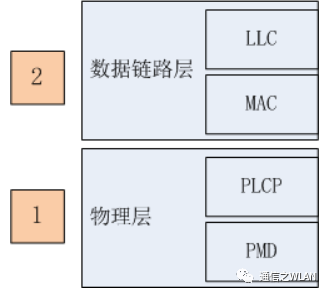

什么是以太網(wǎng)物理層?Ethernet物理層有哪些功能?

如何對CAN物理層進(jìn)行調(diào)試?

淺析串口通訊協(xié)議的物理層和協(xié)議層

IIC物理層是由哪些部分組成的

串口通信的物理層與協(xié)議層的相關(guān)資料推薦

WCDMA系統(tǒng)的物理層(FDD)

物理層 PPT課件

物理層的成幀過程

物理層的作用

PCIe物理層接口定義了物理層中的,媒介層和物理編碼子層之間的統(tǒng)一接口

WLAN物理層關(guān)鍵通信技術(shù)

CAN XL物理層揭秘(下):物理層組合與兼容性

物理層電氣部分基礎(chǔ)

物理層電氣部分基礎(chǔ)

評論