聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Altera

+關注

關注

37文章

782瀏覽量

153938 -

JESD204B

+關注

關注

5文章

76瀏覽量

19138

發布評論請先 登錄

相關推薦

jesd204b

我最近嘗試用arria 10 soc實現與ad9680之間的jesd204B協議,看了很多資料,卻依然感覺無從下手,不知道哪位大神設計過此協議,希望可以請教一番,在此先謝過。

發表于 12-13 12:47

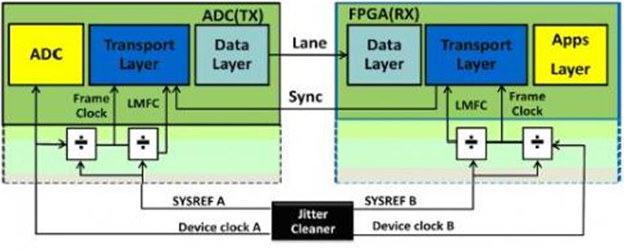

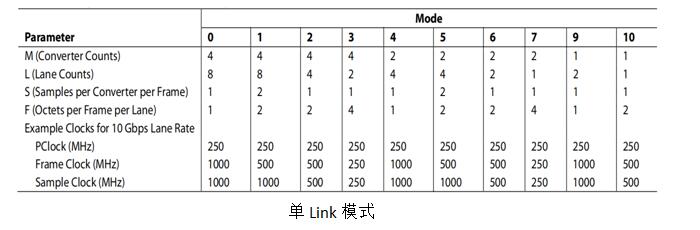

JESD204B的系統級優勢

作者:Sureena Gupta如果您有接觸使用 FPGA 的高速數據采集設計,沒準聽說過新術語“JESD204B”。我在工作中看到過很多工程師詢問有關 JESD204B 接口的信息以及它如何同

發表于 09-18 11:29

串行LVDS和JESD204B的對比

作者:George Diniz,ADI公司高速數據轉換器部產品線總監JESD204B簡介開發串行接口業界標準JESD204A的目的在于解決以高效率且省錢的方式互連最新寬帶數據轉換器與其

發表于 05-29 05:00

JESD204B串行接口時鐘的優勢

摘要 隨著數模轉換器的轉換速率越來越高,JESD204B 串行接口已經越來越多地廣泛用在數模轉換器上,其對器件時鐘和同步時鐘之間的時序關系有著嚴格需求。本文就重點講解了JESD204B 數模轉換器

發表于 06-19 05:00

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

的模數轉換器(ADC)和數模轉換器(DAC)支持最新的JESD204B串行接口標準,出現了FPGA與這些模擬產品的最佳接口方式問題。FPGA一直支持千兆串行/解串(SERDES)收發器。然而在過去,大多數ADC

發表于 04-06 09:46

JESD204B協議介紹

在使用我們的最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。此外,我還在 E2E 上的該

發表于 11-21 07:02

JESD204B的優勢

如果您有接觸使用 FPGA 的高速數據采集設計,沒準聽說過新術語“JESD204B”。我在工作中看到過很多工程師詢問有關 JESD204B 接口的信息以及它如何同 FPGA 協作。他們特別感興趣

發表于 11-23 06:35

JESD204B標準及演進歷程

在從事高速數據擷取設計時使用FPGA的人大概都聽過新JEDEC標準「JESD204B」的名號。近期許多工程師均聯絡德州儀器,希望進一步了解 JESD204B 接口,包括與FPGA如何互動、JE

發表于 11-18 02:57

?1.4w次閱讀

Validating ADI Converters Inter-operability with Xilinx FPGA and JESD204B/C IP

Validating ADI Converters Inter-operability with Xilinx FPGA and JESD204B/C IP

發表于 02-19 16:05

?11次下載

JESD204B時鐘網絡原理概述

明德揚的JESD204B采集卡項目綜合上板后,可以使用上位機通過千兆網來配置AD9144和AD9516板卡,實現高速ad采集。最終可以在示波器和上位機上采集到設定頻率的正弦波。本文重點介紹JESD204B時鐘網絡。

使用JESD204B接口的AD9144高速DA轉換模塊參數設定(私人總結版)

本文為明德揚原創文章,轉載請注明出處! 由于AD9144是高速DA轉換模塊,轉換速率可以達到2.5G,可以滿足普通的DA數據接口。為了匹配高速AD/DA轉換,JESD204B接口就應運

JESD204B使用說明

能力更強,布線數量更少。 本篇的內容基于jesd204b接口的ADC和FPGA的硬件板卡,通過調用jesd204b ip核來一步步在FPGA內部實現高速ADC數據采集,jesd204b

簡述Arria10接口JESD204B的與ADI9144性能

簡述Arria10接口JESD204B的與ADI9144性能

評論