嵌入式系統開發人員一直在想方設法進一步縮短開發時間,特別是針對概念驗證和快速原型開發。雖然開發套件已成為捷徑之選,但設計人員需要找到一個平衡點,既兼顧外形尺寸和廣受支持的生態系統,又要考慮性能要求。

Arduino Uno 開發板就是這種需要找到平衡點的很好例子。由于成本低廉,并在理論上具有數百個可提供 Arduino I/O 插件擴展功能的 Arduino 盾板,其外形尺寸在這一領域極其流行。但是,針對特定嵌入式應用,某些開發人員可能需要比 8 位微控制器所能提供的更高性能。

對于他們來說,Crowd Supply 的 HiFive1 開發套件可能才是解決方案。本文將介紹低成本的 HiFive1 開發套件,討論如何通過其功能實現高性能嵌入式系統的快速原型開發。此外,本文將介紹幫助設計人員入門的可用開發工具。

什么是 HiFive1?

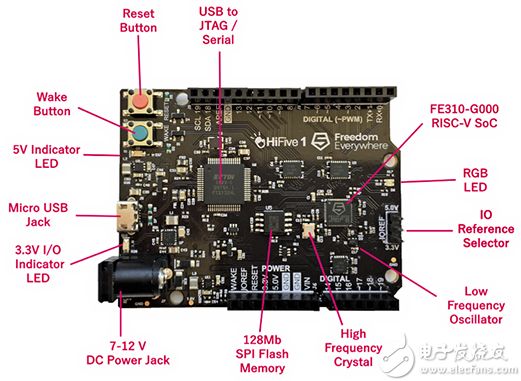

HiFive1 開發套件基于一款集成 32 位 RISC-V(讀音“risk-five”)處理器內核的微控制器(圖 1)。該開發板可接受 Arduino 式盾板,從而大幅提升了其對嵌入式設計快速原型開發的實用性。

圖 1:HiFive1 Arduino 兼容開發板使用一個基于 32 位 RISC-V 處理器內核的微控制器。(圖片來源:SiFive)

HiFive1 的核心是 RISC-V 處理器內核。這就需要 Arduino 開發板背后的開源概念,并將其一直擴展到處理器本身。RISC-V 是開放式指令集架構 (ISA),基于兩個基礎:自 20 世紀 80 年代以來一直采用的精簡指令集計算 (RISC) 概念,以及開源原則。因為 RISC-V ISA 是開源的,所以可自由地用于任何目的。任何人都可以設計、制造和銷售基于 RISC-V 的芯片和軟件,而無需支付版稅。

HiFive1 板上基于 RISC-V 的微控制器可通過編程支持芯片內執行 (XIP) 模式,以便在指令高速緩存重新填充期間降低 SPI 指令執行時間。微控制器的四路 SPI (QSPI) 端口支持 32 字節猝發讀取,使用存儲器的 XIP 模式,加快來自 QSPI 閃存的指令高速緩存重新填充,進而提升性能。

微控制器可在高于 320 MHz 的時鐘速率下運行,但在 HiFive1 板上,應限制時鐘速率不高于 133 MHz,以便保持微控制器的 SPI 串行時鐘在開發板的 128 Mbit QSPI 閃存限制范圍內工作。

Arduino 式針座(包含注意事項)

HiFive1 開發套件復制了 Arduino 獨特的 I/O 針座布局。它可以接受數以百計可用 Arduino 盾板中的多數類型,但有幾點需要注意。

首先,微控制器沒有模擬輸入引腳。HiFive1 開發套件的 Arduino 式針座只能進行數字 I/O、中斷和脈沖寬度調制 (PWM) 引腳分配。Arduino Uno 開發板上 A0 至 A5 模擬引腳所用的物理針座位置在 HiFive1 開發板上標注為 D14 至 D19 數字 I/O 引腳。如果有必要添加模擬功能,可使用眾多可用模數轉換器 (ADC)、數模轉換器 (DAC) 或組合 ADC/DAC Arduino 盾板中的一種。

另請注意:

-

設計人員可將多達 9 個 PWM 發生器分配到 HiFive1 開發套件上的 Arduino 式針座引腳。

-

HiFive1 開發套件的所有 19 個 Arduino 式針座 I/O 引腳均可用作中斷輸入。

板載電壓轉換器可根據跳線設置,靈活地將所有 HiFive1 開發套件的數字 I/O 引腳設置為 3.3 V 或 5 V 邏輯電平。單跳線設置(圖 1 開發板上帶 IOREF 標志)可定義 HiFive1 開發套件的 Arduino 式針座上所有 I/O 引腳的邏輯電平。

這就引出了第二個注意事項:迄今為止,只有以下兩款 Adafruit Arduino 盾板通過了 HiFive1 測試,因為只有針對這兩款盾板的 Adafruit 支持庫已移植到 HiFive1 庫:

-

Adafruit 的 BLE SPI Friend

即便如此,盡管支持庫可能需要微調,但任何與 SPI、UART 或數字 I/O 通信的盾板都應該易于搭配 HiFive1 使用。HiFive1 外設盾板支持庫還處于初期階段:預計支持的盾板數量會增加。

好硬件需要好軟件支持

GitHub 上提供了針對 HiFive1 開發套件的軟件開發工具。這些工具包括用于 RISC-V 處理器架構的 C 編譯器和匯編器、用于 RISC-V 處理器的 GDB 主機駐留調試器和 OpenOCD(片上調試器)的 RISC-V 版本。

一旦程序被編寫、編譯和匯編,開發人員就可以通過 USB 調試接口將其上傳到 HiFive1 開發套件。HiFive1 將該程序存儲在其板載 SPI 閃存芯片中。板載閃存芯片的容量為 16 Mb,比 8 位 Arduino Uno 板上的代碼存儲容量大得多。地址空間擴展只是諸如 RISC-V 的 32 位處理器架構的眾多優點之一。該微控制器的片上 16 Kb SRAM 也相對較大。

處于開發板核心地位的芯片

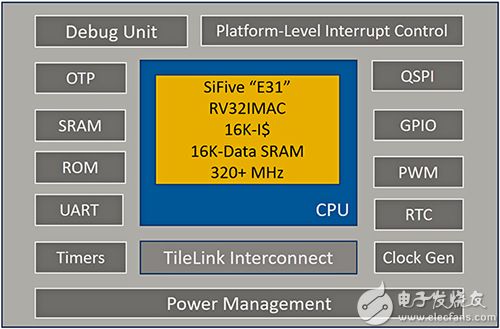

接下來將詳細介紹 HiFive1 開發套件的核心,即微控制器(圖 2)。

圖 2:基于 RISC-V 的開源微控制器的簡化框圖。(圖片來源:SiFive)

該微控制器的中心是基于開源的 32 位 RISC-V ISA 的 CPU 內核。就 RISC-V 而言,核心是 RV32IMAC 處理器,這意味著它使用的是基本 32 位 RISC-V 整數指令集 (RV32I),具有整數硬件乘除 (M) ;原子、實時指令 (A);以及對 16 位精簡 (C) 指令集的附加支持。另外還有 64 位和 128 位版本的 RISC-V ISA。該內核還包括 16 Kb 的指令緩存(在框圖中標記為“I $”)和 16 Kb 的暫存器 SRAM。幾個標準外設包括定時器、PWM 信號發生器、實時時鐘、UART、QSPI 串行接口以及圍繞處理器內核的一個片上硬件調試模塊。

RISC-V 架構幕后有誰或者說有什么?為什么?

HiFive1 開發套件和微控制器實際上是開源 RISC-V 處理器架構的硬件演示工具,是一個假設論證:世界真的需要另一種處理器架構嗎?

RISC-V 項目始于加州大學伯克利分校,最終超越了大學研究的范疇,充分發揮了更多自愿參與者和電子行業人士的想象力。該項目的最終結果是開源代碼 RISC 處理器 ISA(指令集架構),與其他任何 32 位 RISC ISA 幾乎一樣。不同之處在于任何人都可以自由地將 RISC-V ISA 用于任何目的。

它需要一個生態系統

就 HiFive1 開發板而言,嵌入式系統開發人員需要的不僅僅是處理器或微控制器芯片。對于 RISC-V,嵌入式開發人員需要工具、示例代碼、庫和軟件堆棧等形式的開發支持。這類支持來自圍繞成功的處理器架構和用戶而發展的生態系統。RISC-V 處理器架構相對較新,其生態系統也一樣,但它在不斷發展。除了上面討論的 SiFive 開發工具外,RISC-V 生態系統中的其他開發工具目前還包括:

總結

經濟實惠的 Arduino Uno 開發板外形小巧輕便,可訪問數百個 I/O 和外設盾板。HiFive1 開發套件利用這些現有盾板,通過緊密復制緊湊型 Arduino Uno 開發板的外形尺寸和獨特針座配置,將其與基于 RISC-V 的 32 位微控制器配接。

HiFive1 開發套件具有 16 Mb 板載閃存,可提供更高的代碼存儲能力。盡管它是一款新的架構,但嶄露頭角的開源 RISC-V 生態系統提供了一套擴展的軟件開發工具,包括編譯器、匯編器、調試器和 Arduino IDE 庫。

-

嵌入式

+關注

關注

5091文章

19176瀏覽量

307187 -

Arduino

+關注

關注

188文章

6477瀏覽量

187690

發布評論請先 登錄

相關推薦

為加速原型開發,ADI推出FPGA夾層卡快速原型開發套件

萊迪思MachXO2套件:專用原型開發套件

恩智浦推快速物聯網原型套件 可加速PoC開發進程

什么是HiFive1?詳細介紹HiFive1開發套件的核心

如何通過HiFive1套件實現快速原型開發

如何通過HiFive1套件實現快速原型開發

評論