一個故事理解流水線、并行、緩存、內存、存儲

蛋蛋花了一天給小蛋蛋做了一個玩具汽車,沒想到做的太好了,同學們都來買。蛋蛋一個人忙不過來,就一家人合作生產。蛋蛋負責把原料分類擺放在桌上,小蛋蛋擰螺絲組裝,蛋媽把玩具放到包裝盒里。三個人采用流水線的方式,每個人都沒閑著,生產效率大為提高,一天能造50個玩具。

隔壁老王看到蛋蛋做玩具賺錢了,也一家三口加入造玩具大軍,慢慢整個小區家家冒煙,戶戶生產。五十家人采用并行工作的方式,一天能造2500個玩具。

本來,蛋蛋家里的工作臺旁邊有個箱子,叫做緩存。把玩具生產的原料和生產好的玩具放在自己家里,離得又近又速度快。

小區里家家冒煙后,原料供應和玩具運輸需求量大增。居民們在小區中央建了一個倉庫,叫做內存,里面放了很多原料和玩具,看門大爺每天推著手推車到每家每戶去送原料,收玩具,人們給他起了個外號——總線。

鎮長看到蛋蛋家園小區交的玩具稅日漸增長,為了增加收入,決定建設玩具小鎮,于是鎮上每個小區都開始生產玩具,玩具生產規模日漸擴大。鎮中心建了一個大倉庫,集中存放原料和玩具,倉庫太大了,如果一個個領取太不方便,所以每次提貨或者送貨必須以500個為單位批量領取,這個大倉庫叫做硬盤。

在我們的計算機中,CPU采用流水線的方式工作,把一個任務分成十幾個步驟,用十幾級流水線計算,速度增長了十幾倍。多核CPU就是并行工作,又能把計算速度提升幾倍。計算速度快了之后,對數據的讀寫速度要求變高,所以,現代CPU設計了先進的緩存系統,可以說,對現代通用CPU來說,緩存才是核心。

可是對某些應用來說,CPU有點走歪了,它擅長的是用高頻率把順序執行的任務分解成很多級流水線高速執行,但是對于深度學習等計算,需要的是大量的并行計算,這時候,CPU的核心數成了限制。

FPGA的并行性

蛋蛋設計了一個復雜的機器叫CPU,它能一條條讀取并執行蛋蛋寫好的指令,把任務分解成很多級流水線,生產出各種各樣復雜的玩具。

玩具市場總是有新的流行風尚,最近突然樂高玩具開始大火,每一個積木都長得差不多,但是很多的積木就可以搭出復雜的形狀。現在的家長都希望寓教于玩,讓孩子玩游戲也能動腦筋,蛋蛋看到了這個趨勢,也想生產樂高積木。可是他發現復雜的機器CPU的生產效率太低了,他需要的是同時大批量幾百上千個機器并行生產,而CPU最多只能同時生產十幾個。所以,蛋蛋又鉆研了一段時間,研制出新的機器——FPGA。這臺機器里面有幾千個小引擎,按照蛋蛋設定好的任務,大家熱火朝天地生產自己的小積木。

我們上大學學習的C語言是給CPU編程的語言,它的特點就是寫一個main函數,里面有很多內容,程序啟動后,從頭按順序執行到結尾。這是因為只有一個CPU在運行,程序會轉化為指令讓CPU一條條執行。

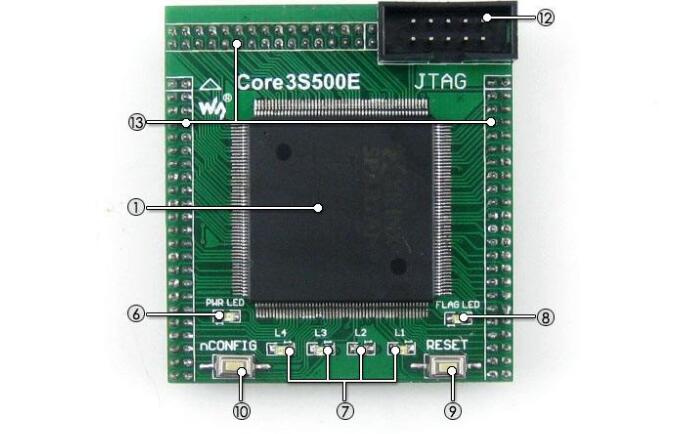

FPGA是并行計算機,它的基礎編程語言叫做Verilog,在這種語言中,每一段程序,都會轉化為FPGA芯片里面的一個小計算引擎,大家并行執行,熱火朝天的干自己的活。

FPGA和CPU如何搭配

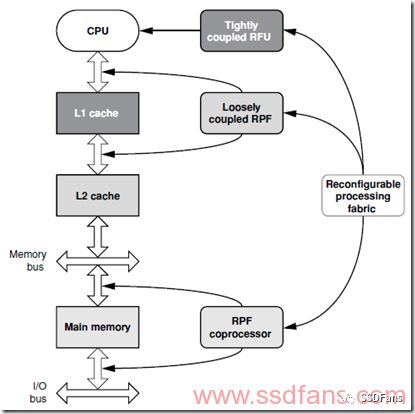

FPGA作為可重構計算引擎,一般要和CPU搭配使用。如下圖,可重構計算引擎要么直接和CPU緊密相連,要么和緩存相連,前者叫緊耦合,后者叫松耦合。還有一種情況下,FPGA是作為協處理器coprocessor連到內存總線上,和CPU共享內存。

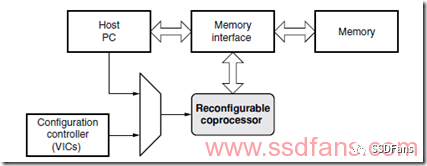

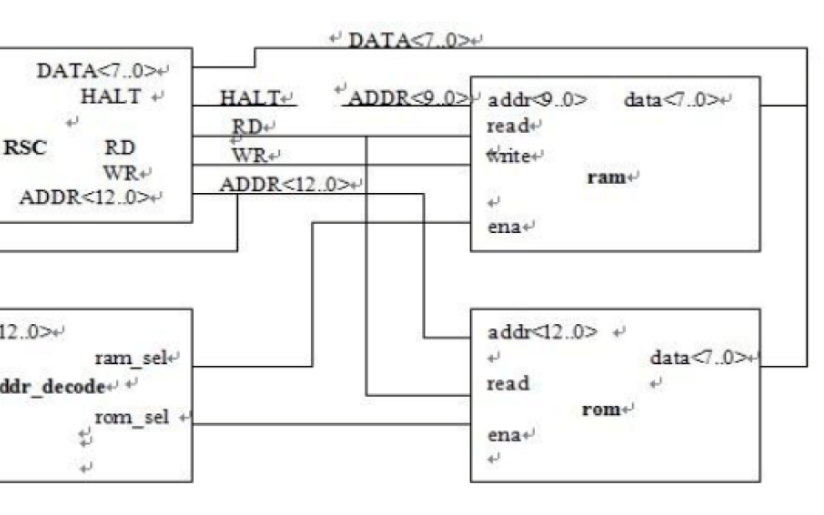

如下圖,FPGA作為協處理器,CPU把指令寫入內存,FPGA從內存讀取指令執行,并把計算結果寫入內存。這種模式的優點是簡單易行,協處理器和CPU分離。瓶頸在于共享內存,限制了性能,同時由于通過內存交互,CPU和FPGA之間通信延遲變長了。所以適合于FPGA能獨立執行的加速任務,比如視頻編解碼、數據加解密等。

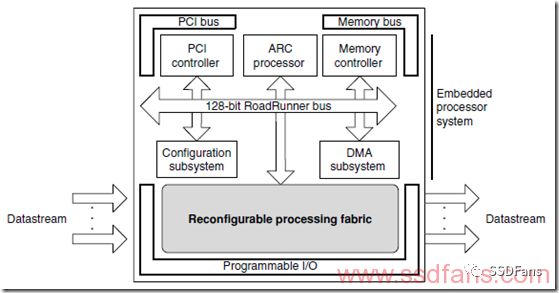

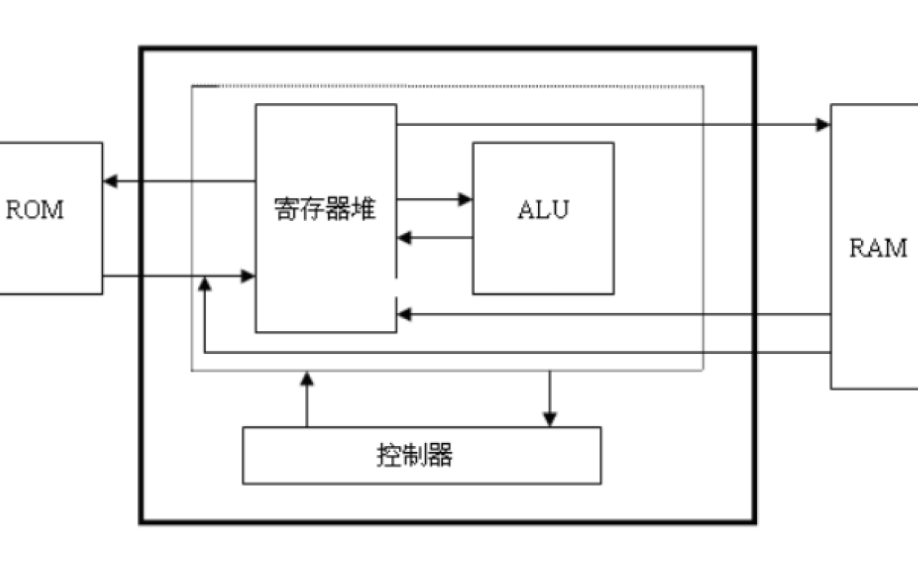

下圖是一個松耦合的例子。CPU(ARC)和可重構計算邏輯放在一顆芯片里面,CPU可以直接訪問可重構計算引擎,而且共享內存,可重構計算引擎可以通過DMA方式直接讀寫內存。同時,我們看到可重構計算引擎有自己的數據讀寫接口,所以可以脫離CPU獨立工作,打工創業兩不誤。

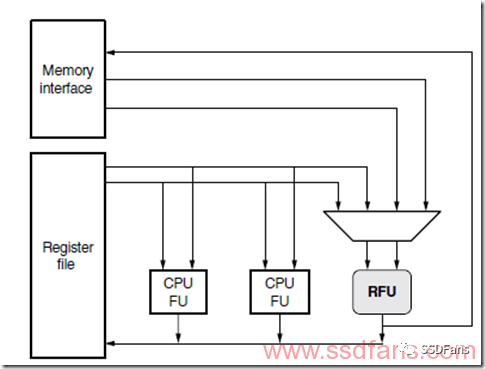

再來看一個緊耦合的例子。如下圖,CPU FU是一般CPU的基本計算單元,例如ALU、乘法器、浮點處理器等,RFU跟這些基本單元一樣,放在芯片里面,而且可以直接被CPU的寄存器控制,還能訪問緩存中的數據。

總結一下,協處理器相當于外地當官的,只能接受皇帝的命令工作。松耦合就是京城里的官員,可以定期去皇宮跟皇帝嘮嘮嗑。緊耦合已經到了外戚和太監的地步,能在皇宮里經常值班。

松耦合和緊耦合都要在芯片里面放可重構計算引擎,成本比較高,但是效率也很高。相當于CPU里面有個FPGA,隨時可以編程讓它做不同的計算。處理視頻時,配置成視頻編解碼邏輯,做AI計算時配置成深度學習計算器,一個芯片既有CPU,又有可以配置的硬件計算引擎。

-

FPGA

+關注

關注

1629文章

21742瀏覽量

603538 -

cpu

+關注

關注

68文章

10868瀏覽量

211844 -

深度學習

+關注

關注

73文章

5503瀏覽量

121182

原文標題:阿呆讀可重構計算2:FPGA如何克服CPU的缺陷?

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA真的能取代CPU和GPU嗎?

一種利用FPGA的CPU設計

基于FPGA的嵌入式CPU的VHDL建模和設計

FPGA、CPU、DSP的競爭與融合

三步教你如何DIY電腦主板和CPU的搭配

簡單了解CPU和內存搭配規律

FPGA為什么比CPU和GPU快

如何才能合理的搭配CPU和主板

使用FPGA實現CPU設計的畢業論文總結

如何使用CPU配置FPGA的詳細資料說明

如何使用FPGA實現八位RISC CPU的設計

FPGA和CPU如何搭配?

FPGA和CPU如何搭配?

評論