在超深亞微米工藝節點創新方面已合作多年的 Arm與三星代工廠宣布雙方合作之旅的新里程碑:為期待已久的極紫外 (EUV)光刻技術,提供首款 7LPP (7nm Low Power Plus)和5LPE (5nm Low Power Early)庫面市。這是 Arm與三星代工廠12 年成功合作旅程的最新成果,雙方從 65nm工藝開始不斷推出新技術和產品庫,利用Arm獨特的IP集成能力,三星代工廠可使用Arm物理和處理器IP驗證其最頂級節點的設計就緒狀態。

三星代工廠的EUV特性和優點

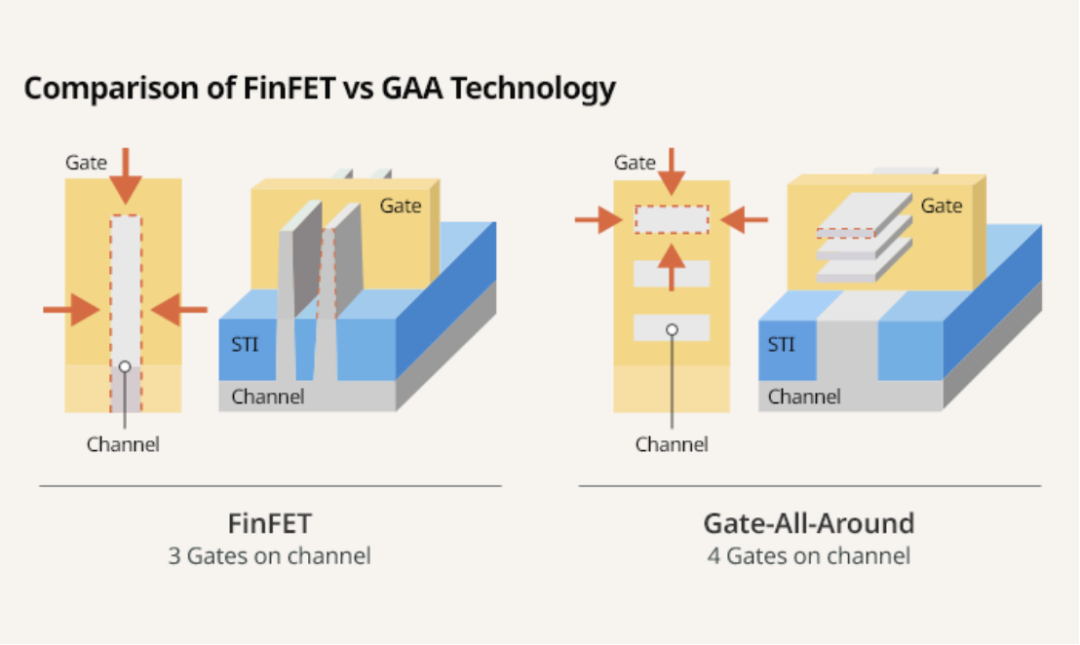

EUV是芯片設計的重要變革。它可降低7nm設計實施的復雜性。制造商可將三個或四個光刻層變為一個光刻層,并將多個圖層變成單個圖層,從而大大縮短處理周期時間,縮小芯片尺寸。此外,由于采用比多色圖層更嚴格的設計規則,EUV還可實現更緊湊的布局。

三星代工廠最新的 7LPP EUV制造工藝采用高能EUV光源生產具有超精細設備特性的芯片,臨界尺寸只有7nm。作為對比,常見的病毒細胞為10nm寬,微觀DNA鏈的寬度約為2.5nm,而一個硅原子的寬度略低于1nm。

“三星電子市場營銷副總裁 Ryan Lee表示:“7LPP和5LPE工藝技術可實現EUV光科技術的優勢, 同時降低這些先進技術節點的布局復雜性和設計開發時間。通過在開發初期與Arm合作,并借助各種設計技術聯合優化技巧 ,我們優化了制造和設計流程。針對7LPP和5LPE的Arm Artisan IP基礎平臺就是建立在這種合作之上的,客戶能夠提前獲取我們針對下一代設計的差異化EUV解決方案。”

除了這一先進技術之外,三星最近還推出了SAFE?(三星高級代工廠生態系統)計劃,以期提供全面的設計解決方案。Arm是SAFE? 計劃的戰略成員之一,為生態系統和客戶提供領先的聯合優化物理IP解決方案,以期增強下一代SoC設計。

基于三星7LPP的物理IP平臺概述

三星代工廠在市場上率先使用 7nm EUV工藝。由三星代工廠贊助的Arm Artisan物理IP綜合平臺將于今年年底開始供貨。Arm正在開發HD邏輯架構、全套內存編譯器、1.8V和3.3V GPIO庫,同時還針對我們的最新處理器內核提供采用DynamIQ技術的POP IP解決方案。POP IP是一項核心硬件加速技術,可以實現最佳Arm處理器的生產,在最短的時間內上市。

該平臺將于 2018年下半年可以提供我們的主要客戶進行設計。針對 7LPP的Arm Artisan物理IP用于支持低電壓運行,以便存儲器和位單元能夠在低至0.55V的電壓條件下運行。

基于三星5LPE的物理IP平臺概述

除了 7LPP EUV,三星代工廠還利用EUV優勢和其他面積優勢設計了首款5LPE。5LPE節點不僅具有面積優勢,還可實現輕松布局,這是最大的EUV優勢。

除了全套內存編譯器和 GPIO庫,Arm還在開發另一個適用于5LPE的UHD邏輯架構。我們的平臺產品中還將添加其他適用于下一代高級內核的POP IP產品,包括對Arm big.LITTLE配置的支持。

Arm Artisan IP供貨

Arm 7LPP物理IP平臺將從2018年第3季度開始供貨,面向移動、消費、高性能計算和汽車領域的主要客戶設計。5LPE物理IP平臺產品將于2019年年初開始供貨。更多信息,請聯系 Arm物理設計部門或點擊“閱讀原文”訪問Arm物理 IP頁面。

-

ARM

+關注

關注

134文章

9105瀏覽量

367911 -

三星電子

+關注

關注

34文章

15865瀏覽量

181065 -

7nm

+關注

關注

0文章

267瀏覽量

35342

原文標題:再攜手推進7nm與先進工藝

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三星芯片代工新掌門:先進與成熟制程并重

三星加速2nm及1.4nm制程投資

所謂的7nm芯片上沒有一個圖形是7nm的

三星奪得首個2nm芯片代工大單,加速AI芯片制造競賽

三星否認晶圓代工廠生產缺陷傳聞

概倫電子NanoSpice通過三星代工廠3/4nm工藝技術認證

臺積電3nm工藝穩坐釣魚臺,三星因良率問題遇冷

三星展望2027年:1.4nm工藝與先進供電技術登場

三星與新思科技攜手,備戰2nm工藝量產

任天堂Switch 2將大幅依靠三星供應鏈

2024年全球與中國7nm智能座艙芯片行業總體規模、主要企業國內外市場占有率及排名

三星攜手高通共探2nm工藝新紀元,為芯片技術樹立新標桿

三星電子宣布擴大與Arm合作

無意發展至10nm以下,第二梯隊晶圓代工廠的成熟工藝現狀

Arm和三星代工廠攜手推進7nm先進工藝

Arm和三星代工廠攜手推進7nm先進工藝

評論