現在,SSD已經大跨步邁入PCIe時代。作為SSD的一項重要技術,我們有必要對PCIe有個基本的了解。

那為什么SSD要用PCIe接口?因為它快,比SATA快。它究竟有多快?我們首先從PCIe接口的速度開始我們的PCIe之旅。

PCIe發展到現在,從PCIe 1.0,PCIe 2.0,到現在的PCIe 3.0,速度一代比一代快。

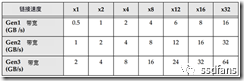

圖1-1 PCIe各代的帶寬

2017年PCIe 4.0已經發布,但本章內容僅限于PCIe 3.0及更早版本。

鏈接速度這一行,我們看到x1,x2,x4,….,這是什么意思?這是指PCIe連接的通道數(Lane)。就像高速一樣,有單根道,有2根道的,有4根道的,不過像8根道或者更多道的公路不常見,但PCIe是可以最多32個Lane的。

圖1-2 PCIe Lane類比高速公路通道

兩個設備之間的PCIe連接,叫做一個Link,如圖所示

圖1-3 PCIe Link的概念

從A到B,之間是個雙向連接,車可以從A駛向B,同時,車也可以從B駛向A,各行其道。兩個PCIe設備之間,有專門的發送和接收通道,數據可以同時往兩個方向傳輸,PCIe spec稱這種工作模式為雙單工模式(Dual-Simplex),可以理解為全雙工模式。

SATA是什么工作模式呢?

圖1-4 SATA 工作模式

和PCIe一樣,SATA也有獨立的發送和接收通道,但與PCIe工作模式不一樣:同一時間,只有一條道可以進行數據傳輸,也就是說,你在一條道上發送數據,另外一條道上不能接收數據,反之亦然。這種工作模式是半雙工模式。

PCIe猶如我們的手機,雙方可以同時講話,而SATA就是對講機了,一個人在說話,另外一個人就只能聽不能說。

回到前面PCIe帶寬那張表,上面的帶寬,比如PCIe3.0x1,帶寬為2GB/s,是指雙向帶寬,即讀寫帶寬。如果單指讀或者寫,該值應該減半,即1GB/s的讀速度或者寫速度。

我們來看看表里面的帶寬是怎么算出來的。

PCIe是串行總線,PCIe1.0的線上比特傳輸速率為2.5Gb/s,物理層使用8/10編碼,即8比特的數據,實際在物理線路上是需要傳輸10比特的,多余的2比特用來校驗。因此:

PCIe1.0 x 1的帶寬=(2.5Gb/s x 2(雙向通道))/ 10bit = 0.5GB/s

這是單條Lane的帶寬,有幾條Lane,那么整個帶寬計算就是用0.5GB/s乘以Lane的數目。

PCIe2.0的線上比特傳輸速率在PCIe1.0的基礎上翻了一倍,為5Gb/s,物理層同樣使用8/10編碼,所以:

PCIe2.0 x 1的帶寬=(5Gb/s x 2(雙向通道))/ 10bit = 1GB/s

同樣,有多少條Lane,帶寬就是1GB/s乘以Lane的數目。

PCIe3.0的線上比特傳輸速率沒有在PCIe2.0的基礎上翻倍,不是10Gb/s,而是8Gb/s,但物理層使用的是128/130編碼進行數據傳輸,所以:

PCIe3.0 x 1的帶寬=(8Gb/s x 2(雙向通道)x(128 bit/130 bit))/ 8bit ≈ 2GB/s

同樣,有多少條Lane,帶寬就是2GB/s乘以Lane的數目。

由于采用了128/130編碼,128比特的數據,只額外增加了2bit的開銷,有效數據傳輸比率增大,雖然線上比特傳輸率沒有翻倍,但有效數據帶寬還是在PCIe2.0的基礎上做到翻倍。

這里值得一提的是,上面算出的數據帶寬已經考慮到8/10或者128/130編碼,因此,大家在算帶寬的時候,沒有必要再考慮線上編碼的問題了。

和SATA單通道不同,PCIe連接可以通過增加通道數擴展帶寬,彈性十足。通道數越多,速度越快。不過,通道數越多,成本越高,占用更多空間,還有就是更耗電。因此,使用多少通道,應該在性能和其他因素之間進行一個綜合考慮。單考慮性能的話,PCIe最高帶寬可達64GB/s,即PCIe 3.0 x 32對應的帶寬,很恐怖的一個數據。不過,現有的PCIe SSD,一般最多使用4通道,如PCIe3.0x4,雙向帶寬為8GB/s,讀或者寫帶寬為4GB/s。

幾個GB/s的傳輸速度,看起小電影來那是杠杠的。

在此,順便來算算PCIe3.0x4理論上最大的4K IOPS。PCIe3.0x4理論最大讀或者寫的速度為4GB/s,不考慮協議開銷,每秒可以傳輸4GB/4K個4K大小的IO,該值為1M,即理論上最大IOPS為1000K。因此,一個SSD,不管你底層用什么介質,閃存還是3D XPoint,接口速度就這么快,最大IOPS是不可能超過這個值的。

PCIe是從PCI發展過來的,PCIe的”e”是express的簡稱,快的意思。PCIe怎么就能比PCI(或者PCI-X)快呢?PCIe在物理傳輸上,跟PCI有著本質的區別:PCI使用并口傳輸數據,而PCIe使用的是串口傳輸。我PCI并行總線,單個時鐘周期可以傳輸32bit或者64bit,怎么就比不了你單個時鐘周期傳輸1個bit數據的串行總線呢?

腿長的姚明為什么跑不過腿短的劉翔?因為劉翔腳步頻率更快。

在實際時鐘頻率比較低的情況下,并口因為可以同時傳輸若干比特,速率確實比串口快。隨著技術的發展,數據傳輸速率要求越來越快,要求時鐘頻率也越來越快,但是,并行總線時鐘頻率不是想快就能快的。

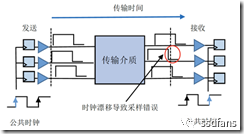

圖1-6 并行傳輸時序

在發送端,數據在某個時鐘沿傳出去(左邊時鐘第一個上升沿),在接收端,數據在下個時鐘沿(右邊時鐘第二個上升沿)接收。因此,要在接收端能正確采集到數據,要求時鐘的周期必須大于數據傳輸的時間(從發送端到接收端,flight time)。受限于數據傳輸時間(該時間還隨著數據線長度的增加而增加),因此時鐘頻率不能做得太高。另外,時鐘信號在線上傳輸的時候,也會存在相位偏移(Clock Skew ),影響接收端的數據采集;還有,并行傳輸,接收端必須等最慢的那個bit數據到了以后,才能鎖住整個數據(Signal Skew)。

PCIe使用串行總線進行數據傳輸就沒有這些問題。它沒有外部時鐘信號,它的時鐘信息通過8/10編碼或者128/130編碼嵌入在數據流,接收端可以從數據流里面恢復時鐘信息,因此,它不受數據在線上傳輸時間的限制,你導線多長都沒有問題,你數據傳輸頻率多快也沒有問題;沒有外部時鐘信號,自然就沒有所謂的Clock Skew問題;由于是串行傳輸,只有一個bit傳輸,所以不存在Signal Skew問題。但是,如果使用多條Lane傳輸數據(串行中又有并行,哈哈),這個問題又回來了,因為接收端同樣要等最慢的那個Lane上的數據到達才能處理整個數據。不過,你不用擔心,PCIe自己能解決好這個問題。

-

接口

+關注

關注

33文章

8667瀏覽量

151526 -

SSD

+關注

關注

21文章

2870瀏覽量

117585 -

PCIe

+關注

關注

15文章

1245瀏覽量

82869

原文標題:PCIe SSD為什么那么快?

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三星980 PRO SSD詳細評測,樹立PCIe 4.0 SSD的性能標桿

PCIe 4.0 SSD尚未起飛,就要迎戰速度翻倍的5.0

用于存儲驅動器的PCIe SSD是否仍會被IOM提升?

在Xilinx ZCU102評估套件上啟用NVMe SSD接口

3D NAND及PCIe NVMe SSD為什么能晉升巿場主流?

PCIe 4.0 SSD尚未起飛,就要迎戰速度翻倍的5.0

請問S32R45是否支持PCIe NVMe SSD?

存儲新態勢!PCIe SSD與SATA SSD同價

pcie和ssd的區別介紹_哪個好

得一微電子入宣布戰略投資深圳大心電子科技,攜手力拓PCIe SSD市場

金士頓首款PCIe 4.0 SSD亮相 采用M.2轉接PCIe方案

江波龍推出XP2100 PCIe SSD

PCIe 5.0 SSD不用風扇會怎么樣?

那為什么SSD要用PCIe接口?

那為什么SSD要用PCIe接口?

評論