0 引言

隨著硬件技術(shù)的進(jìn)步,軟盤逐漸被新的存儲(chǔ)介質(zhì)代替。但部分舊設(shè)備(比如織布機(jī)等)并不支持這些更快、容量更大的存儲(chǔ)設(shè)備,也不支持網(wǎng)絡(luò)訪問。因此,設(shè)法將存儲(chǔ)設(shè)備虛擬成軟盤,通過網(wǎng)絡(luò)對(duì)其進(jìn)行數(shù)據(jù)訪問具有一定的實(shí)用價(jià)值。在臺(tái)式機(jī)讀寫軟盤過程中,數(shù)據(jù)流遵循MFM編碼格式,使用CRC校驗(yàn)檢測(cè)數(shù)據(jù)誤差。

本文提出一種基于FPGA和ARM的虛擬軟盤方案。在DE2-115開發(fā)平臺(tái)下,將2 MB的SRAM存儲(chǔ)器虛擬成1.44 MB軟盤,通過臺(tái)式機(jī)對(duì)虛擬軟盤的數(shù)據(jù)進(jìn)行讀寫,并使用樹莓派實(shí)現(xiàn)UDP服務(wù)器,通過網(wǎng)絡(luò)對(duì)虛擬軟盤的狀態(tài)和數(shù)據(jù)進(jìn)行讀寫訪問。

同時(shí),對(duì)設(shè)計(jì)方案進(jìn)行實(shí)現(xiàn)與驗(yàn)證,成功實(shí)現(xiàn)對(duì)虛擬軟盤的鏡像制作、文件讀寫、格式化、制作啟動(dòng)盤等操作,并實(shí)現(xiàn)局域網(wǎng)內(nèi)設(shè)備對(duì)虛擬軟盤的監(jiān)控。

1 虛擬軟盤核心模塊的設(shè)計(jì)與實(shí)現(xiàn)

1.1 虛擬軟盤數(shù)據(jù)分布結(jié)構(gòu)

一張軟盤包含80個(gè)磁道,每個(gè)磁道有2個(gè)柱面,每個(gè)柱面包含18個(gè)扇區(qū),每個(gè)扇區(qū)包含有512 B數(shù)據(jù)。整個(gè)軟盤包含有2×80×18×512 B=1.44 MB的數(shù)據(jù)量。在實(shí)際應(yīng)用中,軟盤通過軟驅(qū)線發(fā)送到臺(tái)式機(jī)的1個(gè)磁道的數(shù)據(jù),包含數(shù)據(jù)頭部、數(shù)據(jù)中部和數(shù)據(jù)尾部3個(gè)部分。

在本虛擬軟盤設(shè)計(jì)中,虛擬軟盤的數(shù)據(jù)分布結(jié)構(gòu)示意如圖1所示。

頭部的長(zhǎng)度為200 B,其中GAP數(shù)據(jù)為0x4E,用于填充磁道,共有184 B;SYNC為同步信號(hào)0x00,共有12 B;IAM表示索引信號(hào)地址標(biāo)記,內(nèi)容為0xC2C2C2FC,用來指示磁道開始。而數(shù)據(jù)中部則包含有18個(gè)扇區(qū)的數(shù)據(jù),每個(gè)扇區(qū)包含地址段和數(shù)據(jù)段兩部分。其中,地址段長(zhǎng)度為72 B,數(shù)據(jù)段長(zhǎng)度為608 B。地址段中:GAP段用于填充空間;SYNC表示同步;IDAM為地址標(biāo)記;CHNR包含有磁道、磁面、扇區(qū)號(hào)、扇區(qū)內(nèi)數(shù)據(jù)字節(jié)數(shù)等信息;CRC為2 B校驗(yàn)信息,校驗(yàn)起始于IDAM段,終止于CRC段。數(shù)據(jù)段中:GAP段用于填充空間;SYNC表示同步;DATAAM為地址標(biāo)記;DATA包含512 B數(shù)據(jù)信息;CRC為2 B的校驗(yàn)信息,校驗(yàn)起始于DATAAM段,終止于CRC段。磁道尾部包含的數(shù)據(jù)是用于填充用的GAP段,其內(nèi)容為0x4E,長(zhǎng)度為60 B。

1.2并行CRC運(yùn)算模塊的原理和實(shí)現(xiàn)

循環(huán)冗余校驗(yàn)(Cyclic Redundancy Check,CRC)算法在檢測(cè)數(shù)據(jù)傳輸?shù)恼`差上發(fā)揮著重要的作用[1]。CRC校驗(yàn)被用在PCI-Express總線、以太網(wǎng)(IEEE 802.3)以及WiFi(IEEE 802.11)等通信標(biāo)準(zhǔn)中[2]。通常使用的CRC校驗(yàn)生成算法有串行的線性反饋移位運(yùn)算LFSR[3-4],但隨著數(shù)據(jù)傳輸速率的提高,使用串行運(yùn)算不能滿足系統(tǒng)的要求[5],有必要實(shí)現(xiàn)并行CRC計(jì)算模塊。

對(duì)于數(shù)據(jù)字節(jié)流{Cn(x),…,C1(x),C0(x)},Ck(x)都是關(guān)于x的7次多項(xiàng)式,表征一個(gè)字節(jié)的數(shù)據(jù);生成多項(xiàng)式記作G(x),為關(guān)于x的N次多項(xiàng)式。CRC校驗(yàn)結(jié)果為:

考慮到有限域GF(2)上的加法等效于XOR異或運(yùn)算,而乘法等效于AND與運(yùn)算,在FPGA上可以實(shí)現(xiàn)一種基于矩陣式數(shù)據(jù)選通的并行CRC運(yùn)算模塊。其結(jié)構(gòu)框圖如圖2所示。該并行CRC運(yùn)算模塊包含有邏輯運(yùn)算陣列和輸出寄存器兩個(gè)部分。其中邏輯運(yùn)算陣列由組合邏輯構(gòu)成,其功能包括:將收到的數(shù)據(jù)DataIn左移(N-8)位,得到N位數(shù)據(jù) 利用

利用 與上次CRC運(yùn)算結(jié)果Rk(x)進(jìn)行XOR運(yùn)算,得

與上次CRC運(yùn)算結(jié)果Rk(x)進(jìn)行XOR運(yùn)算,得 運(yùn)算結(jié)果進(jìn)入數(shù)據(jù)選通運(yùn)算陣列,陣列由(N×N)個(gè)1-bit選擇器和N個(gè)N-bit XOR運(yùn)算單元構(gòu)成,選通使能信號(hào)是通過計(jì)算Φ=(A+KB)8結(jié)果得到的;陣列出來的運(yùn)算結(jié)果進(jìn)入輸出寄存器,由時(shí)序邏輯構(gòu)成,在模塊接收到ENA使能信號(hào)時(shí),寄存邏輯運(yùn)算陣列的結(jié)果輸出到Q;當(dāng)輸出寄存器接收到RST復(fù)位信號(hào)時(shí),CRC模塊的輸出Q相當(dāng)于CRC校驗(yàn)初始值R-1(x)。

運(yùn)算結(jié)果進(jìn)入數(shù)據(jù)選通運(yùn)算陣列,陣列由(N×N)個(gè)1-bit選擇器和N個(gè)N-bit XOR運(yùn)算單元構(gòu)成,選通使能信號(hào)是通過計(jì)算Φ=(A+KB)8結(jié)果得到的;陣列出來的運(yùn)算結(jié)果進(jìn)入輸出寄存器,由時(shí)序邏輯構(gòu)成,在模塊接收到ENA使能信號(hào)時(shí),寄存邏輯運(yùn)算陣列的結(jié)果輸出到Q;當(dāng)輸出寄存器接收到RST復(fù)位信號(hào)時(shí),CRC模塊的輸出Q相當(dāng)于CRC校驗(yàn)初始值R-1(x)。

在本虛擬軟盤設(shè)計(jì)中,取N=16,即進(jìn)行CRC-16校驗(yàn),生成多項(xiàng)式為G(x)=x16+x12+x5+1,根據(jù)定義得到K=[0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1]T,計(jì)算狀態(tài)轉(zhuǎn)移矩陣Φ,得到選通使能陣列如表1所示。其中橫向表示輸入位,用十六進(jìn)制表示相應(yīng)的位下標(biāo);縱向的表示輸出位對(duì)應(yīng)的下標(biāo);表中陰影部分對(duì)應(yīng)的輸入位被選通,空白部分對(duì)應(yīng)的輸入位不被選通。

1.3 MFM編解碼

1.3.1 MFM編碼原理與實(shí)現(xiàn)

在軟盤應(yīng)用中,讀寫的數(shù)據(jù)都是以串行方式傳輸?shù)摹MǔT诟鱾€(gè)數(shù)據(jù)位之間插入時(shí)鐘位,保證數(shù)據(jù)能被正確傳輸和識(shí)別[6]。在軟盤的數(shù)據(jù)傳輸中,采用MFM編碼。其表達(dá)式如下:(x,y,z)→(x,x NOR y,y,y NOR z,z),其中NOR為非或運(yùn)算,即p NOR q=p∨q。在RData和WData信號(hào)線上,一個(gè)電平翻轉(zhuǎn)表示在MFM編碼碼流的時(shí)鐘位或者數(shù)據(jù)位中出現(xiàn)了“1”;而沒有翻轉(zhuǎn),則表示在碼流的時(shí)鐘位或數(shù)據(jù)位中出現(xiàn)了“0”。采用500 kb/s的傳輸速率,一個(gè)數(shù)據(jù)位的傳輸需要消耗2 μs時(shí)間。圖3為4-bit數(shù)據(jù)流“1010”MFM編碼示意。

MFM編碼沒有起始標(biāo)志,所以在每個(gè)扇區(qū)地址段和數(shù)據(jù)段之前都有AM域,其中的數(shù)據(jù)字節(jié)“0xA1”的編碼采用了MMFM編碼,用于標(biāo)記碼流起始:在數(shù)據(jù)位中,若出現(xiàn)連續(xù)的0-0,則時(shí)鐘位變1;若出現(xiàn)0-0-0,則時(shí)鐘位是1-0;若出現(xiàn)0-0-0-0,則時(shí)鐘位是1-0-1;以此類推。

圖4是MFM編碼模塊的結(jié)構(gòu)框圖。整個(gè)MFM編碼過程由移位寄存模塊、核心編碼模塊、計(jì)數(shù)模塊和并行轉(zhuǎn)串行模塊組成。其中,移位寄存模塊保留上一字節(jié)數(shù)據(jù)的最低位和當(dāng)前字節(jié)數(shù)據(jù),生成數(shù)據(jù)mfmData用來傳遞給核心編碼模塊進(jìn)行MFM編碼。核心編碼模塊根據(jù)MFM編碼規(guī)則,對(duì)mfmData進(jìn)行編碼運(yùn)算,并通過Violate信號(hào)判斷當(dāng)前是否處于AM域,若是,則要使用MMFM編碼規(guī)則。計(jì)數(shù)器模塊用來生成BitCnt計(jì)數(shù)信號(hào),傳遞給并轉(zhuǎn)串模塊,生成最后的數(shù)據(jù)比特流mfmBit信號(hào)。

1.3.2 MFM解碼原理與實(shí)現(xiàn)

數(shù)據(jù)在編碼和傳輸過程中,經(jīng)常出現(xiàn)相位超前、延遲的情況。在MFM解碼之前,需要先同步WData碼流和MFM解碼時(shí)鐘。此外,軟盤數(shù)據(jù)在AM域的0xA1標(biāo)志遵循MMFM編碼,用于定位MFM碼流的起始位置。圖5是MFM解碼模塊的模塊結(jié)構(gòu)框圖。采用32 MHz的采樣時(shí)鐘捕捉WData信號(hào)。因?yàn)橐粋€(gè)數(shù)據(jù)位周期為2 μs,采樣過程中計(jì)數(shù)器由0計(jì)到63,即T=0,1,2,…,62,63。據(jù)此設(shè)定數(shù)據(jù)比特的采樣時(shí)間在T=10和T=42時(shí)刻采樣結(jié)果保存在移位寄存器SHIFTER中,并分離數(shù)據(jù)位和時(shí)鐘位。MFM碼流中的下降沿出現(xiàn)通常在T=0或者T=31時(shí)刻。AM域的數(shù)據(jù)字節(jié)0xA1經(jīng) MMFM編碼后CLOCK_BITS是0x0A,而MFM編碼后CLOCK_BITS為0x0E。據(jù)此,仲裁單元的相位調(diào)整規(guī)則如下:

(1)檢測(cè)到WData下降沿時(shí):若16≤T≤47,選通T=31;若T≤15或者T≥48,選通T=0;

(2)若DATA_BITS==0xA1且CLOCK_BITS ==0x0A,即檢測(cè)到0xA1編碼違例,則選通T=44;

(3)否則選通T=T+1。

最后,數(shù)據(jù)比特計(jì)數(shù)模塊用來判斷是否接收到8 bit數(shù)據(jù),若是,則輸出數(shù)據(jù)有效脈沖信號(hào)MFM_DATA_EN。

2 虛擬軟盤系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

2.1 虛擬軟盤系統(tǒng)框架結(jié)構(gòu)

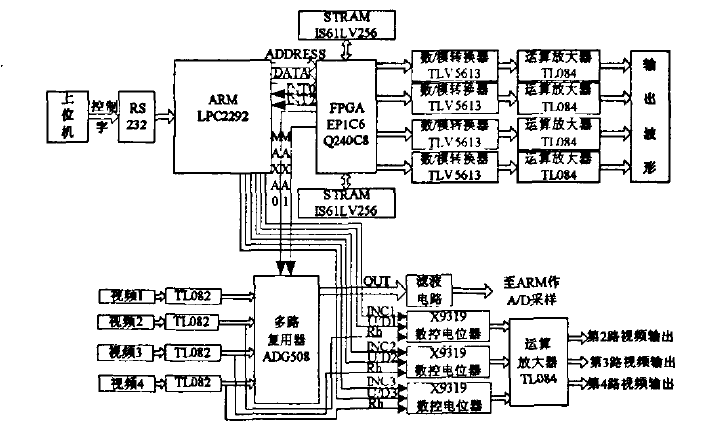

虛擬軟盤系統(tǒng)如圖6所示。其中,控制電腦與虛擬軟盤系統(tǒng)處于同一個(gè)局域網(wǎng)下,通過socket通信實(shí)現(xiàn)與虛擬軟盤系統(tǒng)的交互,包括軟盤狀態(tài)獲取、軟盤狀態(tài)修改、發(fā)送軟盤鏡像和選擇軟盤鏡像等命令;虛擬軟盤系統(tǒng)包括ARM、FPGA和SRAM存儲(chǔ)器3個(gè)部分,其中ARM和FPGA的交互通過SPI接口實(shí)現(xiàn);ARM負(fù)責(zé)網(wǎng)絡(luò)交互,從網(wǎng)絡(luò)獲取軟盤數(shù)據(jù)、狀態(tài)的讀寫命令,同時(shí)開啟SSH服務(wù),方便遠(yuǎn)程登錄,開啟FTP服務(wù)用于控制中心發(fā)送、選擇虛擬軟盤系統(tǒng)中的軟盤鏡像;FPGA負(fù)責(zé)將2 MB容量的SRAM虛擬成1.44 MB軟盤,并通過軟驅(qū)線和外部的臺(tái)式機(jī)/織布機(jī)進(jìn)行交互。

2.2 FPGA部分的結(jié)構(gòu)

FPGA部分的結(jié)構(gòu)框圖如圖7所示。該系統(tǒng)主要包括虛擬軟盤控制模塊、SPI收發(fā)模塊、SRAM控制模塊。

控制模塊實(shí)現(xiàn)軟盤磁針的位置控制和數(shù)據(jù)編解碼:步進(jìn)模塊通過檢測(cè)iStep下降沿和iDir電平確定當(dāng)前軟盤磁針?biāo)幍拇诺捞?hào)rCylNo;通過iHdSel電平確定磁針?biāo)幹嫣?hào)rHeadNo;旋轉(zhuǎn)模塊確定當(dāng)前扇區(qū)號(hào)rSectNo以及在扇區(qū)內(nèi)偏移地址rAddrL。MFM解碼模塊根據(jù)WData得到回寫數(shù)據(jù)wData和磁道wCylNo、柱面wHeadNo、扇區(qū)號(hào)wSectNo及扇區(qū)內(nèi)偏移地址wAddrL等信息。

通過SPI收發(fā)模塊,F(xiàn)PGA可獲取到ARM給出的讀寫命令,數(shù)據(jù)交換模塊會(huì)根據(jù)命令判斷執(zhí)行以下某個(gè)行動(dòng):讀取軟盤的扇區(qū)數(shù)據(jù)、修改軟盤的扇區(qū)數(shù)據(jù)、獲取軟盤狀態(tài)(寫保護(hù),軟盤就緒,寫入使能,磁道、磁面和扇區(qū)等)、修改軟盤狀態(tài)(寫保護(hù)和軟盤就緒等)。

地址、數(shù)據(jù)等信息通過地址轉(zhuǎn)移模塊,映射成對(duì)SRAM的讀地址rAddr和寫地址wAddr。通過SRAM讀寫控制模塊,可以對(duì)虛擬成軟盤的SRAM進(jìn)行數(shù)據(jù)訪問。CRC編碼模塊用于計(jì)算地址段和數(shù)據(jù)段的校驗(yàn)和,可以用來檢測(cè)數(shù)據(jù)傳輸上可能出現(xiàn)的錯(cuò)誤。軟盤數(shù)據(jù)或者校驗(yàn)和經(jīng)過MFM編碼模塊生成MFM碼流傳送給臺(tái)式機(jī)。

2.3 ARM程序結(jié)構(gòu)

ARM部分的程序設(shè)計(jì)框圖如圖8所示。其中,主線程負(fù)責(zé)socket和SPI接口的初始化,并創(chuàng)建線程1和線程2;線程1負(fù)責(zé)通過網(wǎng)絡(luò)獲取控制中心的命令(包括軟盤狀態(tài)讀取命令即#R,軟盤狀態(tài)修改命令即#W、WP、READY、FLAG,以及鏡像文件讀取/寫入命令即&R/W、xxx.ima),對(duì)互斥量filelock進(jìn)行上鎖后,修改data_sent為1,再把filelock解鎖;線程2負(fù)責(zé)判斷data_sent是否為1,即網(wǎng)絡(luò)命令是否有效。若是,則對(duì)filelock進(jìn)行上鎖后,根據(jù)網(wǎng)絡(luò)命令執(zhí)行相應(yīng)的操作,并返回相應(yīng)數(shù)據(jù)給控制中心,再將data_sent清零后,把filelock解鎖;若data_sent為0,即沒有收到網(wǎng)絡(luò)命令,那么讀取當(dāng)前軟盤狀態(tài),空閑1 s后,重新進(jìn)行循環(huán)。

此外,ARM端還負(fù)責(zé)作為FTP服務(wù)器,用于接收控制中心發(fā)送的各個(gè)ima軟盤鏡像文件。

3 虛擬軟盤運(yùn)行測(cè)試情況

針對(duì)提出的虛擬軟盤設(shè)計(jì)方案進(jìn)行測(cè)試與驗(yàn)證。在Altera的DE2-115開發(fā)板上燒寫FPGA工程文件,并在樹莓派上運(yùn)行ARM部分的程序。對(duì)虛擬軟盤的測(cè)試包括虛擬軟盤格式化、文件讀寫、鏡像制作、啟動(dòng)盤測(cè)試等。首先對(duì)虛擬軟盤徹底格式化,將虛擬軟盤所有扇區(qū)數(shù)據(jù)清零;然后進(jìn)行多文件隨機(jī)寫入,并讀取虛擬軟盤文件,進(jìn)行文件比較,比對(duì)結(jié)果說明虛擬軟盤讀寫正常;最后,制作啟動(dòng)盤并利用UltraISO制作軟盤鏡像,通過啟動(dòng)測(cè)試程序加載鏡像,能順利進(jìn)入系統(tǒng),說明啟動(dòng)盤制作和讀取正常。

4 結(jié)論

本文提出并實(shí)現(xiàn)了一種基于FPGA和ARM的虛擬軟盤方案,并成功將2 MB的SRAM虛擬成1.44 MB軟盤,可通過網(wǎng)絡(luò)對(duì)虛擬軟盤的狀態(tài)和數(shù)據(jù)進(jìn)行遠(yuǎn)程訪問,也可通過臺(tái)式機(jī)對(duì)虛擬軟盤進(jìn)行讀寫操作。利用實(shí)際開發(fā)板進(jìn)行實(shí)驗(yàn),驗(yàn)證了本設(shè)計(jì)方案的可行性。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603387 -

ARM

+關(guān)注

關(guān)注

134文章

9097瀏覽量

367560 -

編碼

+關(guān)注

關(guān)注

6文章

942瀏覽量

54829

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

關(guān)于quartus虛擬按鍵的問題

VxWorks 系統(tǒng)啟動(dòng)

FPGA板卡能實(shí)現(xiàn)虛擬化圖形界面嗎

有什么方式能夠用FPGA實(shí)現(xiàn)虛擬光柵的生成

基于ARM的嵌入式系統(tǒng)中從串配置FPGA的實(shí)現(xiàn),不看肯定后悔

怎么實(shí)現(xiàn)基于FPGA的低成本虛擬測(cè)試系統(tǒng)的設(shè)計(jì)?

ARM的虛擬化技術(shù)是什么?如何去實(shí)現(xiàn)呢

一種基于FPGA技術(shù)的虛擬邏輯分析儀的研究與實(shí)現(xiàn)

基于FPGA的虛擬測(cè)試系統(tǒng)實(shí)現(xiàn)

關(guān)于MPU, FPGA SoC以及eFPGA

基于FPGA的ARM并行總線和端口設(shè)計(jì)

如何使用FPGA和ARM設(shè)計(jì)和實(shí)現(xiàn)多路視頻采集系統(tǒng)

ARM與FPGA的接口實(shí)現(xiàn)的解析

基于ARM的FPGA嵌入式系統(tǒng)實(shí)現(xiàn)

關(guān)于基于FPGA和ARM的虛擬軟盤實(shí)現(xiàn)

關(guān)于基于FPGA和ARM的虛擬軟盤實(shí)現(xiàn)

評(píng)論