一個總線周期由多個不可分的時鐘周期構成,完成單次讀/寫操作、塊讀/寫操作或者讀改寫操作。總線周期也分為單次讀/寫周期、塊讀/寫周期和讀改寫周期。一次塊讀/寫總線周期完成多次數據讀/寫操作。一般情況下,一次操作由主設備和從設備控制信號間的一次握手,以及同時進行的地址和數據總線的一次傳輸構成。塊操作表示整個操作需要完成多次數據傳送。在總線周期中主設備和從設備預先設定好的共同遵守控制信號握手規則,以及地址和數據總線的傳輸規則稱作總線協議。

在下文(包括以后的博文中)所給圖例中給出的信號均為主設備的輸入輸出信號。因此,對操作的描述也從主設備信號的角度展開,以便于讀者對照正文理解圖例。比如"在時鐘上升沿1到達之前,從設備檢測到主設備發起的操作,將適當的數據放到主設備的輸入信號DAT_I()和TGD_I(),將主設備的ACK_I置高作為對主設備STB_O的響應。"的等價描述為:"在時鐘上升沿1到達之前,從設備檢測到主設備發起的操作,將適當的數據放到其輸出信號DAT_O()和TGD_O(),將輸出信號ACK_O置高作為對主設備STB_O的響應。"

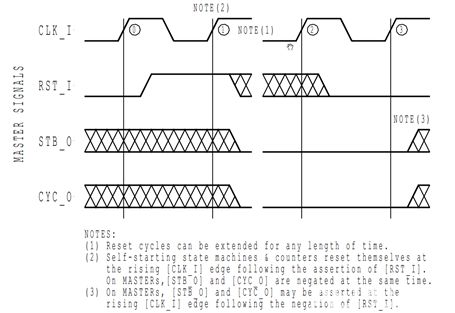

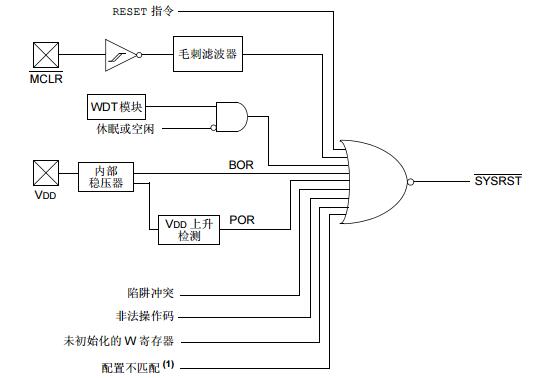

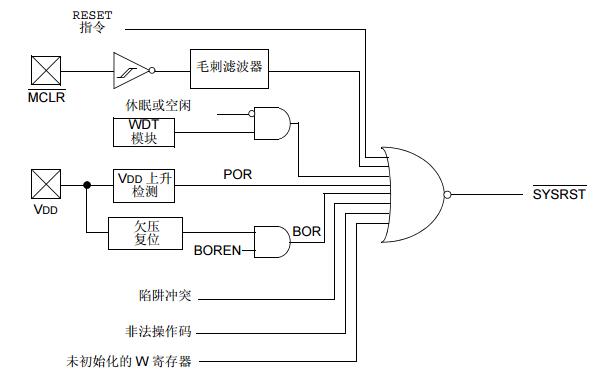

復位操作

復位是數字系統最基本的操作。復位后,系統進入預定的狀態。在遵守Wishbone總線規范的系統中,當RST_I信號有效,系統開始復位。由于Wishbone規范規定的復位是同步復位,因此在復位信號有效后接下來的時鐘上升沿,所有信號和寄存器進入預定狀態。因此,Wishbone規范要求RST_I信號有效時間至少要一個時鐘周期。在數字系統中,實際上更多的采用的是異步復位,而且復位信號的長度一般大于系統電平穩定時間和系統時鐘頻率穩定時間。如果在Wishbone接口中使用的是異步復位,設計者需要在文檔中說明,因為Wishbone接口默認的是同步復位。

圖6 Wishbone總線的復位操作

在圖6中,我們只給出了STB_O和CYC_O這兩個信號,而沒有給出其它信號。當這兩個信號無效時,所有其他信號沒有意義。

規則3.00:所有的Wishbone接口必須在RST_I置位(變為1)后的第一個時鐘上升沿進入初始化狀態,直到RST_I被復位(變為0)后的第一個時鐘上升沿到來。

規則3.05:RST_I必須被置位至少一個完整的時鐘周期,才能有效地完成復位。

允許3.00:當然,RST_I也可以被置位多個時鐘周期,但是數量必須是有限的。

規則3.10:所有的Wishbone接口必須能夠在任意時間響應RST_I信號(優先級足夠高)。

規則3.15:所有的Wishbone自啟動狀態機核計數器必須在RST_I置位(變為1)后的第一個時鐘上升沿進入初始化狀態,直到RST_I被復位(變為0)后的第一個時鐘上升沿到來。

規則3.20:以下主機信號必須在RST_I置位(變為1)后的第一個時鐘上升沿復位(變為0),直到RST_I被復位(變為0)后的第一個時鐘上升沿到來:STB_O,CYC_O。所有的其他主機此時不能操作這些信號,以響應復位周期。RST_I被復位(變為0)后的第一個時鐘上升沿到來后,主機接口的STB_O和CYC_O信號可以被立即置位(變為1)。

注意3.10:在標準模式下(除了流水線之外的模式),當STB_I被復位(變為0)時,從機接口應自動將ACK_O,ERR_O和RTY_O置位。

推薦3.00:設計SYSCON模塊時,應保證上電復位時將RST_O信號置位。并且RST_O信號應該保持置位狀態,直到電壓和時鐘頻率進入穩定狀態。最好使用同步復位的方式,以保證設計的兼容性。

注意3.15:在使用門控時鐘的情況下,如果時鐘被禁止了。此時,Wishbone總線將不能響應RST_I信號。

建議3.00:如果一些IP核或者SoC模塊需要異步復位,應當將復位信號定義為非Wishbone標準信號。這樣可以保證Wishbone接口使用純同步時序,以避免造成疑惑。

注意3.20:所有的Wishbone接口信號都應能響應復位信號,除了IP核接口。

傳輸周期初始化

主機接口通過置位CYC_O信號進行初始化傳輸周期,當CYC_O信號被復位,其他所有的主機信號都被視為無效。從機也只在其CYC_I信號被置位的情況下,才會響應其他主機信號。應當注意,SYSCON信號不受影響。

規則3.25:在單獨寫周期、塊讀寫周期和讀改寫周期(RMW)持續期間。主機接口必須將CYC_O信號置位。CYC_O信號置位時間必須不晚于STB_O置位后的第一個時鐘上升沿,CYC_O信號置位時間必須不早于STB_O復位后的第一個時鐘上升沿。

允許3.05:主機接口可以在任意時間置位CYC_O。

推薦3.05:仲裁邏輯經常使用CYC_I信號進行主機選擇。保持CYC_O一直長時間處于置位狀態可能會導致仲裁錯誤。因此在多主機情況下,應當避免使用【允許3.05】。

規則3.30:當CYC_I被復位時,從機接口可以不響應任何其他主機信號。但是其必須響應SYSCON信號。

-

信號

+關注

關注

11文章

2791瀏覽量

76815 -

總線

+關注

關注

10文章

2887瀏覽量

88125 -

Wishbone

+關注

關注

0文章

16瀏覽量

10438

原文標題:【博文連載】Wishbone總線周期之復位操作

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

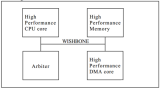

wishbone總線

基于WISHBONE總線的FLASH閃存接口設計

基于Wishbone片上總線的IP核的互聯

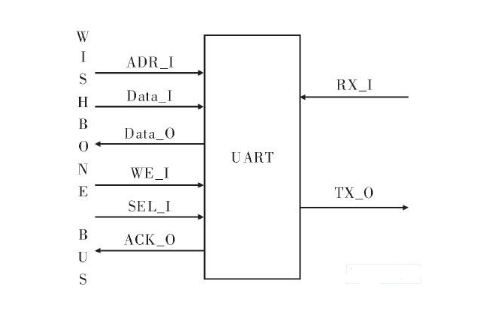

基于Wishbone總線的UART IP核設計

基于WISHBONE總線的FLASH閃存接口設計

基于WISHBONE總線的通用接口控制器

Wishbone總線實現UART IP核設計

基于FPGA的SDX總線與Wishbone總線接口設計

Wishbone總線的異步周期結束路徑

Wishbone總線的主要特征概括

Wishbone總線周期之復位操作

Wishbone總線周期之復位操作

評論