在無線網絡中,射頻模塊有傳導TRP和傳導TIS兩項重要指標,而模塊裝上天線后,整機在OTA暗室中需測試TRP與TIS,在此我們將其定義為輻射TRP和輻射TIS。輻射TRP一般不會出問題,而輻射TIS容易受產品內部電磁噪聲的干擾。當輻射TIS不達標時,首先要考慮傳導TIS是否達標,傳導TIS和射頻電路中的器件(如雙工器的隔離度)、各節電路的匹配等因素有關。射頻電路部分工作流程如下:

接收:天線 →匹配電路 →雙工器 →聲表濾波器(SAW) →低噪聲放大器(LNA) →混頻器

發射:天線← 匹配電路← 雙工器← 功率放大器(PA)← 混頻器

當傳導TIS達標后,我們再處理產品內部的電磁干擾。電磁干擾是無處不在的,產品內部工作頻率及其諧波頻率高達1G以上,當干擾頻率落在天線接收頻率范圍時,就會影響TIS。下面通過一些案例說明電磁干擾對輻射TIS的影響。

案例一:智能POS機中DDR時鐘、屏的時鐘和數據、地噪聲影響4G天線TIS。

呈現問題:

智能POS機中,4G天線FDD ban5/8 在OTA暗室中測試TIS值為-78dB,輻射TIS不合格(合格值為-91dBm),而輻射TRP與模塊傳導TRP與TIS都達標。

分析問題:

傳導TRP與TIS都達標,說明模塊本身無問題;輻射 TRP達標,說明天線也沒問題,而輻射TIS僅為-78dBm, 可以判定是產品內部電磁干擾影響了接收靈敏度。運用頻譜儀偵測干擾源,發現CPU與DDR的時鐘頻率和屏的差分時鐘、數據干擾很大(如下圖)。

解決問題:

1.通過軟件適當降低DDR時鐘的驅動能力,TIS值從-78dBm提升到了-80dBm, 用錫將CPU與DDR上方的屏蔽蓋周圍與PCB地良好焊接,TIS值從-80dBm提升到了-83dBm(用錫將屏蔽蓋焊死不符合量產,后面改板將屏蓋夾子去掉,將夾子改為金屬框,金屬框與PCB地良好焊接,然后屏蔽蓋卡進金屬框,測試TIS能達- 82dBm。)

小結:屏蔽蓋的作用一是屏蔽空間輻射,作用二是承當地回路,減弱共模噪聲。

2. 焊好屏蔽蓋后,用導電布將屏排線屏蔽并兩端接地,測試TIS值能達-86dBm 。(改板后在屏的差分時鐘和數據對各串一顆90Ω的共模電感,同時將原來的屏FFC排線改為FPC排線,測試TIS能達-88dbm。

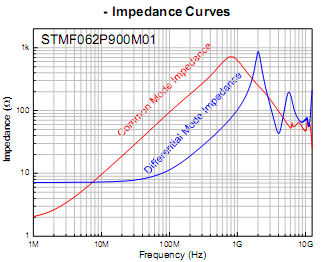

小結:下圖是90Ω共模電感的頻率特性曲線圖,90Ω指的是頻率在100MHz時的共模阻抗,共模阻抗隨著頻率的變化而變化,在800MHz-960MHz時的共模阻抗高達600Ω,所以共模電感對800MHz-960MHz的共模噪聲有很好的抑制效果;FPC排線具備屏蔽效果,同時能給信號提供地回路。

3. 將屏后鐵板與PCB地相接的導電棉去掉,只保留天線接地位的導電棉,測試TIS能達-91dBm, 最終輻射 TIS 達標。

小結:地噪聲傳播的形式是電流,電流往阻抗低的方向流動,PCB上的地噪聲會通過導電棉流向后蓋金屬,然后通過后蓋流向天線的接地位。

案例二:智能音箱中頻偏影響WIFI天線的TIS。

呈現問題:

智能音箱中2.4G WIFI天線 測試傳導、輻射的TRP和TIS都不達標,天線的駐波比、回波損耗等參數正常。

分析問題:

傳導TRP和TIS都不合格,說明模塊本身存在問題;通過調節各電路的匹配,TRP和TIS沒有明顯提升,通過頻譜儀查看發射頻率,發現其頻率偏移,頻偏問題首先考慮晶振,因為晶振基準頻率誤差大,就會造成本地振蕩信號頻偏,本地振蕩信號是合成發射和接收頻率的一部分。

解決問題:

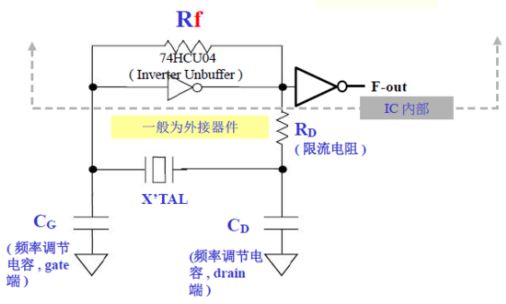

如下圖,通過調節晶振兩邊的匹配電容CG和CD,最后取值10pF, 使發射和接收頻率都在標準范圍內,最終測試TRP和TIS合格。

小結:負載電容是晶振產生基準頻率的一個參數,負載電容包含了CG、CD和走線寄生電容以及芯片端等效電容 ,走線寄生電容和芯片端等效電容不好把控,所以需要外圍 CG、CD去調節。

案例三:行程記錄儀中 DC-DC 和攝像頭的噪聲影響GPS天線的接收靈敏度

呈現問題:

行程記錄儀中GPS天線測試輻射TIS不達標,而TRP與傳導TIS都滿足要求。天線的駐波比、回波損耗等參數正常,這樣基本可以判定是產品內部電磁干擾影響了接收靈敏度。

分析問題:

運用頻譜儀偵測干擾源,發現背光的DC-DC輸出的紋波噪聲和攝像頭時鐘的諧波干擾很大,實驗的過程中,調節頻的亮度和關閉攝像頭,搜星數和星值都有提升,確定了背光和攝像頭的噪聲干擾了GPS天線的TIS。

解決問題:

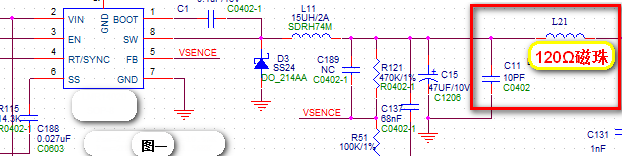

1.如下圖,分別在MCLK和PCLK線上串120Ω磁珠,MCLK的磁珠靠近芯片端,PCLK線上的磁珠串在攝像頭端,搜星數和星值有一定的提升。

小結:磁珠放置的位置是靠近源端,這樣就減弱了中間部分走線的輻射和耦合干擾。MCLK由芯片給出,而PCLK由攝像頭發出。

2.如下圖,DC-DC輸出端增加一顆10pF的電容,然后在電容后串120Ω的磁珠濾除紋波,最后GPS搜星數和星值達標。

小結:通過計算,10pF左右的電容濾除1.575GHz的頻率效過最佳,而磁珠的大小和放置的位置會影響DC-DC的轉換效率,磁珠一般放置在電容之后。

總結:產品內部常見的電磁干擾有DDR、屏、攝像頭等時鐘的諧波噪聲和DC-DC紋波噪聲、地噪聲等。PCB設計初期需考慮EMC設計,布好局、布好線,高頻信號線設計串共模電感或磁珠的位置,電壓線設計串磁珠和并電容位置等等,避免再次改板,縮短研發周期。

-

天線

+關注

關注

68文章

3203瀏覽量

140835 -

電磁干擾

+關注

關注

36文章

2316瀏覽量

105444

原文標題:電磁干擾影響天線接收靈敏度案例分析

文章出處:【微信號:gh_d145c2054c9d,微信公眾號:RF與EMC小助手】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電磁干擾與電磁輻射的區別 EMI電磁干擾與電力系統的關系

EMI電磁干擾的常見來源 電磁干擾對電子設備的影響

收藏這篇,輕松拿捏電磁干擾EMI

電磁干擾對輻射TIS的影響

電磁干擾對輻射TIS的影響

評論