現場可編程門陣列(FPGA)與模數轉換器(ADC)輸出的接口是一項常見的工程設計挑戰。本文簡要介紹各種接口協議和標準,并提供有關在高速數據轉換器實現方案中使用LVDS的應用訣竅和技巧。

接口方式和標準現場可編程門陣列(FPGA)與模數轉換器(ADC)數字數據輸出的接口是一項常見的工程設計挑戰。此外,ADC使用多種多樣的數字數據樣式和標準,使這項挑戰更加復雜。對于通常在200 MHz以下的低速數據接口,單倍數據速率(SDR) CMOS非常普遍:發送器在一個時鐘沿傳送數據,接收器在另一個時鐘沿接收數據。這種方式可確保數據有充足的時間完成建立,然后由接收器采樣。在雙倍數據速率(DDR) CMOS中,發送器在每一個時鐘沿都會傳送數據。因此,在相同的時間內,它傳輸的數據量是SDR的兩倍。然而,接收器正確采樣的時序更加復雜。

并行低壓差分信號(LVDS)是高速數據轉換器的常見標準。它采用差分信號,每一位均有P線和N線;在最新的FPGA中,其速度可達DDR 1.6 Gbps或800 MHz。并行LVDS的功耗低于CMOS,但所需的線數則是CMOS的兩倍,因而布線可能比較困難。

LVDS常常用在具有“源同步”時鐘系統的數據轉換器中,不過這并不是LVDS標準的一部分。在這種設置中,時鐘與數據同相,并且與數據一同發送。這樣,接收器就能使用該時鐘更輕松地捕捉數據,因為它現在知道數據傳輸何時發生。

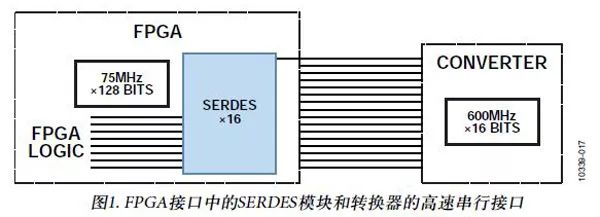

FPGA邏輯的速度一般跟不上高速轉換器的總線速度,因此大多數FPGA具有串行器/解串器(SERDES)模塊,用以將轉換器端的快速、窄帶串行接口轉換為FPGA端的慢速、寬帶并行接口。針對總線中的每個數據位,此模塊輸出2、4或8位,但以?、?或1/8的時鐘速率輸出,從而有效地將數據解串。數據由FPGA內部的寬總線處理,其速度遠低于連接到轉換器的窄總線。

LVDS信號標準也用于串行鏈路,大部分是用在高速ADC上。當引腳數量比接口速度更重要時,通常使用串行LVDS。常常使用兩個時鐘:數據速率時鐘和幀時鐘。并行LVDS部分提到的所有考慮同樣適用于串行LVDS。并行LVDS不過是由多條串行LVDS線組成。

I2C使用兩條線:時鐘和數據。它支持總線上的大量器件,而無需額外的引腳。I2C相對較慢,考慮協議開銷,速度為400 kHz至1 MHz。它通常用在慢速、小尺寸器件上。I2C也常常用作控制接口或數據接口。

SPI使用3到4條線:

時鐘

數據輸入和數據輸出(4線),或者雙向數據輸入/數據輸出(3線)

片選(每個非主機器件使用一條線)

可用片選線有多少,SPI就能支持多少器件。它的速度可達約100 MHz,通常用作控制接口和數據接口。

串行PORT (SPORT)是一種基于CMOS的雙向接口,每個方向使用一個或兩個數據引腳。對于非%8分辨率,其可調字長能夠提高效率。SPORT支持時域復用(TDM),通常用在音頻/媒體轉換器和高通道數轉換器上。它提供每引腳約100 MHz的性能。

Blackn處理器支持SPORT,FPGA上可直接實現SPORT。SPORT一般僅用于數據傳輸,但也可以插入控制字符。

JESD204是一種JEDEC標準,用于單一主機(如FPGA或ASIC等)與一個或多個數據轉換器之間的高速串行鏈路。最新規格提供每通道或每差分對最高3.125 Gbps的速度。未來的版本可能提供6.25 Gbps及更高的速度。通道采用8B/10B編碼,因而通道的有效帶寬降為理論值的80%。時鐘嵌入在數據流中,因此沒有額外的時鐘信號。多個通道可以結合在一起以提高吞吐量,數據鏈路層協議確保數據完整性。在FPGA/ASIC中,為實現數據幀傳輸,JESD204需要的資源遠遠多于簡單的LVDS或CMOS。它顯著降低了接線要求,不過要求使用更昂貴的FPGA,PCB布線也更加復雜。

一般建議進行ADC與FPGA的接口設計時,下列一般建議會有所幫助。

使用接收器、FPGA或ASIC的外部電阻終端,而不要使用FPGA內部終端,以免不匹配引起反射,致使超出時序預算。

如果系統使用多個ADC,請勿使用某個ADC的某個DCO。

布設連接到接收器的數字走線時,請勿采用大量“轉接”(tromboning)來使所有走線

保持等長。

利用CMOS輸出端的串聯終端降低邊沿速率并限制開關噪聲。確認所用的數據格式(二進制補碼或偏移二進制)正確。

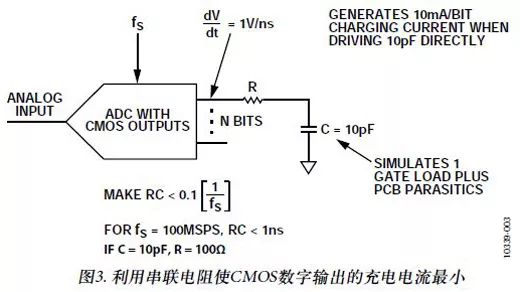

采用單端CMOS數字信號時,邏輯電平以大約1 V/nS的速度移動,典型輸出負載為10 pF(最大值),典型充電電流為10 mA/位。應采用盡可能小的容性負載,使充電電流最小。這可以利用盡可能短的走線僅驅動一個門來實現,最好沒有任何過孔。在數字輸出端和輸入端使用阻尼電阻,也可以使充電電流最小。

阻尼電阻和容性負載的時間常數應為采樣速率周期的大約10%。如果時鐘速率為100 MHz,負載為10 pF,則該時間常數應為10 nS的10%,即1 nS。這種情況下,R應為100 Ω。為獲得最佳信噪比(SNR)性能,1.8 V DRVDD優于3.3 VDRVDD。然而,當驅動大容性負載時,SNR性能會下降。CMOS輸出支持最高約200 MHz的采樣時鐘速率。如果驅動兩個輸出負載,或者走線長度大于1或2英寸,建議使用緩沖器。

ADC數字輸出應小心對待,因為瞬態電流可能會耦合回模擬輸入端,導致ADC的噪聲和失真提高。

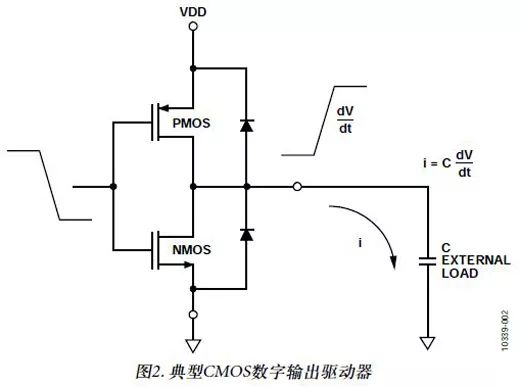

圖2所示的典型CMOS驅動器能夠產生很大的瞬態電流,尤其是驅動容性負載時。對于CMOS數據輸出ADC,必須采取特別措施以使這些電流最小,不致于在ADC中產生額外的噪聲和失真。

典型示例

圖3顯示了一個16位并行CMOS輸出ADC的情況。每路輸出有一個10pF負載,用以模擬一個門負載加上PCB寄生電容;當驅動10 pF負載時,各驅動器產生10 mA的充電電流。因此,該16位ADC的總瞬態電流可能高達16 × 10 mA = 160 mA。在各數據輸出端增加一個小串聯電阻R,可以抑制這些瞬態電流。應適當選擇該電阻的值,使RC時間常數小于總采樣周期的10%。如果fs = 100 MSPS,則RC應小于1 ns。C = 10 pF,因此最佳的R值約為100 Ω。選擇更大的R值可能會降低輸出數據建立時間性能,并干擾正常的數據捕捉。CMOS ADC輸出端的容性負載應以單個門負載為限,通常是一個外部數據捕捉寄存器。任何情況下都不得將數據輸出端直接連到高噪聲數據總線,必須使用一個中間緩沖寄存器,使ADC輸出端的直接負載最小。

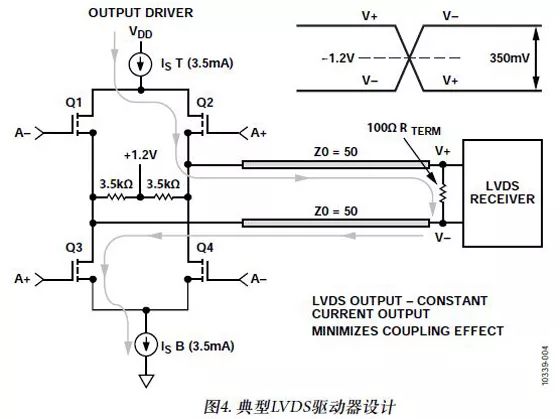

圖4顯示了CMOS中的一個標準LVDS驅動器。標稱電流為3.5 mA,共模電壓為1.2 V。因此,當驅動一個100 Ω差分終端電阻時,接收器各輸入的擺幅為350 mV p-p,這相當于700 mV p-p的差分擺幅。這些數值來源于LVDS規范。

LVDS標準有兩個:一個由ANSI制定,另一個由IEEE制定。雖然這兩個標準類似且大致兼容,但并不完全相同。圖5比較了這兩個標準的眼圖和抖動直方圖。IEEE標準LVDS的擺幅為200 mV p-p,低于ANSI標準的320 mV p-p,這有助于節省數字輸出的功耗。因此,如果IEEE標準支持目標應用及與接收器的連接,建議使用IEEE標準。

圖6比較了走線長度超過12英寸或30厘米情況下的ANSI和IEEE LVDS標準。兩幅圖中,驅動電流均采用ANSI版標準。右圖中,輸出電流加倍,這可以凈化眼圖并改善抖動直方圖。

圖7顯示了長走線對FR4材料的影響。左圖顯示了發送器端的理想眼圖。在距離40英寸的接收器端,眼圖幾乎閉合,接收器難以恢復數據。

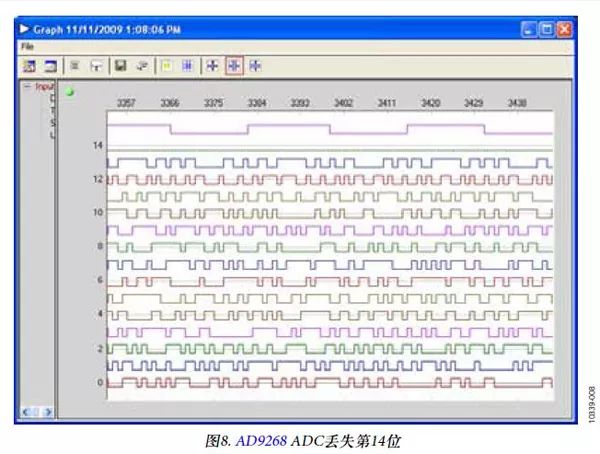

故障排除技巧ADC丟失第14位

圖8中,數據位的VisualAnalog數字顯示表明,第14位從未跳變。這可能說明器件、PCB或接收器有問題,或者無符號數據不夠大,無法使最高有效位跳變。

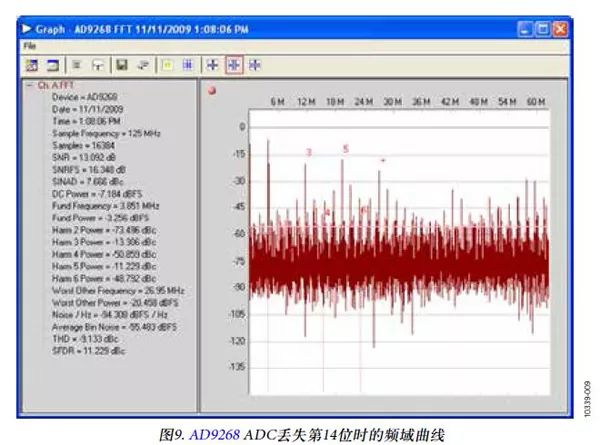

ADC丟失第14位時的頻域曲線

圖9顯示了上述數字數據(其中第14位未跳變)的頻域視圖。該圖說明,第14位有意義,系統中的某個地方發生錯誤。

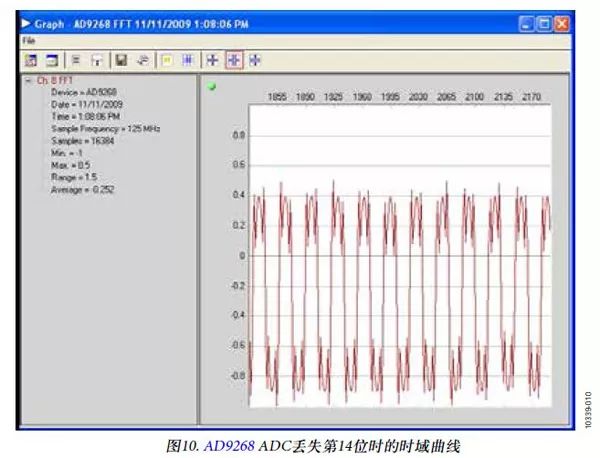

ADC丟失第14位時的時域曲線

圖10為相同數據的時域曲線。它不是一個平滑的正弦波,數據發生偏移,波形中多個點處有明顯的尖峰。

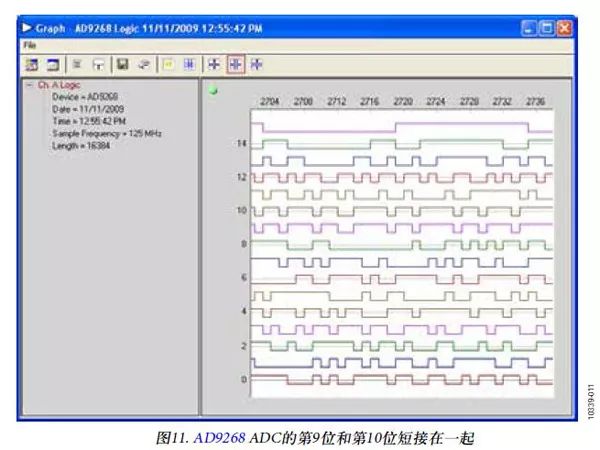

ADC的第9位和第10位短接在一起

圖11所示不再是丟失一位的情況,而是兩位短接在一起,因此對于這兩個引腳,接收器始終接收到相同的數據。

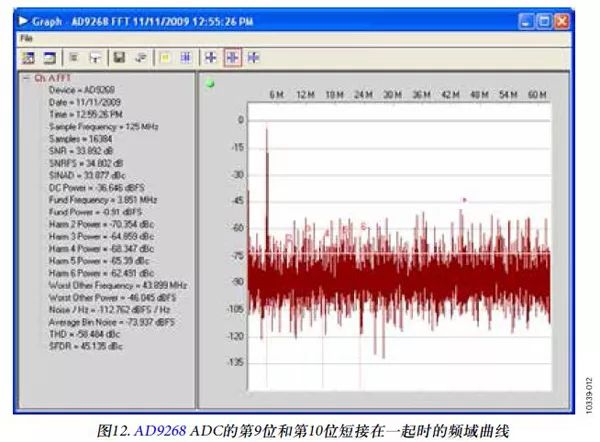

ADC第9位和第10位短接在一起時的頻域曲線

圖12顯示了兩位短接在一起時的頻域視圖。雖然基頻音非常清楚,但噪底顯著低于預期。噪底失真的程度取決于短接哪兩位。

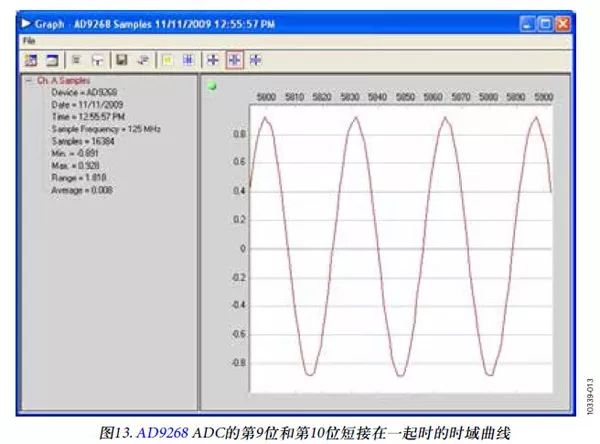

ADC第9位和第10位短接在一起時的時域曲線

在圖13所示的時域圖中,問題相對不明顯。雖然在波峰和波谷處損失了一些平滑度,但當采樣速率接近波形頻率時,這是常見現象。

數據和時鐘時序無效時的時域曲線

圖14顯示了一個因建立/保持問題而導致時序無效的轉換器的情況。上述錯誤一般會在數據的每個周期中出現,而時序錯誤則不然,通常并不是持續存在。不太嚴重的時序錯誤可能是間歇性的。這些圖顯示了不符合時序要求的數據捕捉的時域和頻域曲線。注意,各周期的時域錯誤并不一致。還應注意FFT/頻域的噪底有所提高,這通常表示有一位丟失,原因可能是時序對齊錯誤。

數據和時鐘時序無效時的放大時域曲線

圖15是圖14所示時域時序誤差的放大圖。同樣應注意,各周期的錯誤并不一致,但某些錯誤會重復。例如,該圖中有多個周期的谷底上出現負尖峰。

-

FPGA

+關注

關注

1630文章

21794瀏覽量

605148 -

轉換器

+關注

關注

27文章

8741瀏覽量

147729 -

lvds

+關注

關注

2文章

1045瀏覽量

65937

原文標題:FPGA與ADC數字數據輸出的接口

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速數字轉換器與FPGA開發電路指南

FPGA與ADC數字輸出的各種接口協議和標準

簡易USB與LVDS接口轉換器

采用LVDS的高速模擬數字轉換數據

高速轉換器的種類及特定應用的具體特點

高速轉換器應用指南及需要注意的事項

一款高性價比DP轉LVDS轉換方案|整體低BOM成本DP轉LVDS方案|CS5211 DP to LVDS方案設計方法

寬帶數據轉換器應用的JESD204B與串行LVDS接口考量

為高速數據轉換器設計低抖動時鐘

AD9684: 14-Bit, 500 MSPS LVDS, 雙向數字轉換轉換器 ADI

高速數據轉換器實現方案中使用LVDS的應用訣竅和技巧

高速數據轉換器實現方案中使用LVDS的應用訣竅和技巧

![AN-586: <b class='flag-5'>高速</b>模數<b class='flag-5'>轉換器</b>的<b class='flag-5'>LVDS</b><b class='flag-5'>數據</b>輸出[中文版]](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

評論