摘要:

針對工業物聯網等應用場景中ADC的供電電壓范圍寬、功耗要求苛刻等問題,提出了一種配置靈活、低功耗、低噪聲的片上基準電壓產生電路,為ADC提供與電源無關滿量程電壓。該電路在電源電壓為2.65 V~3.6 V時提供2.5 V參考電壓,電源電壓為2.2 V~3.6 V時提供1.5 V的參考電壓。該電路可以配置成片外電容模式,關閉緩沖器電路,降低整體的功率;還可以配置成內部緩沖器模式,減小基準電壓產生電路的建立時間,從而降低ADC單次采樣消耗的能量。芯片測試結果表明,該方案能夠滿足ADC在各種應用條件下的精度和速度需求。

0 引言

隨著工業物聯網的發展,人們需要處理更多自然界中的信號。自然界中聲、光、電等模擬信號需要經過模擬-數字轉換器(Analog-Digital Convertor,ADC)轉換成數字信號才能被數字系統進一步處理。

逐次逼近(Successive Approximation Register,SAR)型ADC因其低電源壓、低功耗、與數字電路兼容性好的優點,在傳感器、物聯網等中等精度(10 bit~12 bit)、中等速度(50 ks/s~200 ks/s)領域應用廣泛。

主流的SAR ADC一般通過電容的電荷分享的原理實現SAR邏輯的算法,電容型SAR ADC的優點是:電容陣列沒有靜態功耗,利于低功耗設計;電容的匹配性較好,精度接近12 bit。

電容型SAR ADC需要一個有驅動能力的緩沖器為電容陣列提供一個參考電壓。這個參考電壓作為ADC的滿量程電壓,需要有較高的精度,保證ADC的滿量程不隨時間、電源電壓變化;SAR ADC電容切換后,參考電壓需要能快速恢復,因此,參考電路還需要有驅動能力。在傳統的設計中,這樣一個參考電壓產生電路需功耗很大,有時甚至超過SAR ADC本身的功耗。

本文提出了一種可以根據應用場景靈活使用的參考電壓產生電路(Reference Voltage Generator,RVG)。根據ADC的使用方式,選擇電壓基準電路的使用方式,可以在保證性能的前提下,兼具電源電壓低、功耗低、應用靈活的優點。

1 SAR ADC基本原理

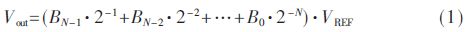

圖1所示為電荷型SAR ADC的基本架構[1]。SAR ADC的基本結構包含一個比較器、一個數字模擬轉換器(Digital-Analog Convertor,DAC)和一個逐次逼近控制器(SAR Logic)。DAC采用電荷按比例縮放的結構,通過比例電容的切換實現將輸入信號與基準電壓VREF進行比較。對于一個N bit分辨率的ADC,最后的數字輸出用模擬量表示為:

其中,BN-1,BN-2,…,B0為N bit ADC量化后的數字輸出結果。

其中VREF是ADC的滿量程參考電壓,當ADC的電容陣列切換時,會對VREF造成擾動,但下一次切換時,需要VREF恢復。因此,RVG電路需要有較大帶寬,并能提供大瞬態電流。目前的商用芯片中,有些芯片需要將VREF直接連接到電源電壓上,如意法半導體的STM32芯片[2],但是其缺點是ADC的滿量程電壓與電源電壓相關,不適用于電源電壓有較大波動的場景;有些芯片集成了內部參考電壓產生電路,可以產生出與電源電壓無關的參考電壓,但是沒有驅動能力,需要外接片外電容,啟動時間接近20 ms,如TI公司的MSP430[3]芯片;有些芯片中集成有內部參考電壓產生電路和緩沖器電路,但功耗很大,如NXP公司的KL17[4],ADC使用時,最大功耗高達1.7 mA。

本文提出了一種可以根據應用場景靈活選擇工作模式的片上RVG電路。

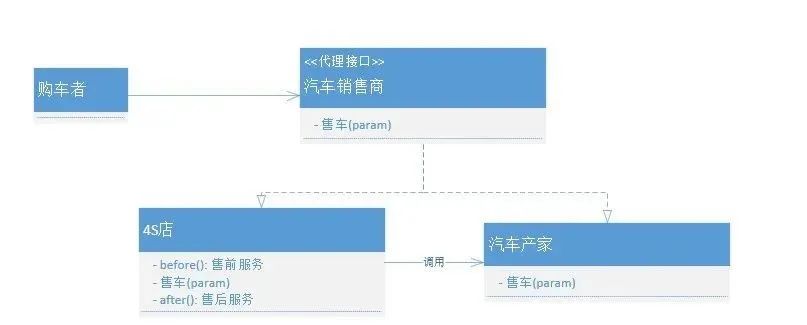

2 RVG電路原理

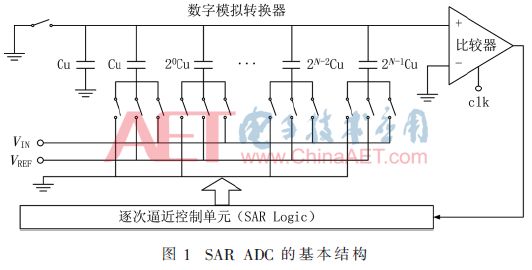

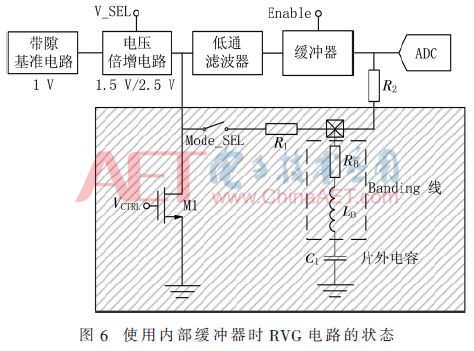

本文提出的ADC如圖2所示,芯片內部集成RVG電路。RVG電路包含:帶有斬波(chopper)功能的帶隙基準電路[5];可以提供1.5 V或2.5 V輸出電壓的電壓倍增電路;低通濾波器電路;帶有驅動能力的緩沖器(buffer)電路;模式選擇開關;電荷泄放開關M1;濾波與防閂鎖(latch up)電阻R1和R2;RB和LB是對Banding線的建模;C1是片外電容,大小定為10 μF。

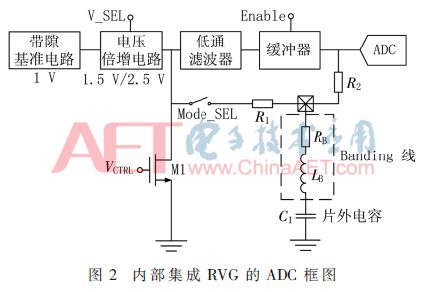

在工業物聯網的應用中,芯片的供電方式多樣,例如,電池供電、50 Hz交流電網取電等,如圖3所示。

靈活的供電方式增強了芯片的適應能力,但同時給芯片設計帶來很大挑戰。在互感器供電中,電源電壓會有10%的波動,需要電路有較好的電源抑制比;電池供電中,需要ADC在低至2.2 V的電源電壓下可以工作。

為了使ADC有較高的精度、較大的輸入范圍,希望ADC的參考電壓盡量大。在一些供電比較穩定的應用中,例如電源電壓保持在2.65 V~3.6 V以內,用戶可以選擇2.5 V模式為ADC提供參考電壓;在電源變化范圍較大的應用中,如電源電壓會在2.2 V~3.6 V之間波動,用戶可以選擇1.5 V參考電壓,雖然會降低了ADC的精度,但是保證了ADC在低電源電壓下功能正常。

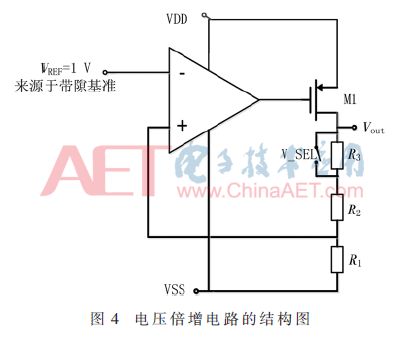

電壓倍增電路的結構如圖4所示,電壓選擇開關控制電阻R3是否接入電路。

當V_SEL=1時,R3被短路

此時輸出電壓為1.5 V。當V_SEL=0時,R3接入電路,R3=R1,此時電壓倍增電路的輸出電壓為2.5 V。

3 SAR ADC工作方式

在傳感器和工業物聯網中,SAR ADC一般集成在MCU中使用,根據應用場景的變化,整個MCU會在電池供電或電網取電的模式下工作,在不同場景下,ADC的工作模式不同,例如單點采樣的工作方式、連續采樣的工作方式。芯片對功耗的要求也不同,有對能量消耗嚴格的場景,如電池供電;有對功率要求的場景,如連續采樣或使用線圈耦合供電。采用本文提供的RVG電路,通過合理地選擇工作模式,可以分別在單次采樣應用和連續采樣應用中實現低功耗。

3.1 能量高效率應用模式

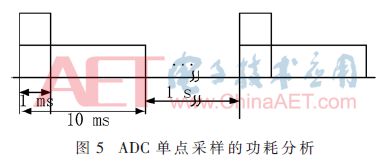

如果應用中對采樣頻率要求較低,例如,間隔1 s采集環境的溫度,ADC會采用單次采樣的模式,使能后進行一次采樣,立即關閉ADC的使能,進入關斷模式,等待下一次采樣。

單次采樣應用模式如圖5所示,ADC消耗的電荷不僅取決于ADC開啟時的電流,還取決于ADC完成一次轉換的時間。如圖5所示,ADC1(網狀曲線)開啟時功率較大,ADC2(斜線曲線)開啟時功率較小,假設ADC1的功率P1是ADC2的功率P2的兩倍,P1=2×P2,但ADC1采樣一次的時間為ADC2的0.1倍,即T1=0.1×T2。

ADC消耗的能量為E=P×T,所以E1=0.2×E2。

即雖然ADC1的功率較大,但是在單點采樣的工作方式下,消耗的能量僅為ADC2的1/5。

使用內部buffer時,如圖6所示,陰影中的電路處于關斷狀態。低通濾波器消除了帶隙基準電路的紋波,限制前面電路的噪聲;ADC中切換電容時造成的紋波,依靠緩沖器的環路穩定,因此,這種組態下,緩沖器的帶寬要求較高,功率很大。但是,使用內部buffer時,沒有大電容,整個電路的建立較快(<1 ms),相比于市場上使用片外電容的芯片接近20 ms的建立時間,建立時間縮短,一次采樣消耗的總能量減小。

仿真和測試結果表明,VREF可以在1 ms以內建立到ADC的1/2 LSB以內。

3.2 功率高效率應用模式

當芯片頻繁使用連續采樣時,對芯片的功率要求嚴格,可以配置成片外電容模式,ADC切換電容陣列時,片外電容為電容陣列提供瞬態電流。另外,大片外電容C1與R1同時構成了低通濾波器,可以濾除帶隙基準電路的chopper紋波和噪聲。這種應用方式,由于不需要開啟緩沖器,其功率較小;但是,由于每次開啟都需要給片外大電容充電,因此,其建立時間很長(<10 ms)。但RVG電路建立好后,可不再關閉,ADC可以連續運行。

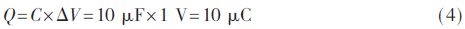

在使用片外電容的工作方式時,當電壓倍增電路從2.5 V模式向1.5 V模式切換時,需要進行電荷的泄放:

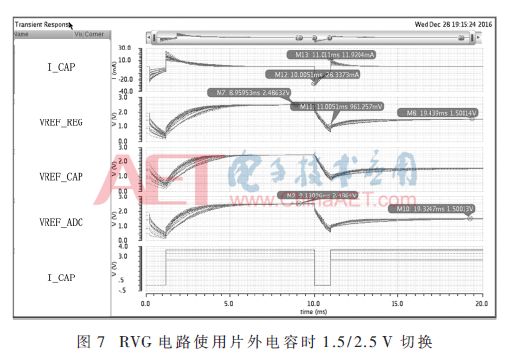

傳統設計中電荷只能通過圖4中所示的電阻串流過,為了降低靜態功耗,電阻串的電流設計為10 μA,要將10 μC的電荷泄放,需要長達1 s的時間。因此,在使用片外電容的應用方式中,當切換1.5 V/2.5 V的過程中,會將M1開關打開,快速泄放電容上的電荷。圖7是參考電壓電路開啟與切換的過程。

仿真中,對Banding線的寄生電容和電阻進行了建模,如圖6所示,LB=5 nH,RB=0.3 Ω。

圖7中的I_CAP分別為通過Banding線給片外電容充放電的電流,在放電階段,可以提供28 mA的放電電流,在參考電壓建立階段,可以提供12 mA的充電電流。參考電壓建立到ADC的精度范圍需要10 ms的時間。在參考電壓2.5 V到1.5 V的切換過程中,1 ms內,參考電壓可以從2.5 V降到1 V以下。

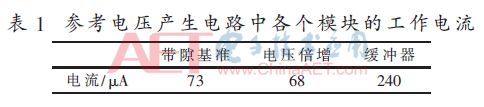

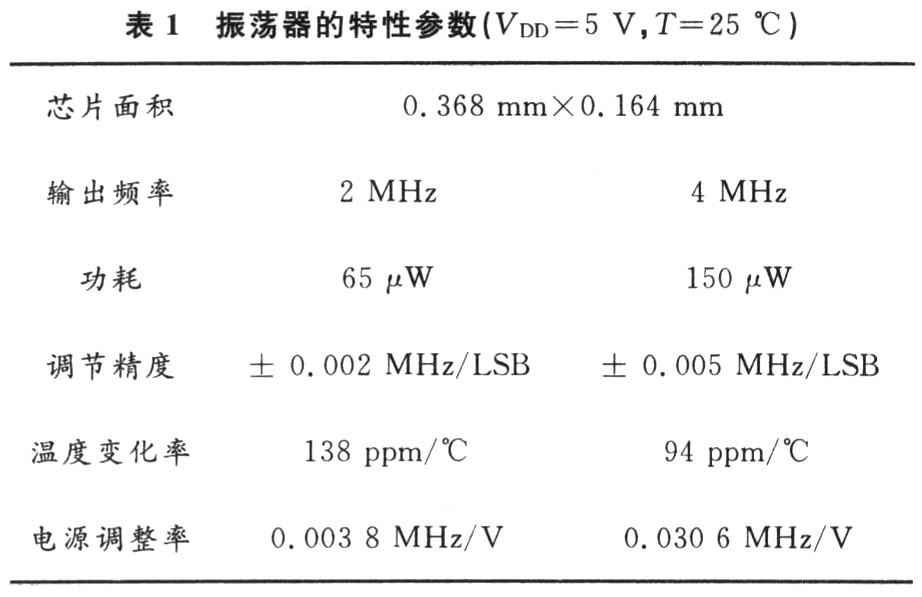

RVG中各個模塊的功耗見表1,片上低通濾波器使用MOS電阻和電容濾波,沒有靜態功耗。

結合前面的分析,如果ADC進行單點采樣,并每次采樣結束后關閉ADC所有電路,使用片外電容的應用方式,完成一次采樣需要1 410 nC的電荷;使用內部buffer的應用方式,完成一次采樣需要229 nC的電荷。如果使用電池供電,采用內部buffer應用方式,可以有效減小對電池的消耗,延長使用壽命,參考電壓產生電路不同應用方式下的參數如表2所示。

當ADC連續采樣,不需要關閉內部參考電壓產生電路時,使用片外電容的應用方式可以降低功耗。另外,如果芯片的供電模式是線圈取電,由于磁感應強度有限,對芯片的功率有一定限制,采用帶片外電容的應用模式可以降低其功率。

綜上所述,使用內部buffer是能量高效率的應用模式;而使用片外電容是功率高效率的應用模式。

4 芯片測試

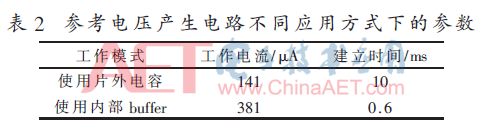

本芯片已經在TSMC180 nm工藝下流片,SAR ADC的版圖如圖8所示,其中虛線框部分為RVG電路,其余部分為SAR ADC。

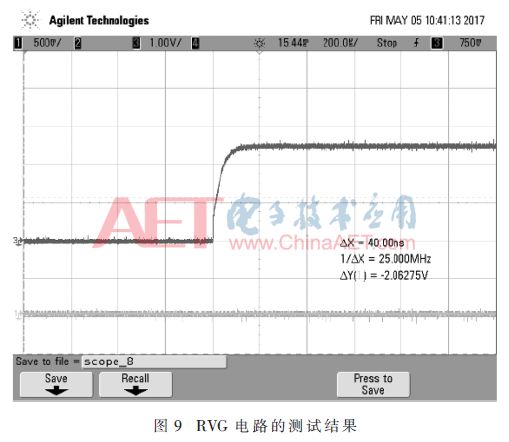

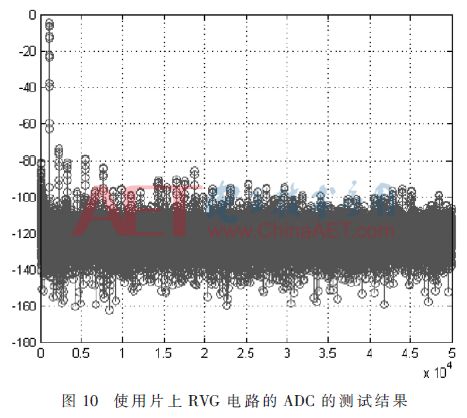

芯片測試結果如下,RVG電路的輸出電壓的啟動,穩定性滿足SAR ADC的需求,如圖9所示。使用片上集成的RVG電路,當芯片電源電壓在2.2 V~3.6 V時,電路均可正常工作,SAR ADC的信噪比可以達到66 dB,如圖10所示。

5 結論

針對工業物聯網芯片中供電情況復雜、ADC使用方式多樣功耗要求高的特點,提出了一種全集成多模式RVG電路,可以根據供電電壓范圍的不同,選擇1.5 V/2.35 V電壓輸出;可以根據ADC的應用方式配置成能量高效率模式和功率高效率模式。測試結果表明,該方案穩定性良好,能夠為ADC提供可靠的滿量程參考電壓。

-

adc

+關注

關注

98文章

6513瀏覽量

545022 -

數字電路

+關注

關注

193文章

1608瀏覽量

80689 -

工業物聯網

+關注

關注

25文章

2379瀏覽量

64451

原文標題:【學術論文】用于SAR ADC的片上多模式基準電壓產生電路的設計

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

STM32待機模式適合用于那些應用場景?

源測量單元設備的技術原理和應用場景

實時示波器的技術原理和應用場景

便攜式示波器的技術原理和應用場景

MOS管的應用場景

小容量OLT應用場景分析

FPGA的應用場景

一文區分Array與Vec的使用場景

一種片上系統復位電路的設計

MOS管工作在不同的區域時的應用場景是什么?

php設計模式和應用場景

TCXO四種輸出模式解析,應用場景廣泛選擇多

一種可以根據應用場景靈活選擇工作模式的片上RVG電路

一種可以根據應用場景靈活選擇工作模式的片上RVG電路

評論