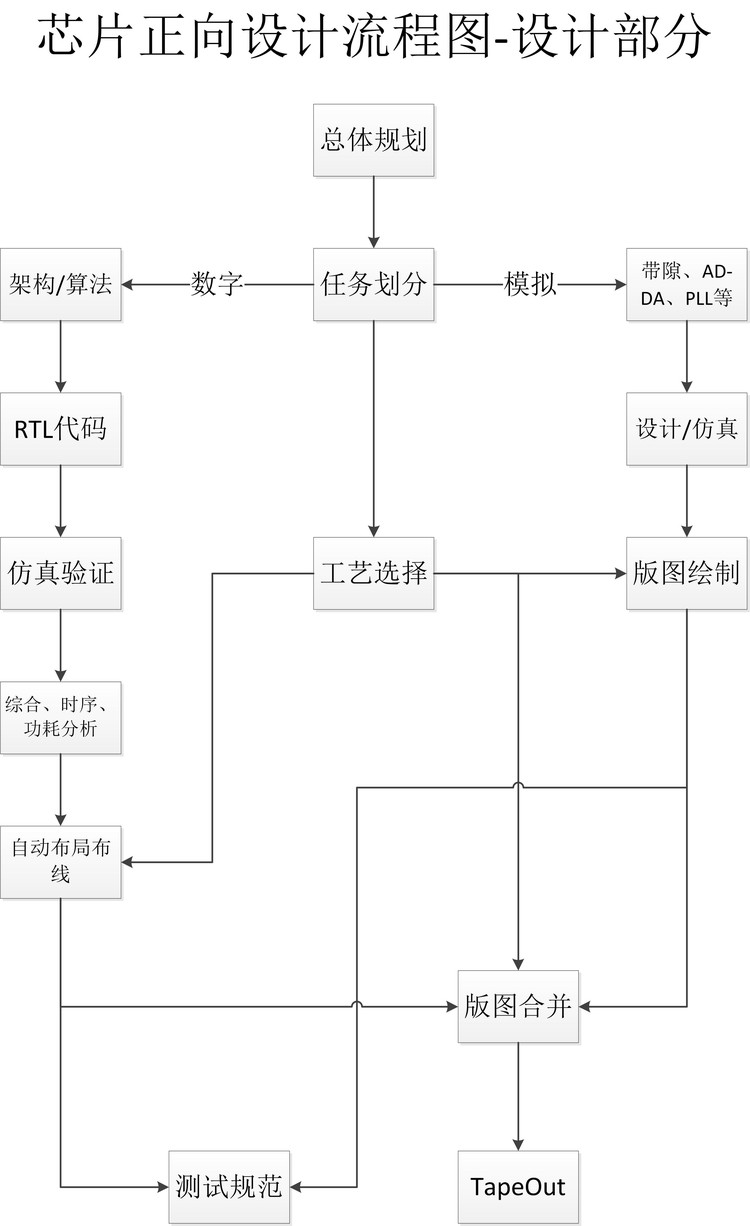

網(wǎng)絡(luò)上有很多人討論著芯片的反向設(shè)計,那么與之相對應(yīng)的芯片的正向設(shè)計是什么呢?它設(shè)計的具體流程又包括哪些?本文只要介紹的就是芯片的正向設(shè)計及其流程。

芯片的正向設(shè)計

在工程技術(shù)人員的腦海中,產(chǎn)品的設(shè)計過程都是從無到有,即在工程技術(shù)員的腦海中構(gòu)思產(chǎn)品的外形,技術(shù)參數(shù),性能等,然后通過繪制圖建立產(chǎn)品的三維數(shù)字化模型,最終將這個模型轉(zhuǎn)入到制造流程中,這就是芯片的正向設(shè)計。

芯片的正向設(shè)計流程

一、總體規(guī)劃

隨著集成電路設(shè)計規(guī)模的不斷擴大,出現(xiàn)了很多成熟的常用設(shè)計模塊,也被成為IP核,現(xiàn)在芯片正向設(shè)計,不再是完全從0開始,都是基于某些成熟的IP核,并在此基礎(chǔ)之上進行芯片功能的添加。真正從0開始設(shè)計的芯片,不是沒有,而是成本太高,企業(yè)無法承擔(dān),而且也并沒有必要從0開始設(shè)計。例如現(xiàn)在的ARM芯片開發(fā),那些大公司基本上是獲取ARM公司的授權(quán),得到ARM芯片的IP核,并根據(jù)細分市場的需求進行有針對性的開發(fā)。這是數(shù)字芯片的情況,模擬芯片的情況也是類似的,當(dāng)然我們并不能小看別人的原創(chuàng)能力,以為就是隨隨便便在別人的基礎(chǔ)上小修小補就可以設(shè)計出令人滿意的芯片,還有很多東西依然是需要豐富的經(jīng)驗和知識的。芯片正向設(shè)計依然是從市場未來需求著手,從開發(fā)成本和預(yù)期收益來衡量是否進行芯片的開發(fā)的。明確市場未來需求之后,就將這些需求轉(zhuǎn)化為芯片的各項重要參數(shù)指標(biāo),然后進行任務(wù)劃分,模擬設(shè)計師負責(zé)模擬,數(shù)字設(shè)計師負責(zé)數(shù)字。個人對于模擬部分不太熟,所以就略過。重點總結(jié)數(shù)字設(shè)計部分,當(dāng)然這部分也不是很熟,因為沒有真正做過。

二、架構(gòu)/算法

現(xiàn)在數(shù)字電路在芯片中占有極大的比重,數(shù)字邏輯也變得越來越復(fù)雜,所以必須從架構(gòu)和算法上進行考慮。個人所略知的關(guān)于芯片架構(gòu)的是,架構(gòu)可以分為三種大的方向:

1,數(shù)據(jù)流;

2,控制流,

3,總線流。數(shù)據(jù)流:數(shù)據(jù)從輸入到輸出是一條直線,并沒有折回的數(shù)據(jù),這是純數(shù)據(jù)處理的一種架構(gòu),這種芯片功能應(yīng)該是比較單一。

2,控制流,這是基于狀態(tài)機或者CPU形式的一種架構(gòu)設(shè)計。簡單點的芯片就采用狀態(tài)機就夠了,復(fù)雜的就必須采用CPU作為控制內(nèi)核了,比如單片機就是以CPU為控制內(nèi)核,外加RAM,ROM所形成的一類控制類芯片。

3,總線流,這是基于總線的芯片設(shè)計架構(gòu),最熟悉的就是SOC類芯片,總線上連接著一個或多個CPU,RAM,ROM,I2C,UART等等之類的各種組件。由這些組件的不同排列組合,形成滿足各種不同需求的芯片,例如不同的ARM類芯片。

算法,我所略知的是通信類的,例如,F(xiàn)IR,FFT,小波變換,三角函數(shù)變換等等,當(dāng)然還有視頻音頻類的算法,對與這方面的內(nèi)容就沒有接觸過了。總的來說,這類算法都是以數(shù)據(jù)處理為主要目的的,所以這些算法都要求有較強的數(shù)學(xué)功底。做算法開發(fā),主要工具為MATLAB,都是先在MATLAB上做原型開發(fā)驗證,再轉(zhuǎn)化為RTL級的代碼。

結(jié)合架構(gòu)和算法,將芯片的總體結(jié)構(gòu)搭建出來,為后續(xù)的工作做好了準(zhǔn)備。

三、RTL代碼

當(dāng)算法工程師把芯片架構(gòu)設(shè)計好,各種算法在MATLAB上通過了驗證,以及其他必要條件的考量之后,便將工作交接給ASIC工程師去做RTL代碼的翻譯工作,就是將MATLAB上的算法翻譯成RTL。這一步單純從翻譯的角度只需要一個文本編輯器就可以了。然而,還有后續(xù)的仿真驗證工作,這部分的內(nèi)容并不輕松。有時候根據(jù)公司的不同,根據(jù)項目的工作量大小,算法工程師與ASIC工程師在工作內(nèi)容上是有交叉的,他們也承擔(dān)將MATLAB轉(zhuǎn)換為RTL的工作。RTL設(shè)計的時候也會考慮DFT(Design For Test 可測性設(shè)計)的問題,會在RTL代碼中加入測試鏈,這個我就不太熟了。

四、仿真驗證

這一步的工作比較關(guān)鍵,可以說是設(shè)計部分的第一個分水嶺。仿真驗證,視不同的公司,不同的項目,復(fù)雜度有非常大的不同。簡單的,只要寫一個較為完善的testbench驗證完RTL代碼的功能就行了;復(fù)雜的,將會在RTL驗證環(huán)境下進行詳細的驗證,甚至可能用得到各種驗證方法學(xué)UVM,VMM,OVM等等,這種復(fù)雜驗證所用的語言一般采用SystemVerilog。驗證軟件可以采用cadence公司的NC_VERILOG,或者synopsys公司的VCS。此外,某些芯片還會采用FPGA,進行硬件在線仿真。這樣能夠獲取關(guān)于芯片的更為詳細的信息。但不管如何,無論是個人還是公司,都應(yīng)該有對于仿真驗證工作的一套完整和完善的流程方案。

五、工藝選擇

正向設(shè)計在一開始的整體規(guī)劃中就要考慮工藝的問題,這涉及到有關(guān)工藝的相關(guān)知識,有些工藝就是特別為某種類型的芯片而開發(fā)的。所以一旦是要開發(fā)某種有對應(yīng)工藝的芯片,則直接采用即可,但往往工藝的選擇會特別耗時間,會有各種參數(shù)的考量,例如工藝生產(chǎn)周期,工藝的成品率,工藝生產(chǎn)時間的安排等等各方面的考究。這部分,需要花費特別多的時間。工藝由芯片制造廠提供,前提是必須和芯片制造廠有合作關(guān)系。

六、綜合、時序&功耗分析

這一步是在RTL仿真驗證完之后進行,當(dāng)然還有一個前提,制造工藝必須選定,否則,如果中途換了工藝,這部分的工作還得重新來做,這樣將會消耗特別多的時間。這部分的工作主要用到synopsys公司的工具Design Complier(綜合)、Prime Time(時序和功耗)。這兩個工具的使用比較復(fù)雜,使用說明參考百度文庫相關(guān)資料。總體來說,這兩個工具都是約束驅(qū)動型軟件,軟件在使用時都是靠約束文件來進行驅(qū)動的。所以工作的主要內(nèi)容除了軟件的使用外最重要的就在于如何編寫約束文件。一般而言,約束主要有面積約束,扇入扇出約束,時序約束等約束條件。如果RTL代碼不滿足約束,則必須根據(jù)具體情況修改約束條件或者是修改RTL代碼。約束條件是用TCL腳本語言來寫。綜合和時序分析會生成基于所采用的工藝的電路網(wǎng)表,這個網(wǎng)表將是下一步自動布局布線所用到的主文件。

主要工作內(nèi)容:

1、準(zhǔn)備好選定的工藝庫文件(綜合網(wǎng)表文件、時序文件庫);

2、根據(jù)設(shè)計要求編寫TCL約束腳本;

3,操作軟件,生成約束報告;

4,分析約束報告,修改或調(diào)整不合理的約束或者修改RTL代碼(RTL代碼不會輕易修改,這要求在RTL設(shè)計時就要考慮這些約束要求,以便于能夠通過約束分析)。

七、 形式驗證

綜合出來的網(wǎng)表正確與否如何判定呢?這需要用到形式驗證技術(shù),該技術(shù)與RTL的仿真不同,它是從數(shù)理邏輯出發(fā),來對比兩個網(wǎng)表在邏輯上的等效性。如果等效,則綜合的網(wǎng)表就是符合要求的。用到的工具為synopsys 公司的Formality 形式驗證工具。其實,形式驗證是在每一次芯片的邏輯電路轉(zhuǎn)換為另一種表達形式的時候都需要做的工作。具體來說,在綜合生成網(wǎng)表后做一次,主要對比的文件為RTL仿真之后的文件和綜合之后的網(wǎng)表,在布局布線之后還需要做一次,主要對比文件為綜合之后的網(wǎng)表與布局布線之后的網(wǎng)表。主要工作內(nèi)容:

1、準(zhǔn)備好待比較的兩份文件及各種工藝技術(shù)庫文件;

2、用TCL腳本編寫腳本程序,設(shè)置其中一份文件為比較標(biāo)準(zhǔn),其中一份為待比較文件;

3、運行Formality,分析生成的比較報告;

八、自動布局布線

這個步驟嚴重依賴于軟件和經(jīng)驗,目前常用的軟件為Cadence Encounter不同版本的自動布局布線軟件名字可能不一樣。Synopsys公司也有對應(yīng)的自動布局布線的軟件ASTRO,最新版本為ICC套件。軟件的使用同樣可以在網(wǎng)上找到相關(guān)資料,這里就不細說了。主要工作內(nèi)容:

1、準(zhǔn)備好工藝文件(時序文件庫 數(shù)字版圖庫);

2,準(zhǔn)備好綜合之后的電路網(wǎng)表文件及約束文件;

3,根據(jù)設(shè)計要求,設(shè)置好版圖面積等相關(guān)參數(shù),

4,進行自動布局布線,檢查時序和功耗,如果不滿足要求,則再次修改相關(guān)參數(shù),直到符合設(shè)計要求為止。

自動布局布線需要注意的是:數(shù)字信號一定要關(guān)注好關(guān)鍵路徑的延時問題,這一點曾經(jīng)是數(shù)字設(shè)計的關(guān)鍵問題。現(xiàn)在,據(jù)說,時序已經(jīng)不再是芯片設(shè)計的主要難題了,主要難題已經(jīng)轉(zhuǎn)移到了功耗上,在設(shè)計的每一個階段都要考慮功耗的問題。

模擬部分似乎是沒有數(shù)字部分那么多的工具需要使用,但模擬部分的電路設(shè)計最考究的還是工程師們的設(shè)計經(jīng)驗,而這些經(jīng)驗都是要靠時間才能堆出來的。模擬電路的每一個模塊都需要很多的時間去驗證,比說一個高性能的放大器,一個與工藝和電壓無關(guān)的帶隙基準(zhǔn)等等。模擬的版圖只能是一個一個管子的畫,沒有自動布局布線的必要,因為模擬電路的管子也不會很多。

剩下的工作就是合并整體的版圖,并進行DRC、LVS的各種驗證,通過之后就可以tapeout。之后再制定測試規(guī)范,這與反向設(shè)計的剩余步驟是一樣的。另外,有時候版圖還需要做ECO(Engineering Change Order)工程修改命令,是指在原有的設(shè)計 的基礎(chǔ)上如果要作一些改動,可不必從頭再來,可以在原來的布局上通過eco步驟快捷地 完成設(shè)計。

總結(jié)

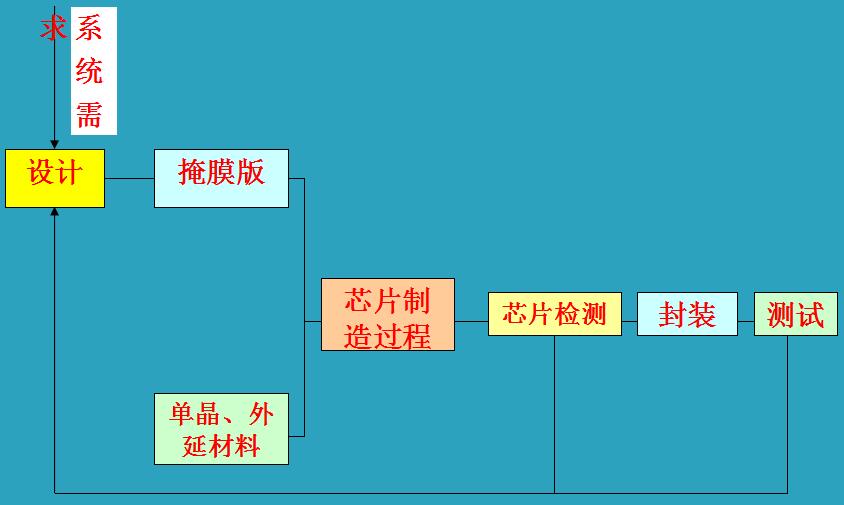

傳統(tǒng)以來,工業(yè)產(chǎn)品的開發(fā)均是循著序列嚴謹?shù)难邪l(fā)流程,從功能與規(guī)格的預(yù)期指標(biāo)確定開始,構(gòu)思產(chǎn)品的零組件需求,再由各個元件的設(shè)計、制造以及檢驗零組件組裝、檢驗整機組裝、性能測試等程序來完成,此為芯片正向設(shè)計的由來。

-

芯片

+關(guān)注

關(guān)注

456文章

51059瀏覽量

425701 -

數(shù)字化

+關(guān)注

關(guān)注

8文章

8820瀏覽量

61995

發(fā)布評論請先 登錄

相關(guān)推薦

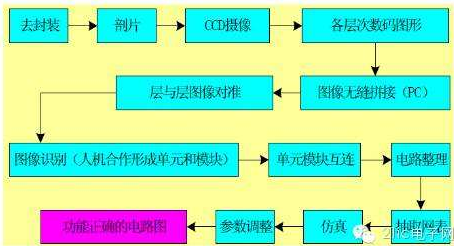

一文詳解芯片逆向工程的設(shè)計與流程

芯片的具體設(shè)計流程又是什么?

什么是芯片反向設(shè)計?深度解析芯片反向設(shè)計流程

芯片的反向設(shè)計和正向設(shè)計的區(qū)別

芯片的設(shè)計流程全方位詳細解讀

芯片的具體設(shè)計流程

芯片設(shè)計流程 芯片的設(shè)計原理圖

芯片設(shè)計流程概述

語音芯片燒錄流程概述

數(shù)字設(shè)計ic芯片流程

芯片封測架構(gòu)和芯片封測流程

什么是芯片正向設(shè)計?芯片設(shè)計的具體流程解析

什么是芯片正向設(shè)計?芯片設(shè)計的具體流程解析

評論