設計背景:

數字時鐘的設計,在我們的好多設計中都有過這樣那樣的設計,這基本屬于一個比較精簡的一個小項目,可以練習我們學到的好多知識點。

設計原理:

本次的設計主要還是為了結合我們所學到的知識,因為我們學到的知識要經常的用,并不是我們不用,一直在用我們就可以加深我們的想法和思路,這也是一種良好的學習態度。

我設計的數字鐘是這樣的一種架構,我又3個按鍵,上電后,我們需要先配置我們的時分秒,我的設計是一個按鍵來控制我們的時,一個按鍵來控制我們的分,秒我沒有控制,因為我比較懶,大家可以自己取設計控制一下我們的設計,那么然后是這樣的,第三個按鍵來控制我們時鐘的運行,也就是說當我們用2個那件配置好了我們的時鐘的時候,按下這個開始按鍵,我們的時鐘就開始工作了。

那么我們就在來討論一下我們的按鍵模塊,我們的按鍵模塊是這樣的,因為按鍵有抖動,我加入按鍵消抖,和邊沿檢測電路,這樣我們就實現了按鍵的消抖,用到的也就是我們前面設計的知識。

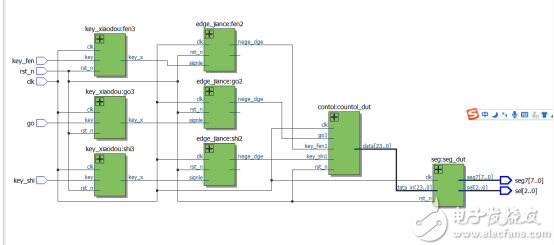

設計架構圖:

寫好一個模塊,我們可以任意例化幾次都是可以的,目前還不用考慮別的,三個按鍵就例化了三次我們的按鍵消抖和邊沿檢測。

設計代碼:

設計模塊

0moduletime_seg(clk,rst_n,sel,seg7,key_fen,key_shi,go);

1

2 inputclk;

3 inputrst_n;

4

5 inputkey_fen; //控制分的按鍵

6 inputkey_shi; //控制時的按鍵

7 inputgo; //控制時鐘運行的按鍵

8 output[2:0]sel;

9 output[7:0]seg7;

10

11 wire[23:0]data_in;

12

13

14seg seg_dut( //例化我們的數碼管模塊

15 .clk(clk),

16 .rst_n(rst_n),

17 .sel(sel),

18 .seg7(seg7),

19 .data_in(data_in)

20 );

21 wiref_fen,f_shi,f_go;

22contol countol_dut( //例化我們的控制模塊

23 .clk(clk),

24 .rst_n(rst_n),

25 .data(data_in),

26 .key_fen1(f_fen),

27 .key_shi1(f_shi),

28 .go1(f_go)

29 );

30 wirefen_x,shi_x,go_x;

31key_xiaodou shi3( //例化3次消抖

32 .clk(clk),

33 .rst_n(rst_n),

34 .key(key_shi),

35 .key_x(shi_x)

36 );

37key_xiaodou fen3(

38 .clk(clk),

39 .rst_n(rst_n),

40 .key(key_fen),

41 .key_x(fen_x)

42 );

43

44key_xiaodou go3(

45 .clk(clk),

46 .rst_n(rst_n),

47 .key(go),

48 .key_x(go_x)

49 );

50

51edge_jiance shi2( //例化3次邊沿檢測電路

52 .clk(clk),

53 .rst_n(rst_n),

54 .signle(shi_x),

55 .nege_dge(f_shi),

56 .pose_dge()

57 );

58edge_jiance fen2(

59 .clk(clk),

60 .rst_n(rst_n),

61 .signle(fen_x),

62 .nege_dge(f_fen),

63 .pose_dge()

64 );

65edge_jiance go2(

66 .clk(clk),

67 .rst_n(rst_n),

68 .signle(go_x),

69 .nege_dge(f_go),

70 .pose_dge()

71 );

72

73endmodule

控制模塊:

0modulecontol(clk,rst_n,data,key_fen1,key_shi1,go1);

1

2 inputclk;

3 inputrst_n;

4 inputkey_fen1; //輸入端口

5 inputkey_shi1;

6 inputgo1;

7

8 outputreg[23:0]data; //輸出的端口

9

10

11 reg[26:0]count;

12

13 always@(posedgeclk ornegedgerst_n) //1秒的計數器

14 if(!rst_n)

15 begin

16 count <=26'd0;

17 end

18 else

19 begin

20 if(count ==50_000_000)

21 count <=26'd0;

22 else

23 begin

24 count <=count +1'd1;

25 end

26 end

27

28 wireflag;

29

30 assignflag =(count ==50_000_000)?1'b1:1'b0; //計數到了1S給一個高脈沖

31

32 reg[1:0]state;

33 always@(posedgeclk ornegedgerst_n)

34 if(!rst_n)

35 begin

36 data <=0;

37 state <=0;

38 end

39 else

40 case(state)

41 0:begin

42 if(key_fen1) //調節分

43 begin

44 data[11:8]<=data[11:8]+1;

45 if(data[11:8]==9)

46 begin

47 data[11:8]<=4'd0;

48 data[15:12]<=data[15:12]+1'b1;

49 if(data[15:12]==5)

50 data[15:12]<=0;

51 end

52 end

53 elseif(key_shi1) //調節時

54 begin

55 data[19:16]<=data[19:16]+1;

56 if(data[19:16]==9&&data[23:20]!=1)

57 begin

58 data[19:16]<=4'd0;

59 data[23:20]<=data[23:20]+1'b1;

60 if(data[23:20]==1)

61 data[23:20]<=0;

62 end

63 elseif(data[19:16]==2&&data[23:20]==1)

64 begin

65 data[19:16]<=0;

66 data[23:20]<=0;

67 end

68 end

69 elseif(go1) //讓我們的時鐘啟動

70 begin

71 state <=1;

72 end

73 else

74 state <=0;

75 end

//一層一層的嵌套設計,讓我們的秒一個一個的來驅動

76 1:begin

77 if(flag )

78 begin

79 data[3:0]<=data[3:0]+1;

80 if(data[3:0]==9) //秒的個位

81 begin

82 data[3:0]<=4'd0;

83 data[7:4]<=data[7:4]+1'b1;

84 if(data[7:4]==5) //秒的時位

85 begin

86 data[7:4]<=4'd0;

87 data[11:8]<=data[11:8]+1'b1;

88 if(data[11:8]==9) //分的個位

89 begin

90 data[11:8]<=4'd0;

91 data[15:12]<=data[15:12]+1'b1;

92 if(data[15:12]==5) //分的十位

93 begin

94 data[15:12]<=4'd0;

95 data[19:16]<=data[19:16]+1'b1;

96 if(data[19:16]==9&&data[23:20]!=1)//時的計算

97 begin

98 data[23:20]<=4'd0;

99 data[23:20]<=data[23:19]+1'b1;

100 if(data[23:20]==1)

101 data[23:20]<=4'd0;

102 end

103 elseif(data[19:16]==2&&data[23:20]==1)//如果到12小時制

104 begin

105 data[19:16]<=0;

106 data[23:20]<=0;

107 end

108 end

109 end

110 end

111 end

112 end

113 end

114

115 default:;

116 endcase

117

118

19 endmodule

這邊我就不給大家仿真了,后續我會給大家發一個完整的工程,建議大家可以自己例化我的設計。

-

FPGA

+關注

關注

1630文章

21777瀏覽量

604686

發布評論請先 登錄

相關推薦

FPGA加速深度學習模型的案例

FPGA做深度學習能走多遠?

FPGA如何消除時鐘抖動

源碼系列:基于FPGA的數字電壓表(AD)設計

紫光同創PGL22G開發板|盤古22K開發板,國產FPGA開發板,接口豐富,高性價比

FPGA的時鐘電路結構原理

FPGA學習筆記-入門

FPGA初步學習印象

FPGA學習資料分享

種草一塊國產FPGA開發板,不用燒錄器,一根TypeC線即插即用,盤古EU22K開發板

FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么?

FPGA的數字時鐘電路解析

FPGA時鐘內部設計方案

FPGA學習系列:22. 數字時鐘的設計

FPGA學習系列:22. 數字時鐘的設計

評論