多年來,高速信號(hào)轉(zhuǎn)換系統(tǒng)中的模數(shù)轉(zhuǎn)換器(ADC)所使用的典型流水線架構(gòu)包含了取樣波形所需的所有功能,這些功能被集成進(jìn)同一封裝中:

1. 某種形式的跟蹤保持電路,可保持用于轉(zhuǎn)換的信號(hào);

2. 內(nèi)置參考和偏置電流;

3. 時(shí)鐘緩沖器和較小的數(shù)字電路,可將來自各級(jí)電路的比特組成無誤碼的數(shù)據(jù)字。

在大多數(shù)情況下,這些轉(zhuǎn)換器中的可編程性僅限于通過一個(gè)休眠管腳打開/關(guān)閉轉(zhuǎn)換器,或通過在雙補(bǔ)碼(two's complement)或偏移二進(jìn)制碼(offset binary)輸出格式中選擇一種格式。

系統(tǒng)內(nèi)調(diào)整

隨著ADC速度和通道密度的提高,數(shù)字輸出驅(qū)動(dòng)電平和終端電阻的系統(tǒng)內(nèi)調(diào)整有助于保證高數(shù)據(jù)速率時(shí)的數(shù)字信號(hào)完整性。對(duì)具有串行低壓差分信號(hào)(LVDS)輸出的ADC來說更是如此。在沒有輸入信號(hào)的情況下,通過從ADC輸出端提供一個(gè)數(shù)字激勵(lì)信號(hào),就可以在輸出總線上發(fā)送練習(xí)模型。這樣做可以確保多個(gè)數(shù)字組成得到正確的連接。即使是信噪比(SNR)和無雜散動(dòng)態(tài)范圍(SFDR)之間的性能折衷也可以通過寄存器調(diào)整實(shí)現(xiàn)。

目前已有一些流水線式ADC具備了增強(qiáng)的可編程能力,例如TI公司的ADS*5。在該器件中,4個(gè)14位、125兆樣本/秒的ADC、以及用戶可編程性都被集成在單一的9×9mm封裝內(nèi),因此比起采用多個(gè)ADC、每個(gè)ADC包含一個(gè)轉(zhuǎn)換器、整體體積更大的方案,該器件使用起來更容易。ADS*5還有許多特性可用于精確調(diào)整數(shù)字接口,以及實(shí)現(xiàn)SNR和SFDR之間的系統(tǒng)折衷。這正是系統(tǒng)內(nèi)可編程能力存在的真正價(jià)值。

一旦定義好ADC和下游數(shù)字器件之間的鏈路并在板上建立起來,通過串行可編程接口(SPI)調(diào)整ADC的能力,就可以把以前要數(shù)周的調(diào)試時(shí)間縮短到5分鐘。如果沒有這種可編程能力,那就可能需要設(shè)計(jì)多個(gè)電路板才能解決意外的數(shù)字信號(hào)完整性或時(shí)序問題。

可調(diào)整的LVDS接口

可以通過ADS*5中的SPI調(diào)整寄存器設(shè)置中的LVDS電流等級(jí),以優(yōu)化低阻抗或互連匹配不良的差分信號(hào)完整性。這些調(diào)整可以在板子制造出來后進(jìn)行。LVDS信號(hào)完整性在LVDS傳輸路徑末端進(jìn)行表征。

例如,圖1就是只有5pF負(fù)載電容的一個(gè)LVDS數(shù)據(jù)輸出位的示波器圖形。LVDS輸出驅(qū)動(dòng)強(qiáng)度被設(shè)為3.5mA進(jìn)入板上100歐姆電阻,觸發(fā)頻率為~375MHz。這些是正常的LVDS設(shè)置。在高速和更長(zhǎng)距離時(shí),LVDS信號(hào)中可能會(huì)發(fā)生反射,從而減小數(shù)據(jù)有效窗口,破壞接收器件識(shí)別正確轉(zhuǎn)換信號(hào)的能力。這種信號(hào)完整性問題正在圖1中發(fā)生。

圖1:LVDS的電容負(fù)載5pF,以額定的3.5mA進(jìn)入板上接收端100歐姆的電阻。

有幾種方法可以解決這個(gè)問題,它們除了訪問ADC的SPI外沒有其他任何要求。你可以將LVDS輸出電路中的內(nèi)部負(fù)載電阻作為源負(fù)載來終結(jié)傳輸線。這會(huì)在LVDS輸出端形成一個(gè)50歐姆的負(fù)載(兩個(gè)100歐姆電阻并聯(lián))。因此,額定的3.5mA電流形成的信號(hào)幅度是700mVpp額定輸出電壓的一半。

更低的差分信號(hào)電平本身會(huì)導(dǎo)致與上述劣化信號(hào)同樣多的檢測(cè)錯(cuò)誤,但只要LVDS接收器具備必要的靈敏度,那么對(duì)許多系統(tǒng)來說就沒有問題。

如果要求更高的LVDS擺幅,可以設(shè)置ADS*5讓LVDS輸出電流翻倍到7mA(圖2),從而使信號(hào)回到700mVpp。電容負(fù)載也從5pF(圖1)提高到10pF(圖2),進(jìn)一步彰顯了額外電流和雙倍終端信號(hào)的好處。在圖2中,所有轉(zhuǎn)化現(xiàn)在都沒有反射能量。

圖2:LVDS的電容負(fù)載10pF,以的7mA進(jìn)入板上接收端50歐姆的電阻。

就像驅(qū)動(dòng)能力可以根據(jù)要求增加一樣,在LVDS信號(hào)完整性允許的條件下,也可以降低驅(qū)動(dòng)能力以便節(jié)省功耗。為了節(jié)省功率,如果滿幅700mVpp沒必要的話,或者距離可能很短、ADC和數(shù)字器件之間的負(fù)載也很小,那么就可以改變LVDS輸出電流和負(fù)載電阻。

根據(jù)不同的期望結(jié)果,這樣做有幾大好處。在信號(hào)速率不是特別高、電容負(fù)載又低的情況下,可以使用低于3.5mA標(biāo)準(zhǔn)的幾種電流設(shè)置之一、以及大于100歐姆的內(nèi)部負(fù)載電阻(甚至無需額外的負(fù)載電阻,進(jìn)而節(jié)省費(fèi)用和空間),這樣仍能建立可靠的鏈接。

在信號(hào)完整性允許的情況下,一種節(jié)省功耗的方法是選用142歐姆的內(nèi)部LVDS差分負(fù)載和2.5mA的LVDS電流。在這種組合設(shè)置下仍能達(dá)到約700mVpp。通常,在條件有保證的情況下,建議為L(zhǎng)VDS路徑末端的差分終端電阻提供一塊空間。對(duì)于短路徑來說可能沒有必要,ADC里的內(nèi)部源端的終端電阻已經(jīng)足夠。

LVDS規(guī)范允許LVDS源的差分輸出處于247到454mV峰值范圍內(nèi)的任一點(diǎn)。其他組合也可能用于增加或減少仍處于TIA/EIA/ANSI-* LVDS規(guī)范內(nèi)的LVDS驅(qū)動(dòng)強(qiáng)度和電壓電平。你可以從系統(tǒng)概念開始就選擇這些特性以便節(jié)省功率。另外,它們也可以在LVDS信號(hào)完整性問題被意外發(fā)現(xiàn)時(shí)僅用作保障措施。

這些特性可以在發(fā)生問題時(shí)節(jié)省大量板級(jí)調(diào)試的時(shí)間和費(fèi)用。要看清楚LVDS接收器件要求的電壓值。因?yàn)槊繅K板都是不同的,你可能需要對(duì)ADC編程以便調(diào)整LVDS輸出電平。這可以在電路板信號(hào)丟失被表征和考慮后,在LVDS接收端來維持允許的范圍。

內(nèi)置測(cè)試模型

ADS*5提供了多種內(nèi)置的測(cè)試模型,可以在沒有模擬輸入源的時(shí)候使用。這些模型可以在初始電路板調(diào)試時(shí)用來考察ADC和FPGA之間的時(shí)序關(guān)系,以便確定FPGA接口處正確的時(shí)鐘與數(shù)據(jù)關(guān)系。這能確保有良好的時(shí)序(時(shí)序通常可以在FPGA LVDS輸入信號(hào)中調(diào)整)。

與提供模擬信號(hào)相比,使用內(nèi)置練習(xí)模型的一個(gè)好處是模型具有一致性,因此可以排除模擬源帶來的任何誤差問題,使實(shí)驗(yàn)具有可重復(fù)性,也更容易建立。練習(xí)模型也可以在電路板制造與測(cè)試過程中用作電路板功能測(cè)試的一部分。

信號(hào)增益、SNR和SFDR

可編程性不僅僅能解決板級(jí)互連問題,一些特性還可以用來實(shí)現(xiàn)系統(tǒng)性能折衷。舉例來說,ADS*5也有內(nèi)部模擬輸入信號(hào)增益功能,允許犧牲SNR來提高SFDR,或只是降低模擬輸入幅度。

ADS*5既有粗略增益調(diào)整也有精細(xì)增益調(diào)整。在這兩種情況下,模擬輸入電壓值必須至少要減去ADC中所選取的增益值。這樣可以保持ADC的輸入電壓范圍,避免讓數(shù)字輸出字飽和或削減。因此,如果你想使用ADC中的增益設(shè)置進(jìn)行開發(fā),最好要在ADC之前的模擬電路中就計(jì)劃減少板級(jí)模擬輸入信號(hào)的電平。

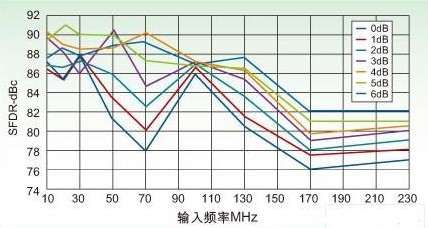

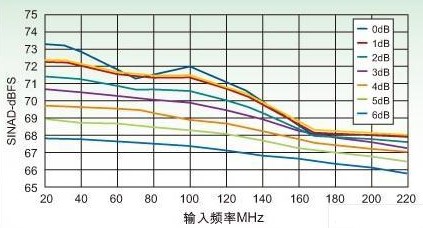

從圖3和圖4可以看出,折衷在輸入信號(hào)電平和使用兩種不同增益調(diào)整方法導(dǎo)致的失真(或這里特指的SFDR)之間是顯而易見的。這個(gè)特性可用來獲得多重對(duì)象。對(duì)于能利用數(shù)字抽取技術(shù)恢復(fù)SNR的窄帶系統(tǒng)來說,根據(jù)涉及的輸入頻率,可以通過降低轉(zhuǎn)換器中的SNR來改善SFDR。

圖3:使用精細(xì)增益控制時(shí)SFDR與輸入頻率的對(duì)比。

圖4:使用粗略增益控制時(shí)SFDR與輸入頻率的對(duì)比

另外,通過允許更小的輸入信號(hào)進(jìn)入ADC,同時(shí)仍保持來自ADC的全刻度代碼,驅(qū)動(dòng)ADC的模擬電路就可能改善失真,并為放大器和ADC整合電路創(chuàng)建更好的SFDR。

可以在創(chuàng)建原型的階段就使用這個(gè)特性,以便確定輸入信號(hào)電平的最佳組合,從而無需設(shè)計(jì)多塊電路板就能取得最佳的系統(tǒng)失真。可以在系統(tǒng)中動(dòng)態(tài)地進(jìn)行增益調(diào)整,并一道使用自動(dòng)增益控制(AGC)來恢復(fù)盡可能多的動(dòng)態(tài)范圍。還可以通過一個(gè)封裝引腳實(shí)現(xiàn)粗略的3.5dB增益設(shè)置,以便用于那些沒有SPI但想要調(diào)整ADC增益的應(yīng)用,附加的內(nèi)部寄存器子集也是如此。

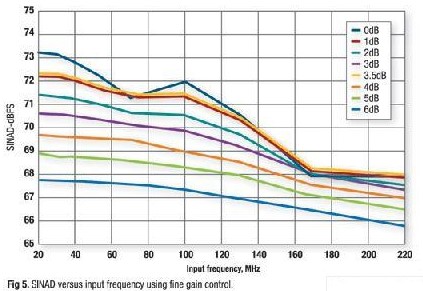

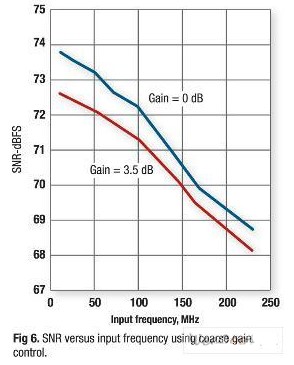

圖5和圖6給出了信號(hào)-噪聲及失真比(SINAD),以及與A/D轉(zhuǎn)換器的內(nèi)部增益設(shè)置有關(guān)的SNR減少的情況。

圖5:使用精細(xì)增益控制時(shí)SINAD與輸入頻率的對(duì)比

圖6:使用粗略增益控制時(shí)SNR與輸入頻率的對(duì)比

由于高速A/D轉(zhuǎn)換器的可編程性越來越強(qiáng),它們對(duì)用戶的友好程度也越來越高。對(duì)那些厭煩SPI方法或編程的傳統(tǒng)模擬硬件設(shè)計(jì)師來說,該ADC仍可以使用默認(rèn)的設(shè)置,直接簡(jiǎn)單的忽略掉其可編程特性。

高速ADC是模擬和數(shù)字硬件之間的橋梁,它經(jīng)常由全數(shù)字或全模擬硬件設(shè)計(jì)師負(fù)責(zé)。此時(shí),數(shù)字硬件設(shè)計(jì)師更容易接受其可編程特性,但它也可以幫助那些無法正確建立數(shù)字時(shí)序或信號(hào)完整性的模擬硬件設(shè)計(jì)師節(jié)省寶貴的時(shí)間。

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8741瀏覽量

147727 -

緩沖器

+關(guān)注

關(guān)注

6文章

1929瀏覽量

45583 -

adc

+關(guān)注

關(guān)注

99文章

6532瀏覽量

545424

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

可編程交流負(fù)載標(biāo)準(zhǔn)

什么是可編程邏輯

時(shí)鐘的重要性

高速可編程遙感衛(wèi)星數(shù)據(jù)模擬源的設(shè)計(jì)與實(shí)現(xiàn)

可編程SoC(SoPC),什么是可編程SoC(SoPC)

LabVIEW可編程FPGA模塊對(duì)示波器的重要性

實(shí)現(xiàn)重要分析與硬件加速的可編程Xilinx zynq-7000平臺(tái)推薦

可編程電源的原理 可編程電源的優(yōu)缺點(diǎn)

下一代安全設(shè)備中可編程性的重要性

可編程三相交流電源重要性和優(yōu)勢(shì)

可編程單相交流電源的重要性及優(yōu)勢(shì)

可編程電源如何編程

用TMAG5328電阻器和電壓可編程霍爾效應(yīng)開關(guān)實(shí)現(xiàn)可編程性和診斷

高速ADC的可編程特性的重要性

高速ADC的可編程特性的重要性

評(píng)論