1 緒論

計(jì)數(shù)器是數(shù)字邏輯系統(tǒng)中的基本部件, 它是數(shù)字系統(tǒng)中用得最多的時(shí)序邏輯電路,其主要功能就是用計(jì)數(shù)器的不同狀態(tài)來記憶輸入脈沖的個(gè)數(shù)。除此以外還具有定時(shí)、分頻、運(yùn)算等邏輯功能。 計(jì)數(shù)器不僅能用于對(duì)時(shí)鐘脈沖的計(jì)數(shù), 還可使用于定時(shí)、分頻、產(chǎn)生節(jié)拍脈沖以及進(jìn)行數(shù)字運(yùn)算等。只要是稍微復(fù)雜一些的

數(shù)字系統(tǒng), 幾乎沒有不包含計(jì)數(shù)器的。通常把滿足N=2n的計(jì)數(shù)器稱為二進(jìn)制規(guī)則計(jì)數(shù)器, 有些數(shù)字定時(shí)、分頻系統(tǒng)中,常需要N≠2n 的任意進(jìn)制計(jì)數(shù)器。

當(dāng)我們在設(shè)計(jì)任意進(jìn)制計(jì)數(shù)器 (即計(jì)數(shù)模不是 2及10)時(shí), 一般采用現(xiàn)有的中規(guī)模集成電路( Medium Scale Integration, MSI)芯片, 通過適當(dāng)?shù)姆答佭B接加以實(shí)現(xiàn)。而市場上現(xiàn)成的中規(guī)模集成電路芯片常見的只有十進(jìn)制計(jì)數(shù)器和十六進(jìn)制計(jì)數(shù)器,而在實(shí)際應(yīng)用中,如數(shù)字鐘電路中,卻需要二十四進(jìn)制和六十進(jìn)制計(jì)數(shù)器,因此要將現(xiàn)有計(jì)數(shù)器改造成任意進(jìn)制計(jì)數(shù)器。利用MSI芯片進(jìn)行適當(dāng)?shù)倪B接就可以構(gòu)成任意進(jìn)制計(jì)數(shù),所使用的方法主要有反饋置零法、反饋預(yù)置法和級(jí)聯(lián)法。

采用中規(guī)模集成計(jì)數(shù)器來設(shè)計(jì)任意進(jìn)制計(jì)數(shù)器,使設(shè)計(jì)和調(diào)試工作更趨于簡單, 并且具有體積小, 功耗低, 可靠性高等優(yōu)點(diǎn)。 本文主要闡述了用中規(guī)模集成計(jì)數(shù)器設(shè)計(jì)任意進(jìn)制同步加法計(jì)數(shù)器的設(shè)計(jì)思想, 并對(duì)設(shè)計(jì)方法和步驟作了討論。

2. MS I中規(guī)模計(jì)數(shù)器概述

2.1 MS I中規(guī)模計(jì)數(shù)器芯片種類

MS I中規(guī)模計(jì)數(shù)器芯片有非常多的種類。若按觸發(fā)時(shí)鐘的方式分類有: 同步計(jì)數(shù)器、異步計(jì)數(shù)器; 若按進(jìn)制的"模"分類有: 二進(jìn)制計(jì)數(shù)器、十進(jìn)制計(jì)數(shù)器; 若按計(jì)數(shù)的方式分類: 有加法計(jì)數(shù)器、減法計(jì)數(shù)器和可逆(加/減)計(jì)數(shù)器; 若按芯片的型號(hào)分類就更多了, 如:僅74系列的4位二進(jìn)制計(jì)數(shù)器芯片就有161、163、191、193、197等,十進(jìn)制計(jì)數(shù)器芯片有160、162等。

2.2 MSI中規(guī)模計(jì)數(shù)器工作原理

2.2.1.以十進(jìn)制同步計(jì)數(shù)器74LS160為例

74LS160的功能

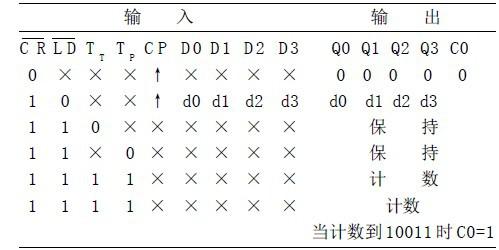

表1 74LS160功能表

根據(jù)功能表,74LSl60的功能說明如下:

(1)異步清零功能。當(dāng)CR=0 時(shí),不論其他輸入如何,輸出Q3Q2Q1Q0 為0000,表中"×"表示任意。

(2)同步并行置數(shù)功能。LD為預(yù)置數(shù)控制端,在CR=1 的條件下, LD=0 時(shí),在CP 上升沿的作用下,預(yù)置好的數(shù)據(jù)d3d2dld0被并行地送到輸出端,即此時(shí)的Q3Q2Q1Q0 為d3d2dld0 .

(3)保持功能。在CR=1 和LD=1 的前提下,只要TTTP=0,則計(jì)數(shù)器不工作,輸出保持原狀態(tài)不變。

(4)計(jì)數(shù)功能。正常計(jì)數(shù)時(shí),必須使CR=1,LD=1,TTTP=1,此時(shí)在CP 的上升沿的作用下,計(jì)

數(shù)器對(duì)C P 的個(gè)數(shù)進(jìn)行加法計(jì)數(shù)。當(dāng)計(jì)數(shù)到輸出Q3Q2Q1Q0 為1001 時(shí),C0=1,C0=1 的維持時(shí)間是從Q3Q2QlQ0 為1001 時(shí)起到QaQ2Q1Q0 狀態(tài)變化時(shí)止。

2.2.2以四位二進(jìn)制計(jì)數(shù)器為例

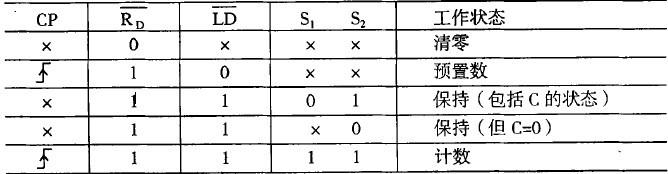

74LS161功能

表2 74LS161功能表

從功能表( 一) 可以看到,74LS161處于計(jì)數(shù)狀態(tài)時(shí),引出端RD,L D , S : , S : 都應(yīng)為" 1 " ( 接高電平) . 如果取其中一片T 4 1 6 1 作為低位計(jì)數(shù)器〔記作(1 ) 〕, 對(duì)該片計(jì)數(shù)器來講,每來一個(gè)C P 就計(jì)一次數(shù),它始終工作在計(jì)數(shù)狀態(tài)。

3. 設(shè)計(jì)方案

3. 1 采用反饋置零法來設(shè)計(jì)任意進(jìn)制計(jì)數(shù)器

對(duì)于 74LS160屬于異步置零輸入端的計(jì)數(shù)器,它是當(dāng)置零輸入端出現(xiàn)有效電平 (低電平 ) 后計(jì)數(shù)器立 即 被 置 零, 不 受 時(shí) 鐘 信 號(hào) 的 控 制。 而 對(duì) 于74LS162 / 74LS163 屬于同步置零輸入端的計(jì)數(shù) 器。它是當(dāng)置零輸入端出現(xiàn)有效電平 (低電平 ) 后計(jì)數(shù)器并不會(huì)立即被置零, 必須等下一個(gè)時(shí)鐘信號(hào)到達(dá)后, 才能將計(jì)數(shù)器置零。兩者用時(shí)必須加以區(qū)分。

3. 1. 1 采用并行法來設(shè)計(jì) 24 進(jìn)制計(jì)數(shù)器

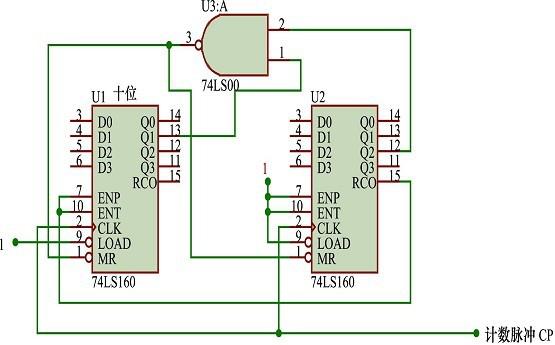

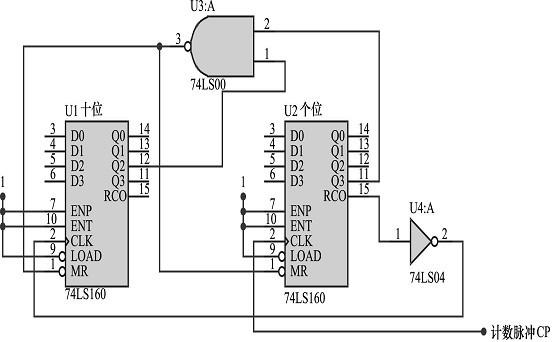

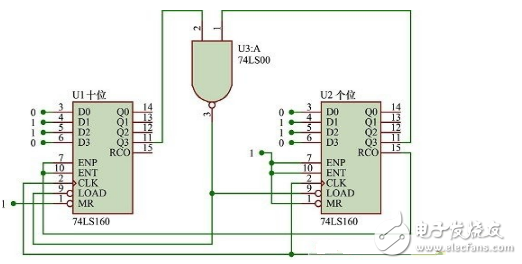

用 74LS160并行置零法設(shè)計(jì) 24進(jìn)制計(jì)數(shù)器的電路圖如圖 1所示。此電路的工作原理: 先假設(shè)兩芯片的置零輸入端為 1, 則個(gè)位芯片由于計(jì)數(shù)控制端 ENP = ENT = 1, 故該芯片始終處于計(jì)數(shù)狀態(tài); 而十位芯片的 ENP、ENT連接的是個(gè)位芯片的進(jìn)位控制端 RCO, 只有當(dāng)個(gè)位芯片的計(jì)數(shù)狀態(tài) Q 3Q 2 Q1 Q0為 1001時(shí), RCO 才為 1.十位芯片才能計(jì)數(shù)。如果沒有反饋置零 (即 MR 端恒接高電平 )則電路是一個(gè) 100進(jìn)制計(jì)數(shù)器。現(xiàn)在電路中加上了反饋, 當(dāng)計(jì)數(shù)狀態(tài) ( 00100100) 8421BCD碼 = ( 24) 10時(shí), 與非門輸出為零。由于 74LS160 屬于異步置零, 且復(fù)位控制端 MR低電平有效, 所以計(jì)數(shù)器立即置零。由于電路中的狀態(tài) ( 24 ) 10轉(zhuǎn)瞬即逝, 顯示不出。故電路的有效狀態(tài)從 ( 00) 10到 ( 23) 10共 24個(gè), 故此電路為24進(jìn)制計(jì)數(shù)器。

圖1 用74LS160并行置零法設(shè)計(jì)24進(jìn)制計(jì)數(shù)器

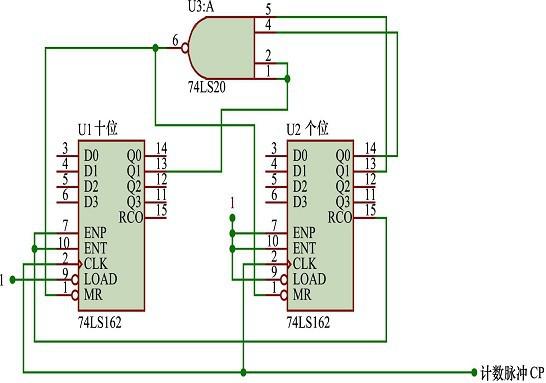

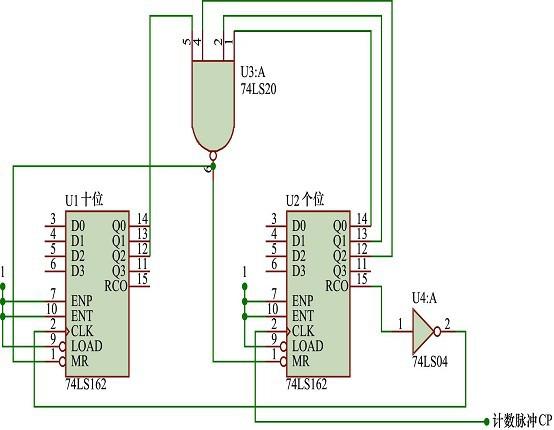

另外如果采用同步置零 74LS162計(jì)數(shù)器來設(shè)計(jì)24進(jìn)制計(jì)數(shù)器, 那么反饋代碼必須是 ( 23) 10相應(yīng)的8421BCD 碼為 00100011.由此可見反饋信號(hào)應(yīng)取自十位芯片的 Q1 及個(gè)位芯片的 Q1 和 Q0, 相應(yīng)的與非門應(yīng)改成四輸入端與非門。用 74LS162并行置零法設(shè)計(jì) 24進(jìn)制計(jì)數(shù)器的電路圖如圖 2所示。

圖2 用74LS162并行置零法設(shè)計(jì)24進(jìn)制計(jì)數(shù)器

3. 1. 2 采用串行法來設(shè)計(jì) 48 進(jìn)制計(jì)數(shù)器

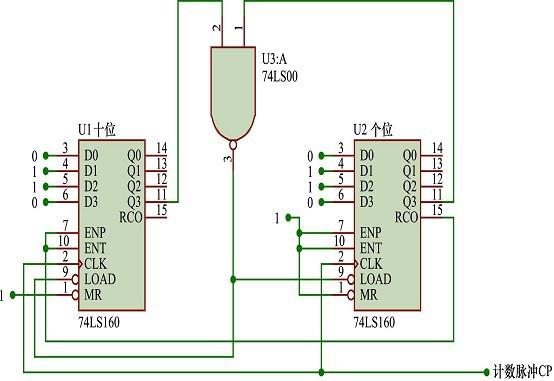

用 74LS160串行置零法設(shè)計(jì) 48進(jìn)制計(jì)數(shù)器的電路圖如圖 3所示。

圖3 用74LS160串行置零法設(shè)計(jì)48進(jìn)制計(jì)數(shù)器

此電路的工作原理: 先假設(shè)兩芯片的置零輸入端為 1, 則個(gè)位芯片由于計(jì)數(shù)控制端 ENP=ENT = 1, 故該芯片始終處于計(jì)數(shù)狀態(tài); 而十位芯片的 ENP = ENT = 1, 但十位芯片的計(jì)數(shù)脈沖CLK 是通過個(gè)位芯片的進(jìn)位控制端 RCO 取反來控制的。當(dāng)個(gè) 位芯 片的計(jì) 數(shù)狀 態(tài) Q 3Q 2Q 1Q 0為 1001時(shí), RCO 為 1.當(dāng)下一個(gè)計(jì)數(shù)脈沖到來時(shí) RCO 又為0.又由74LS160計(jì)數(shù)器的時(shí)鐘脈沖 CLK是上升沿有效, 與此同時(shí), 個(gè)位的RCO 由1到0相當(dāng)于一個(gè)下降沿, 通過非門74LS04 控制就得到一個(gè)上升沿, 同時(shí)十位芯片才能計(jì)數(shù)。如果沒有反饋置零(即MR 恒接高電平)則電路是一個(gè)100 進(jìn)制計(jì)數(shù)器。現(xiàn)電路中加上了反饋。當(dāng)計(jì)數(shù)狀態(tài)( 01001000) 8421BCD碼= (48)10時(shí), 與非門輸出為零。由于74LS160屬于異步置零, 且復(fù)位控制端低電平有效, 所以計(jì)數(shù)器立即置零。如果采用同步置零74LS162計(jì)數(shù)器來設(shè)計(jì)48進(jìn)制計(jì)數(shù)器, 那么反饋代碼必須是( 47)10相應(yīng)的8421BCD碼為01000111.由此可見反饋信號(hào)應(yīng)取自十位芯片的Q2 及個(gè)位芯片的Q2, Q1 及Q0, 相應(yīng)的與非門應(yīng)改成四輸入端與非門。74LS162串行置零法設(shè)計(jì)48進(jìn)制計(jì)數(shù)器的電路圖如圖4所示。

圖4 用74LS162串行置零法設(shè)計(jì)48進(jìn)制計(jì)數(shù)器

另外, 采用串行法設(shè)計(jì)時(shí), 十位芯片的計(jì)數(shù)脈沖CLK還可以通過個(gè)位芯片的最高位Q3 端通過非門取反來控制, 其他線路保持不變。只要對(duì)圖3或圖4稍加修改即可。

3.2 采用反饋置數(shù)法來設(shè)計(jì)任意進(jìn)制計(jì)數(shù)器

此方法適用于某些具有預(yù)置數(shù)的計(jì)數(shù)器, 它是采用預(yù)置數(shù)控制端LOAD來實(shí)現(xiàn)。對(duì)于74LS160屬于同步式預(yù)置數(shù)的計(jì)數(shù)器來說, 當(dāng)LOAD 出現(xiàn)有效電平低電平后待下一個(gè)時(shí)鐘脈沖信號(hào)到來后計(jì)數(shù)器輸出端的狀態(tài)Q3Q2Q1Q0 = D3D2D1D0.使其跳過某些狀態(tài)來設(shè)計(jì)任意進(jìn)制計(jì)數(shù)器。下面就以74LS160為例, 用并行置數(shù)法設(shè)計(jì)23 進(jìn)制計(jì)數(shù)器,其中預(yù)置數(shù)端D3D2D1D0可以置零, 也可以置十以內(nèi)的任意四位二進(jìn)制數(shù)。那么此電路在其置數(shù)時(shí)十位和個(gè)位的D3D2D1D0 置入( 01100110 )8421BCD 碼= ( 66) 10, 而反饋代碼十位和個(gè)位為( 10001000)8421BCD 碼= ( 88) 10, 相當(dāng)于十進(jìn)制數(shù)的88.由此分析可得到計(jì)數(shù)器的模為( 88- 66) + 1= 23, 故計(jì)數(shù)器為23進(jìn)制計(jì)數(shù)器, 其設(shè)計(jì)電路圖如圖5所示。由此可以得到置數(shù)法的設(shè)計(jì)要點(diǎn)為:反饋代碼轉(zhuǎn)換成的十進(jìn)制數(shù) - 預(yù)置數(shù)端的代碼轉(zhuǎn)換成的十進(jìn)制數(shù) + 1 = 所設(shè)計(jì)的計(jì)數(shù)器的模。同樣我們也可以仿照前面的設(shè)計(jì)用串行置數(shù)法設(shè)計(jì)任意進(jìn)制計(jì)數(shù)器。

圖5用74LS160并行置數(shù)法設(shè)計(jì)23進(jìn)制計(jì)數(shù)器

4 設(shè)計(jì)步驟

由于反饋置數(shù)法不太常用, 且難于理解,下面我們就以反饋置零法為例, 通過以上分析和經(jīng)驗(yàn)總結(jié),可以得出任意N 進(jìn)制計(jì)數(shù)器的設(shè)計(jì)方法及步驟。

根據(jù)計(jì)數(shù)模N 來確定所需要計(jì)數(shù)器芯片的個(gè)數(shù)n.n= INT ( logm (N - 1) ) + 1, INT 表示取整。m: 當(dāng)芯片為十進(jìn)制計(jì)數(shù)器時(shí)m 取10, 當(dāng)芯片為四位二進(jìn)制計(jì)數(shù)器時(shí)m 取16.

( 2)當(dāng)n個(gè)計(jì)數(shù)器芯片連接成模為m 的計(jì)數(shù)器

( 3)選用并行法或串行法將n 個(gè)計(jì)數(shù)器連接起來。

( 4)確定反饋置零代碼。如果計(jì)數(shù)器芯片采用異步置零反饋代碼為(N ) 10, 若是采用同步置零, 則反饋代碼為(N ?? 1) 10.

( 5)反饋置零代碼形式的轉(zhuǎn)換。如果芯片為十進(jìn)制制計(jì)數(shù)器, 將反饋代碼轉(zhuǎn)換成8421BCD 碼的形式。若是四位二進(jìn)制計(jì)數(shù)器, 則將反饋代碼轉(zhuǎn)換成二進(jìn)制數(shù)。

( 6)將轉(zhuǎn)換結(jié)果與計(jì)數(shù)器的狀態(tài)輸出端進(jìn)行比較,讓與1對(duì)應(yīng)的引腳作用到與非門(反饋置零端低電平有效)或者與門(反饋置零端高電平有效)的輸入端, 然后將與非門或者與門的輸出, 連接到計(jì)數(shù)器芯片的反饋置零端即可。

-

芯片

+關(guān)注

關(guān)注

455文章

50816瀏覽量

423674 -

集成電路

+關(guān)注

關(guān)注

5388文章

11547瀏覽量

361835 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2256瀏覽量

94575

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

N進(jìn)制計(jì)數(shù)器的實(shí)現(xiàn)

60進(jìn)制計(jì)數(shù)器

100進(jìn)制計(jì)數(shù)器

64進(jìn)制計(jì)數(shù)器

74LS161異步置零法構(gòu)成任意進(jìn)制計(jì)數(shù)器的Multisim仿真

基于MSI的N進(jìn)制計(jì)數(shù)器設(shè)計(jì)方法

采用歸零法的N進(jìn)制計(jì)數(shù)器原理

基于Multisim的計(jì)數(shù)器設(shè)計(jì)仿真

二五十進(jìn)制計(jì)數(shù)器

集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

基于Proteus的任意進(jìn)制計(jì)數(shù)器設(shè)計(jì)與仿真

24進(jìn)制計(jì)數(shù)器的設(shè)計(jì)

基于74LS192的任意進(jìn)制計(jì)數(shù)器的設(shè)計(jì)

基于74LS160的N進(jìn)制計(jì)數(shù)器仿真設(shè)計(jì)

任意進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案匯總(七款模擬電路設(shè)計(jì)原理詳解)

采用中規(guī)模集成計(jì)數(shù)器進(jìn)行任意進(jìn)制計(jì)數(shù)器設(shè)計(jì)的解決方案

采用中規(guī)模集成計(jì)數(shù)器進(jìn)行任意進(jìn)制計(jì)數(shù)器設(shè)計(jì)的解決方案

評(píng)論