游戲控制臺設計者必須在實現系統的多功能、可靠性和低成本之間尋找平衡。市場壓力經常迫使最初的控制臺價格低于可盈利的水平。不過,要在商業上獲得成功,游戲控制臺就必須能夠提供多種功能,如高清晰度圖像、網絡連接、運動傳感控制器以及基于IP的視頻內容,并且所有這些都要在用戶能承受的價格內。

為保持低成本特性,通常采用基于平臺的方法來設計游戲控制臺。目標是盡可能地使每個控制臺相似,同時還能滿足特殊區域的要求。單個平臺設計通常是不現實的,經濟效益上也不可行,但FPGA所提供的硬件靈活性使得游戲系統能夠很容易地針對不同區域、模型、組件和升級版進行重新設計。

一個典型的游戲控制臺包括CPU、圖形處理器、存儲器件、通信單元、I/O和用戶接口。游戲控制臺的核心通常是幾個大規模ASIC或ASSP。例如,iSuppli的報告指出,Sony PS3就包含一個7個核定制基于cell的CPU(ASIC)、一個NVIDIA圖形芯片組(ASSP)、XDR存儲器和一個flexIO處理器接口。

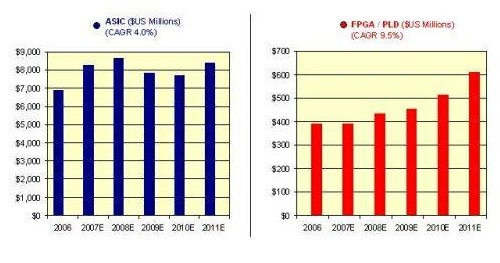

由于FPGA在許多應用中取代了ASIC,或許現在是時候將它用于下一代游戲控制臺設計中了。FPGA和PLD相對較低的成本正在推動其在消費電子產品中的使用,尤其是在LCD和等離子電視中。根據Gartner Group的報告(如圖1所示),在未來的4年中,用于消費電子產品的PLD和FPGA器件的全球市場年均復合增長率(CAGR)預計將達9.5%,超過了年均復合增長率為4.0%的ASIC器件。

圖1:用于消費電子設備的ASIC和FPGA的年收益變化。

基于平臺的游戲控制臺設計考慮因素

FPGA可以幫助系統設計者盡可能地節約成本并提供最大的靈活性,這是由基于平臺方法通過提供以下設計方針來實現的。

需求和模型可隨著區域而變化:針對多個標準和格式提供可編程支持能加快產品上市時間;低成本和可靠的設計:集成全部的系統I/O接口、控制邏輯和調試功能,以支持連接至HDD和內部存儲器的ASIC/ASSP芯片組的橋接功能,定制的用戶接口邏輯可降低在新產品中的風險;在最終測試期間和現場的安全編程能夠實現對多種標準的支持、協處理算法的增量升級以及易于對新功能進行測試。

在選擇面向平臺的可編程器件時,通常需考慮三種電路要求:面向協處理功能的嵌入式DSP的功能和性能、查找表(LUT)以及RAM塊(EBR),這種協處理功能利用并行方法,針對具體應用以最優成本對功能和性能進行裁剪。低電壓差分信號(LVDS)和串行解串器(SERDES)可支持高速芯片至芯片接口,如HyperTransport、PCI Express或串行RapidIO。能夠安全地保護知識產權。

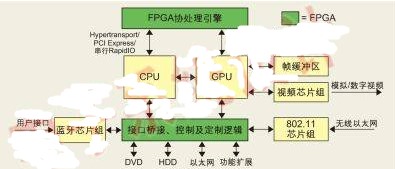

圖2顯示了一個滿足這些要求的FPGA解決方案。FPGA被連接到主CPU、圖像處理芯片、用戶接口和諸如無線以太網的其它關鍵ASSP。FPGA模塊執行協處理功能和硬件加速,并具有實現未來功能所必需的定制邏輯,這些功能是針對用戶接口或控制臺的其它部分。

圖2:可重構FPGA能支持多個I/O標準、高速接口以及針對硬件加速的協處理算法。

DSP協處理和硬件加速

盡管低成本FPGA通常工作在小于300MHz的系統時鐘頻率下,但通過并行地執行串行功能仍然可實現很高的DSP吞吐量(63,000MMAC)。例如,某個應用要求具有100MS/s采樣率的32抽頭FIR濾波器,那么需要帶有4個乘法器的通用DSP處理器以800MHz計算乘累加。具有32個乘法器的FPGA能夠在100MHz實現相同的濾波器。

與乘法器一樣,能夠靈活地利用FPGA的并行特性有益于存儲器訪問。片上分布式存儲器可用來構建小容量高性能臨時存儲器,而片上嵌入式存儲塊可用來構建大容量高性能存儲器。DDR DRAM等片外存儲器則可以提供大容量、高性能存儲器。

高速的芯片至芯片互連

FPGA通過高速的芯片至芯片互連技術與GPU和CPU連接,這些技術包括HyperTransport、PCI Express或串行RapidIO。串行RapidIO和PCI Express是串行而非并行技術,即串行地發送數據,并通過LVDS以數據包的形式恢復數據,而不是一次恢復一位。從并行到串行接口的轉換系統可用較少的線路達到同樣的高速數據速率。

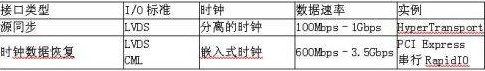

源同步和時鐘數據恢復接口

HyperTransport是一個源同步接口,而PCI Express和串行RapidIO采用時鐘數據恢復(CDR)技術,如下表所示。對于源同步接口而言,傳送方提供數據和差分時鐘,這樣就能較容易地在高達700Mbps的數據速率捕獲數據。

源同步和時鐘數據恢復接口。

當數據速率超過700Mbps時,數據通道之間的偏移成為數據有效窗的重要部分,特別是對寬數據通道而言。有些FPGA具有自動對齊功能,能夠針對源同步接口管理數據偏移,從而有助于它們達到超過800Mbps的LVDS數據速率(有些情況下高達2Gbps)。

對于CDR接口而言,并沒有提供額外的差分時鐘。取而代之的是時鐘包含在串行數據包中,必須從數據中恢復出來。因此,對于CDR來說時鐘偏移不是一個問題,這與源同步不同。利用SERDES高速串行地發送數據包,CDR接收器將對數據本身鎖定相位以取得時鐘。

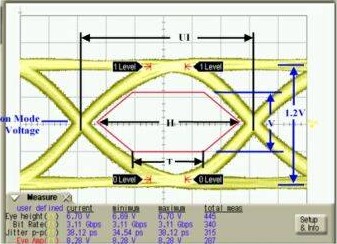

對于CDR而言,在高速情況下,SERDES抖動是主要問題。抖動是指期待數據傳輸的位置發生了變化,使得難以準確地接收到數據包。如圖3所示的眼圖,抖動使得圍繞眼睛的黃色帶的寬度發生變化,圖中用紅色表示。

圖3:CDR眼圖。

有些抖動是隨機的,但大部分抖動是確定性的,是由于其它信號以及靠近數據信號的半導體元件的開關操作引起,或者是由數據模式的特性、傳輸的不平衡上升及下降時間所引起。

安全配置和現場升級

游戲控制臺往往是電腦黑客攻擊的目標,因此FPGA不應該在配置期間給系統引入額外的弱點。對于基于SRAM的FPGA而言,配置數據通常來自外部的非易失存儲器。為保護該數據,一些FPGA加入了內置的128位AES加密引擎。面向AES的FPGA解密密鑰采用一次性可編程(OTP)熔絲編程。OTP密鑰是非易失的,且一旦密鑰被編程就不能修改,從而可阻止黑客用逆向工程探尋FPGA內部的功能。

此外,FPGA能幫助設計者橋接ASSP功能與圖像處理器或系統處理器。橋接的例子包括無線以太網(802.11)和用戶接口控制邏輯。定制的用戶接口邏輯有助于將游戲控制臺與競爭產品區分。用FPGA解決方案可以橋接或控制這兩種功能。

成功的策略

根據Booz Allen Hamilton公司今年三月發布的報告,Darden商業研究生院的Tim Laseter在2007年的一項研究認為,許多成功的公司并非是最先進入某個領域的先行者,而是能夠發現更多資源的后來者。例如,在Xbox 360和PS3之后,任天堂公司發布了不具有高清晰圖像的Wii游戲機。但是,采用Wii游戲控制臺的人數在不斷增加,因為這種游戲控制臺具有運動敏感的控制器和受家庭喜愛的游戲主題。

研究得出的結論是,在各種不同的技術中,多個小實驗能夠產生對如何創造價值的更多認識。我們不可能在當前就準確地知道客戶將來需要什么特性,或者硬件設計是否有小故障,或者主要的可靠性問題。由于“廣泛的硬件故障”,微軟公司花費了10億多美元來修補Xbox 360控制臺并將其納入保修范圍。

在游戲控制臺設計中采用FPGA可對硬件功能進行一些小實驗,從而有助于未來驗證游戲控制臺的設計。設計集成了一個可選的連接器用來連接至FPGA,并能夠實現未來的特性,或者FPGA可以通過以太網進行連接,從互聯網下載新的位流并實現新的功能。這些實驗可能還包括對人工智能、DVD倍線功能、附加的家長控制功能和新型用戶接口的測試。

市場要求所有設計游戲控制臺的公司能夠以盡可能低的制造實現更多的特性。如果設計出來的產品未加入重要的特性或靈活的接口,這些公司將會蒙受億萬美元的損失,更糟的是,產品可能根本沒有市場需求。

現在很有機會將一些小型的技術革新加入游戲控制臺系統,以支持未來將發生的變化,或者用硬件而不僅僅是固件來試驗新的特性。構筑一個在游戲控制臺中支持PCI Express、HyperTransport或串行RapidIO、LVDS和DSP的安全FPGA使得這些技術革新都有發展機會。

LatticeECP2M FPGA系列產品可支持許多這方面的要求,包括AES加密位流、PCI Express、LVDS、DSP以及可編程邏輯,以支持多種接口標準和定制功能。此外,由于支持多個DSP知識產權核和MATLAB Simulink,也使設計更加方便。

-

處理器

+關注

關注

68文章

19382瀏覽量

230481 -

FPGA

+關注

關注

1630文章

21769瀏覽量

604651 -

嵌入式

+關注

關注

5087文章

19153瀏覽量

306426

發布評論請先 登錄

相關推薦

基于PLD的視頻接口

采用PLD實現視頻接口設計

PLD在消費電子領域的應用

PLD在消費電子領域的挑戰

PLD在消費電子領域的應用

采用低成本FPGA實現高效的低功耗PCIe接口

dmx512控制臺是什么_dmx512控制臺按鍵說明

高效、低成本的 FPGA 器件:Spartan-7 FPGA!

SU RUBy控制臺如何使用?SU RUBy控制臺的一個應用實例說明

帶有ESP32 FutureBoard的DIY樂高視頻游戲無線控制臺

采用低成本的FPGA器件和PLD進行游戲控制臺的設計

采用低成本的FPGA器件和PLD進行游戲控制臺的設計

評論