如今CMOS技術讓一塊FPGA器件可以擁有多個I/O接口。同時,近幾年,低功耗已開始成為高速I/O接口的主流概念。降低功耗最有效的途徑就是降低電壓,而電壓降低就會導致I/O接口所允許的噪聲余量變小。因此,對FPGA用戶而言,量化芯片、封裝和PCB環境下的系統級同步開關噪聲(SSN)就顯得十分必要。

本文對SSN進行了系統性介紹,著重介紹由FPGA輸出緩沖導致的SSN。這種噪聲一般被稱作同步開關輸出噪聲(SSO),與輸入緩沖導致的SSN不同。本文介紹了系統級SSO的成因,并提出了一種分層的系統級SSO建模方法。同時,本文還講解了如何將SSO模型與頻域和時域測量相關聯,并給出了幾種減小SSO的PCB設計方法。

系統級SSO的形成機制

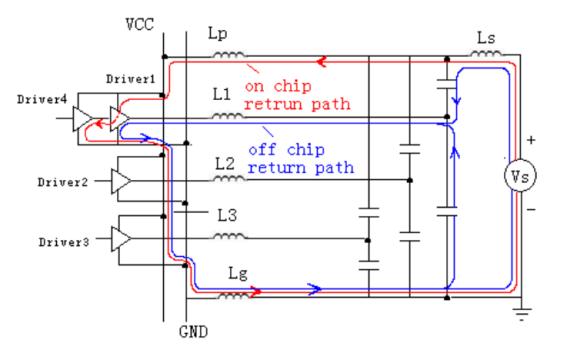

帶FPGA的PCB是一個復雜的系統,可將其分為包含有源電路的芯片部分、帶有嵌入式無源器件的支撐走線的封裝部分,和為FPGA與外部提供連接的電路板部分。在此類系統中,要想弄清芯片內部的噪聲特性很困難。因此,對與FPGA相連的PCB走線近端和遠端的SSO進行量化就顯得很有價值。造成SSO的主要有兩大因素:電源分配網(PDN)的阻抗和開關I/O之間的互感耦合。

從系統的角度來說,PDN中包含芯片級、封裝級和板卡級的組件,這些組件共同為CMOS電路供電。當一定數量的CMOS輸出驅動電路同時打開時,就會有很大電流瞬間涌入PDN的感性電路元件中,從而產生一個delta-I壓降。互連結構產生寄生電感,例如球柵陣列封裝上的電源焊球和PCB中的電源過孔。這種快速變化的電流還會在電源/接地平面對之間激勵起放射狀的電磁波,電磁波從PCB的平面邊緣反射回來,在電源/接地平面之間產生諧振,從而導致電壓波動。

造成SSO的另一個重要原因是互感耦合,尤其是在芯片封裝/PCB邊沿周圍產生的互感耦合。芯片BGA封裝上的焊球與PCB上的過孔都屬于緊耦合的多導線結構。每個I/O焊球及其相應的PCB過孔與離它最近的接地焊球和接地過孔構成一個閉合環路。當多個I/O口的狀態同時發生變化時,會有瞬態I/O電流流過這些信號環路。這種瞬態I/O電流又會產生時變的磁場,從而侵入鄰近的信號環路造成感應電壓噪聲。

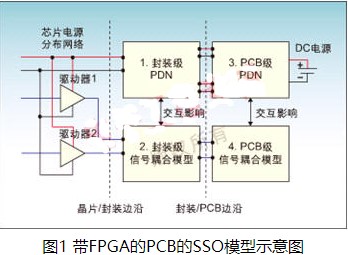

一個優秀的SSO模型應能體現SSO的基本形成機制。圖1給出的就是一個用于預測PCB中SSO的分層模型。在芯片一級,我們需要的是能在有限復雜度下提供電源線和信號線上精確電流分布的輸出緩沖模型。在封裝一級,為簡單起見,可利用建模工具分別得到PDN模型和信號耦合模型,但應謹慎考慮PDN和信號耦合模型之間的相互影響。這兩個模型起著橋梁的作用,連接了芯片封裝上凸點端的輸出緩沖模型和焊球端的PCB級模型。PCB的PDN模型通常包含電源/接地平面和其上的大容量/去耦電容,而PCB的信號耦合模型中則包含一個緊耦合的過孔陣列和不同信號層上的松耦合信號走線。這兩個PCB級模型的交互效應出現在PCB過孔陣列中,感性串擾正是從這里將噪聲帶入PDN模型,delta-I噪聲反過來會降低I/O信號質量。這種分層建模方法合理地保持了仿真精度,同時也提高了此類復雜系統的計算效率。

通過PCB設計減小SSO

下面針對裝有FPGA的印制電路板,介紹兩種基于SSO產生機制來減小SSO的基本設計方法。

1. 減小感性耦合的設計方法

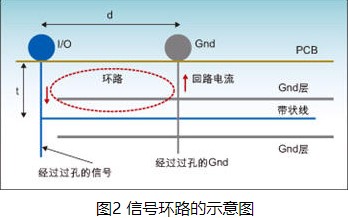

仿真結果顯示,芯片封裝/PCB接口上的感性耦合是導致SSO波形中高頻尖峰的元兇。一個大小為t×d的信號環路由一個信號過孔和距其最近的接地過孔組成,這個環路的大小就標志了感性耦合的強弱,如圖2所示。I/O干擾環路的面積越大,產生的磁場就越容易侵入鄰近的被干擾環路。被干擾I/O信號環路的面積越大,也就更容易受其它I/O環路干擾。因此,要降低串擾和參數t,設計中就應注意采用較薄的PCB,而且PCB上的關鍵I/O應從較淺的信號層引出。同時,設計師還可通過縮短I/O過孔與接地過孔之間的距離來減小串擾。在圖中所示的設計中,設計師專門將一對I/O焊盤連到了地平面和VCCIO平面,以減小干擾管腳和被干擾管腳相應的信號環路面積。

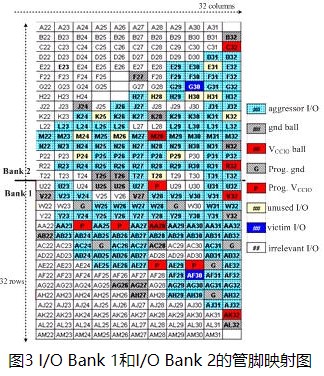

為評估本方法的有效性,我們對FPGA I/O Bank1 和Bank2進行了兩次測量,如圖3所示。這兩個Bank中的所有I/O口都配置為電流強度12mA的LVTTL 2.5-V接口,并通過50Ω帶狀線與10pF的電容端接。

在Bank1中,管腳AF30是被干擾管腳。在FPGA設計中,將W24、W29、AC25、AC32、AE31和AH31這6個管腳通過編程設置為邏輯“0”,它們通過過孔連接到PCB的接地平面。U28、AA24、AA26、AE28和AE30這5個管腳則通過編程設置為邏輯“1”,并連接到PCB的VCCIO平面。其它68個I/O口以10MHz頻率同時發生狀態變換,因而是產生干擾的管腳。為了進行比較,Bank2中沒有將W24、W29、AC25、AC32、AE31、AH31、U28、AA24、AA26、AE28和AE30這些 I/O通過編程設置為接地腳或VCCIO腳,只是將其空置,其它68個I/O仍然同時開關,如圖3所示。

實驗測試顯示Bank1中AF30上的地彈(ground bounce)已比Bank 2中的G30降低了17%,電壓下陷(power sag)也減小了13%。仿真結果也驗證了這一改善。由于可編程接地管腳的出現縮短了干擾環路和被干擾環路的距離d,因此SSO的減小是預料中的,如圖2所示。然而,由于芯片封裝中的信號環路面積無法減小,所以改善程度也有限。

2. 通過合理設計減小PDN阻抗

PCB上接口處VCCIO和接地管腳之間的阻抗對于一塊FPGA芯片的PDN性能評估是最重要的一個標準。通過采用有效的去耦策略并使用較薄的電源/接地平面對可以減小這一輸入阻抗。但最有效的方法還是縮短將VCCIO焊球連接至VCCIO平面的電源過孔的長度。而且,縮短電源過孔也會減小其與鄰近接地過孔構成的環路,從而使這一環路較不易受干擾I/O環路狀態變化的影響。因此,設計時應將VCCIO平面安排在離PCB頂層更近的位置。

本文小結

本文對裝有FPGA的PCB上的同步開關噪聲仿真進行了全面分析。分析結果表明,封裝和PCB接口上的串擾與封裝和PCB上的PDN阻抗分布是SSO的兩個重要成因。

相關模型可用于幫助PCB設計師減小SSO,實現更優秀的PCB設計。文中還介紹了幾種降低SSO的方法。其中,合理分配信號層并充分利用可編程的接地/電源管腳可幫助減小PCB級的感性串擾,將VCCIO安排在PCB疊層中較淺的位置也可降低PDN阻抗。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604301 -

CMOS

+關注

關注

58文章

5724瀏覽量

235700 -

pcb

+關注

關注

4322文章

23126瀏覽量

398584

發布評論請先 登錄

相關推薦

開關電源傳導EMI預測方法研究

三相步進電動機建模及常用控制方法仿真

【EMC家園】開關電源傳導EMI預測方法研究

【EMC家園】開關電源傳導EMI預測方法研究

如何應對FPGA同步開關的SSN噪聲的挑戰

永磁同步電機直接轉矩控制系統中的MATLAB/Simulink建模方法

基于MDA的訓練仿真建模研究

同步開關噪聲產生的原因和影響

同步開關輸出噪聲建模方法及仿真研究

同步開關輸出噪聲建模方法及仿真研究

評論