現(xiàn)在有各種各樣的硅資源供您選擇,供應(yīng)商們正在調(diào)整其標(biāo)準(zhǔn)組件產(chǎn)品系列以滿足您的需求。

要點(diǎn)

● 標(biāo)準(zhǔn)單元ASIC 和FPGA 的權(quán)衡為結(jié)構(gòu)化ASIc新興公司打開了一個(gè)有爭議的市場缺口。

● 結(jié)構(gòu)化ASIC不只是改名換姓的門陣列,而是反映了目前的市場現(xiàn)實(shí)和硅片功能。

● 平臺(tái)ASIC是具有硬件定制功能的ASSP。

● RapidWorx大大降低了ASIC開發(fā)工具套件的成本,而Quartus II則使其達(dá)到了FPGA工具的水平——這是一件極好的事情。

● 競爭者對手的反應(yīng)是各種各樣的,其它的解決辦法即將出現(xiàn)。

看來您已認(rèn)定,采取購買并組裝現(xiàn)成的專用標(biāo)準(zhǔn)產(chǎn)品(ASSP),如嵌入式控制器、外設(shè)芯片等,然后再編寫您自己的軟件這種做法將不能使您設(shè)計(jì)的產(chǎn)品與您競爭對手的產(chǎn)品有足夠大的差別。因此,您會(huì)決定選擇芯片級設(shè)計(jì)。兩大硅平臺(tái)競爭對手及其各自的折衷方案已經(jīng)在各種工業(yè)論壇上引起廣泛的爭論。不過如果您剛涉足這場爭論,則很有必要了解下述有關(guān)爭論的概要。

多種制造FPGA的深亞微米工藝,如Xilinx公司最新Spartan-3系列產(chǎn)品采用的90納米工藝(參考文獻(xiàn)1),使每塊芯片上的門電路數(shù)量變得越來越大。如果您的設(shè)計(jì)使用FPGA的嵌入式存儲(chǔ)器陣列和擴(kuò)散式模擬及數(shù)字功能模塊,如DLL、PLL、乘法累加器、串行器/解串行器(SERDES)電路、高速I/O緩存器,在某些情況下甚至是CPU芯核和相關(guān)外設(shè),則FPGA的可用功能是極大的。您可以根據(jù)設(shè)計(jì)的需求來訂購少量或大量的FPGA,而且不必向供應(yīng)商支付NRE(非經(jīng)常工程)費(fèi)用。供應(yīng)商已經(jīng)安排并調(diào)試芯片的邏輯平面、存儲(chǔ)器平面、信號路由平面以及電源平面。

一旦您的設(shè)計(jì)完成,你便可在幾秒鐘到幾分鐘之內(nèi)擁有一塊實(shí)用的芯片。一般說來,你用來開發(fā)和調(diào)試設(shè)計(jì)的工具要比用于開發(fā)調(diào)試專用集成電路(ASIC)的工具便宜許多。(然而,如果Hier設(shè)計(jì)公司售價(jià)為25,000 美元的PlanAhead代表未來工業(yè)趨勢的話,F(xiàn)PGA工具組的平均價(jià)格將會(huì)上漲)。但是,無論FPGA變得多么密集,F(xiàn)PGA的面積效率仍然要比用可比工藝制造的標(biāo)準(zhǔn)單元ASIC低一到兩個(gè)數(shù)量級。FPGA,尤其是基于占用大量硅面積的、每個(gè)單元六個(gè)晶體管的靜態(tài)存儲(chǔ)器(SRAM)的查尋表(LUT)和配置元件技術(shù)的FPGA,其功耗要比對等的ASIC大得多。

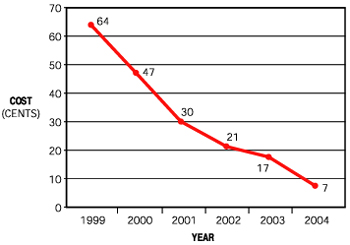

遺憾的是,ASIC的很多優(yōu)點(diǎn)也帶來相應(yīng)的缺點(diǎn)。由于芯片按照摩爾定律光刻線路發(fā)展,NRE費(fèi)用、最少訂購數(shù)量以及每席開發(fā)工具套件的費(fèi)用都將猛漲(圖1)。ASIC的最少訂購數(shù)量反映了供應(yīng)商能夠在生產(chǎn)線上生產(chǎn)并仍可獲利的最少的用戶專用晶圓。芯片的裸芯片越大,所需的最小訂購數(shù)量就越小,而且您還會(huì)看到為什么改用線寬更小的光刻工藝和更大的晶圓后能大大提高這種最小批量需求。

電源電壓下降、信號耦合以及深亞微米布線效應(yīng)會(huì)造成種種故障,查找、修理這些故障所需的時(shí)間加上布線主導(dǎo)的時(shí)序收斂,都會(huì)延長標(biāo)準(zhǔn)單元ASIC的開發(fā)周期。甚至在當(dāng)您認(rèn)為您的設(shè)計(jì)業(yè)已完成時(shí),您還不得不等待設(shè)計(jì)通過漫長的生產(chǎn)、測試以及包裝等工序,然后才能取回芯片,而且,如果您設(shè)計(jì)的芯片不工作或者不再能夠滿足快速變化的市場需求,那就會(huì)招致成本和時(shí)間延遲的成倍增加。用標(biāo)準(zhǔn)單元ASIC進(jìn)行設(shè)計(jì)需要大量的時(shí)間、勞力和金錢;正如最近的分析報(bào)告所指出的那樣,造成市場向FPGA急速轉(zhuǎn)移的就是這三個(gè)因素。但是對于門電路數(shù)量或芯片批量達(dá)到幾十萬的設(shè)計(jì)或者對于性能要求或功率要求非常嚴(yán)格的設(shè)計(jì)來說,標(biāo)準(zhǔn)單元的ASIC仍然是唯一的技術(shù)選擇。

傳統(tǒng)的解決方案

對此怎么做出選擇呢?為了回答這一問題,首先比較一下FPGA和ASIC的基本硅標(biāo)準(zhǔn)組件,即兩者的邏輯單元和布線結(jié)構(gòu)。FPGA的邏輯單元都是粗粒的,從各種各樣的多路復(fù)用器和分立邏輯門到一個(gè)或多個(gè)LUT,全都是粗顆粒的,并且通常由觸發(fā)器作補(bǔ)充。Actel公司的 ProASIC FPGA目前能提供業(yè)界最細(xì)顆粒的邏輯模塊。FPGA供應(yīng)商設(shè)計(jì)其器件的內(nèi)部邏輯模塊布線,從而將所需的可由用戶配置的布線層數(shù)減到最少;這樣,設(shè)計(jì)編譯和布局布線軟件面臨的主要挑戰(zhàn)就是高效利用邏輯模塊問題。您得到的芯片具有大多未編程的邏輯模塊間布線資源;對于基于非熔斷閃存芯片來說,這些資源您可以在系統(tǒng)加電之前配置,而對于基于SRAM的FPGA來說,則可在系統(tǒng)啟動(dòng)之時(shí)及之后配置(如果您的設(shè)計(jì)支持的話)。

標(biāo)準(zhǔn)單元ASIC邏輯模塊與FPGA的邏輯模塊相比顆粒要細(xì)得多。顧名思義,“標(biāo)準(zhǔn)單元”都采用按相同標(biāo)準(zhǔn)尺寸來制造晶體管和芯片上的其他結(jié)構(gòu)。(這種同質(zhì)性就是標(biāo)準(zhǔn)單元與完全定制芯片的主要差異)。然而,正如“專用”這一名稱所示,ASIC的布局以及器件的時(shí)鐘、電源和信號布線都是您實(shí)現(xiàn)方法專用的。因此,芯片的金屬化層和多晶硅層對每個(gè)用戶來說全都是獨(dú)一無二的,而且供應(yīng)商在將器件運(yùn)送給您之前預(yù)先對布線進(jìn)行了配置,使您在系統(tǒng)生產(chǎn)和隨后的運(yùn)作過程中不必具備硬件定制能力。在這種情況下,開發(fā)軟件不是主要側(cè)重于使每個(gè)邏輯模塊內(nèi)的設(shè)計(jì)實(shí)現(xiàn)方法高效率,就像更粗顆粒的FPGA一樣,但卻要側(cè)重于邏輯模塊互連的高效率。

從歷史看,另一種ASIC——門陣列——介于FPGA和標(biāo)準(zhǔn)單元ASIC這兩個(gè)極端之間。與FPGA類似,門陣列的布線網(wǎng)格是通用而又預(yù)定的。和標(biāo)準(zhǔn)單元一樣,這種布線網(wǎng)格專門設(shè)計(jì)配置在芯片生產(chǎn)的最后幾個(gè)階段進(jìn)行,而且供應(yīng)商有時(shí)將細(xì)顆粒的邏輯單元陣列稱為“雙輸入‘與非’門之海”。近幾年,曾經(jīng)被廣泛應(yīng)用的門陣列已經(jīng)逐漸消失,隨著FPGA逐步蠶食其領(lǐng)地,門陣列已經(jīng)越來越明顯地成為萬事通而無專長現(xiàn)象的犧牲品。就從訂購到使用的周轉(zhuǎn)時(shí)間而言,門陣列比標(biāo)準(zhǔn)單元快得還不夠,無法奪取大量FPGA的業(yè)務(wù)。而且,門陣列的性能和硅片面積效率太差,使它們無法取代很多標(biāo)準(zhǔn)單元。

掩膜可編程FPGA

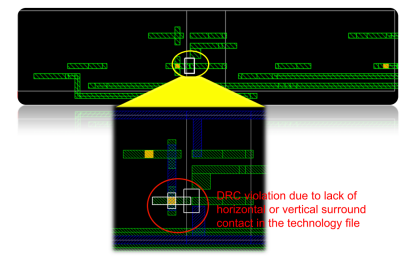

受到業(yè)務(wù)流失警示的一些ASIC供應(yīng)商把FPGA竅門寶典的一些經(jīng)驗(yàn)和門陣列的以往教訓(xùn)結(jié)合在一起,提出了結(jié)構(gòu)化的ASIC。有人也將這種方法稱為模塊化陣列或結(jié)構(gòu)化陣列。供應(yīng)商和供應(yīng)商之間存在大量的技術(shù)差別,但是簡單的講,結(jié)構(gòu)化的ASIC是具有類似FPGA粗顆粒邏輯單元的門電路陣列派生產(chǎn)品,因而需要更少的可由用戶配置的金屬層和通孔層(圖2)。供應(yīng)商需要處理時(shí)鐘樹和電源平面布線。一個(gè)類比能夠有助于對結(jié)構(gòu)化ASIC設(shè)計(jì)的理解:在軟件編程的早期,微處理器的速度非常慢,存儲(chǔ)器非常昂貴,因此低級而又高效的匯編語言和更為低級的機(jī)器代碼占據(jù)了支配地位。

隨著CPU運(yùn)行速度的加快和存儲(chǔ)器價(jià)格的下降,更高級的軟件語言取代了以前的匯編語言和機(jī)器代碼。它們對資源的使用效率較低,但是好在現(xiàn)在效率并不顯得那么重要。然而,面市時(shí)間卻日益重要,而高級語言在這一方面出類拔萃。由于同樣的原因,VHDL和Verilog日益成為將電路變成芯片的硬件工程師們選擇的設(shè)計(jì)輸入方法,而更耗時(shí)的原理圖輸入技術(shù)則放棄使用。結(jié)構(gòu)化ASIC供應(yīng)商大膽地假定,將會(huì)出現(xiàn)一個(gè)硅平臺(tái)市場,盡管硅平臺(tái)可能比標(biāo)準(zhǔn)單元的效率低,面市時(shí)間比FPGA長,但是也沒有那些競爭產(chǎn)品的所有缺點(diǎn)(圖3)。因?yàn)樾酒难谀ぁ啽愕卣f,常常也是最昂貴的掩膜——所占的百分比很大,這對于多個(gè)用戶設(shè)計(jì)來說是很普通的,所以每個(gè)用戶的NRE費(fèi)用就會(huì)減少,周轉(zhuǎn)時(shí)間就會(huì)縮短,而且你還能更容易地使由此產(chǎn)生的平臺(tái)適應(yīng)不斷演進(jìn)的工業(yè)標(biāo)準(zhǔn),和適應(yīng)硬件修改最少的派生芯片(圖4)。

現(xiàn)在正在吹捧結(jié)構(gòu)化ASIC器件的公司中有AMI Semiconductor公司, Chip Express公司, Faraday Technology公司, Fujitsu公司, Lightspeed Semiconductor公司, NEC公司, 和ViASIC公司。在這些公司中,目前只有AMI公司目前沒有把自己定位為范圍廣泛的硅片供應(yīng)商;該公司正在堅(jiān)持向FPGA轉(zhuǎn)換的有利地位,但是使用的是一種結(jié)構(gòu)化ASIC基礎(chǔ),而不是過去的門陣列平臺(tái)。相反,Lightspeed Semiconductor公司曾短暫擴(kuò)入Xilinx FPGA降價(jià)市場,現(xiàn)已退出這一市場,將精力集中在傳統(tǒng)的ASIC上(參考文獻(xiàn)2)。Chip Express 公司的結(jié)構(gòu)化ASIC采用各種備選方案中最細(xì)顆粒的邏輯模塊;該公司估計(jì)其器件的每個(gè)邏輯模塊將包含三到四個(gè)門電路,視具體設(shè)計(jì)而定。其他供應(yīng)商的大多數(shù)邏輯模塊能實(shí)現(xiàn)20~40個(gè)門的設(shè)計(jì)(圖5)。

結(jié)構(gòu)化ASIC供應(yīng)商用各種混合的工藝制造芯。這種多樣性反映了每個(gè)廠商都試圖想在潛在的用戶大蛋糕上占有自己單獨(dú)的一份。供應(yīng)商及其代工工廠攤消了他們用來開發(fā)后沿的易于理解的成品率高的0.18-微米、 0.25-微米、和0.35-微米工藝的生產(chǎn)設(shè)施與設(shè)備費(fèi)用。您能用這些工藝實(shí)現(xiàn)的設(shè)計(jì)規(guī)模有個(gè)上限,但是相關(guān)的供應(yīng)商指出:分析報(bào)告顯示具有1百萬門以下的ASIc設(shè)計(jì)占很大的百分比,同時(shí)有數(shù)據(jù)顯示用戶使用的ASIC設(shè)計(jì),其中不足100000件批量的占50%(圖6)。

在工藝技術(shù)另一端的是Fujitsu、NEC等公司。Fujitsu 公司現(xiàn)已將0.11微米結(jié)構(gòu)化ASIC工藝投產(chǎn),0.09微米工藝也將于2004年投產(chǎn)。NEC公司預(yù)示他們的90納米工藝也將在2004年下半年投產(chǎn)。使工藝適合于設(shè)計(jì)是一種微妙的平衡行為,也涉及到了解設(shè)計(jì)的I/O緩沖器數(shù)量;供應(yīng)商和用戶希望發(fā)生的最后的事情是裸芯片在對最小尺寸起限制作用的I/O環(huán)路

內(nèi)包含未被使用、從而浪費(fèi)硅資源的區(qū)域。復(fù)雜封裝的成本逐漸增加也使得封裝內(nèi)各種硅片的成本成比例地不相關(guān)。

結(jié)構(gòu)化ASIC供應(yīng)商聲稱從設(shè)計(jì)完成到第一個(gè)樣品供使用的標(biāo)準(zhǔn)單元周轉(zhuǎn)時(shí)間要從幾個(gè)月縮短到幾個(gè)星期。這種延遲不是從布局布線網(wǎng)表到FPGA提供的硅資源的幾秒鐘到幾分鐘的遲后時(shí)間,但是ASIC擁護(hù)者聲稱這種比較在某種意義上是蘋果和桔子的比較。他們指出,隨著FPGA和其內(nèi)部的設(shè)計(jì)越來越復(fù)雜,工程師們?yōu)榱藢?shí)現(xiàn)區(qū)域(這個(gè)區(qū)域適合嗎)和時(shí)間(它運(yùn)行的足夠快嗎)收斂所花費(fèi)的時(shí)間是指數(shù)增加的。工程師們認(rèn)為,由于ASIC具有比FPGA更快的設(shè)計(jì)基礎(chǔ),所以花在模擬和重新設(shè)計(jì)方面的時(shí)間比較少,用結(jié)構(gòu)化ASIC進(jìn)行開發(fā)的總周期可能也因此而比用FPGA的更短。

硬件可定制的ASSP

結(jié)構(gòu)化ASIC供應(yīng)商用來使性能要求嚴(yán)格的電路的速度最大并實(shí)現(xiàn)諸如降低功耗、減小面積等其它功效的方法,就是將這些電路變成芯片的擴(kuò)展部分而不是一般邏輯結(jié)構(gòu)。例如Fujitsu公司聲稱其擴(kuò)展的嵌入式觸發(fā)器要比代替的方法能降低功耗50%,提高門使用率1.5~2倍。

Lightspeed公司將AutoTest 和AutoBIST快速測試電路嵌入模塊化陣列ASIC中,以確保100%的固定型故障檢測范圍,并發(fā)現(xiàn)深亞微米造成的延遲故障。本文提到的每一個(gè)結(jié)構(gòu)化ASIC供應(yīng)商都提供擴(kuò)展的嵌入式SRAM模塊,而且如果您的設(shè)計(jì)需要的話,其中有些SRAM模塊集成有時(shí)鐘電路、高速串行和并行I/O緩沖器和其它具有豐富模擬功能的、對面積、電源和性能有嚴(yán)格要求的結(jié)構(gòu)。

LSI logic公司利用其RapidChip將擴(kuò)展電路發(fā)揮到極致。該公司將RapidChip 稱為平臺(tái)ASIC,而且目前用0.11微米和0.18 微米兩種工藝來制造。LSI Logic公司希望RapidChip將能使他們重溫幾年前的美好時(shí)光,當(dāng)時(shí)他們的用戶平均每天有三個(gè)設(shè)計(jì)啟動(dòng);而現(xiàn)在他們大約每三天才有一個(gè)新設(shè)計(jì)。LSI Logic公司開始進(jìn)行占裸芯片面積很大百分比的、按應(yīng)用定制的擴(kuò)展式模擬、數(shù)字和存儲(chǔ)資源的混合設(shè)計(jì),如SRAM陣列、微處理器芯核、PLL和基于SERDES的接口(如10G以太網(wǎng)、光纖通道和SATA)。它用一個(gè)或多個(gè)片上門陣列ASIC陣列來補(bǔ)充這些專用功能,并將合成的芯片稱為RapidSlice。LSI Logic公司的Extreme系列在其所包含廣泛擴(kuò)展的芯核產(chǎn)品中都是按應(yīng)用定制的,In Tegrator產(chǎn)品在性質(zhì)上更加通用。

RapidChip部件反映細(xì)顆粒門陣列邏輯單元,因而支持用戶定制的金屬化層多達(dá)5層。從一般的RapidSlice到用戶專用的RapidChip的過渡涉及到門陣列分區(qū)的數(shù)量,這分區(qū)可能具有用戶設(shè)計(jì)的專有電路和獲準(zhǔn)從LSI Logic公司的CoreWare 資源庫中獲得的芯核。這些芯核可能是“軟件”、“硬件”或“固件”知識(shí)產(chǎn)權(quán)(IP)。軟件IP具有最好的設(shè)計(jì)布局靈活性但性能最低;具有預(yù)定義的布局布線的硬件IP處于速度對適應(yīng)性關(guān)系的另一端。該公司將其稱為Hard RapidReady IP ,以便與預(yù)制的擴(kuò)展RapidReady芯核區(qū)別開來。固件IP是預(yù)先布局的但是沒有布線,因此是介于上面兩種IP之間的中間產(chǎn)品。LSI Logic公司聲稱存在一條能直截了當(dāng)降低成本的途徑,使RapidChip轉(zhuǎn)化為可與IP兼容的標(biāo)準(zhǔn)單元ASIC。

RapidChip 程序不僅側(cè)重于實(shí)現(xiàn)方程的硅部分,而且也側(cè)重于開發(fā)工具開支,這在這個(gè)遲遲不去的高技術(shù)不景氣時(shí)代尤其是個(gè)問題。

RapidChip 資源庫將并入你已經(jīng)擁有的各種昂貴的標(biāo)準(zhǔn)單元ASIC工具套件中;其他ASIC供應(yīng)商的資源庫也是以這種方式工作著。LSI Logic公司已經(jīng)與Synplicity公司和Tera Systems公司合作,共同提供RapidWorx——一種集成的全面工具,它具有物理合成、RTL規(guī)則檢查以及規(guī)劃三種功能;RapidWorx的專利許可費(fèi)是每六個(gè)月20000美元。Synplicity公司是在FPGA市場上長期占有統(tǒng)治地位的設(shè)計(jì)軟件公司,非常熟悉用較低的每個(gè)設(shè)計(jì)席利潤率換取數(shù)量大得多的設(shè)計(jì)席的業(yè)務(wù)方法。至少可以說,歷來ASIC為重點(diǎn)的EDA供應(yīng)商會(huì)發(fā)現(xiàn)這種轉(zhuǎn)換非常困難,而且Synplicity也希望這第二次在ASIC市場上的努力將比它的Synplify ASIC 產(chǎn)品更加成功。Synplicity公司還宣布了與Chip Express、Lightspeed和NEC三公司建立合作關(guān)系。

有些競爭對手發(fā)表了嘲笑結(jié)構(gòu)化ASIC供應(yīng)商的種種說法。例如Actel公司和QuickLogic公司指出他們的非熔斷的FPGA具有比相同粗顆粒的結(jié)構(gòu)化ASIC更好的設(shè)計(jì)與生產(chǎn)靈活性,而且在密度和性能上也可與之相媲美。Actel公司銷售副總裁Barry Marsh還認(rèn)為文化因素在結(jié)構(gòu)化ASIC推銷過程中起了作用:亞洲的供應(yīng)商有時(shí)由于“關(guān)系”因素而被迫接收他們通常不接受的小批量業(yè)務(wù),而結(jié)構(gòu)化ASIC為他們提供了一種在可能有利可圖的程度上支持這種業(yè)務(wù)的手段。

沒有結(jié)構(gòu)化ASIC程序——或者至少?zèng)]有公開宣布程序——的ASIC供應(yīng)商,如IBM公司和 Toshiba公司,也想當(dāng)然地貶低新公司達(dá)到其崇高目標(biāo)的能力。Toshiba公司認(rèn)為,因?yàn)镕PGA和標(biāo)準(zhǔn)單元ASIC在業(yè)界都已得到確認(rèn),它們在成本、性能、功耗、面市時(shí)間或者其它方面的差距太小,任何一家結(jié)構(gòu)化ASIC供應(yīng)商都不能長久生存下來。Toshiba公司報(bào)道說,最近幾年它在知識(shí)產(chǎn)權(quán)(IP)庫、驗(yàn)證方法學(xué)和后端工具方面進(jìn)行了大量的投資;其目標(biāo)是將從市場需求到生產(chǎn)出產(chǎn)品的延續(xù)時(shí)間縮短到六個(gè)月以內(nèi)。

Toshiba公司聲稱,是布線錯(cuò)誤而不是邏輯錯(cuò)誤,才有必要對大多數(shù)設(shè)計(jì)進(jìn)行返工,因此混合的標(biāo)準(zhǔn)單元加門陣列平臺(tái),例如該公司提供的這種平臺(tái),將會(huì)滿足大多數(shù)用戶的需求。Xilinx公司也對結(jié)構(gòu)化ASIC廠商的前景持類似的悲觀態(tài)度;Xilinx公司認(rèn)為,只有它的FPGA改用先進(jìn)的光刻工藝來制造,它才會(huì)否認(rèn)基于后沿?cái)U(kuò)展工藝的結(jié)構(gòu)化ASIC在其他方面具有的任何優(yōu)點(diǎn)(圖7)。

來自各方的響應(yīng)

Xilinx公司也指出,令人可疑的是,LSI Logic 公司的RapidChip在概念上與自己的Virtex-II Pro平臺(tái)相似,包含有擴(kuò)散的PowerPC芯核及其他電路,并用RapidChip的掩膜可編程分區(qū)取代了更加靈活的基于SRAM的可編程邏輯。其它包含有FPGA的混合芯片實(shí)例有:Altera 公司的Excalibur系列,Atmel公司的現(xiàn)場可編程系統(tǒng)級IC(FPSLIC)芯片,QuickLogic公司的嵌入式標(biāo)準(zhǔn)產(chǎn)品和Triscend公司的片上可配置系統(tǒng))。IBM公司與Xilinx公司合作,使IBM公司可以充分利用其合作伙伴的FPGA技術(shù);盡管IBM公司還沒有宣布任何確實(shí)的合作關(guān)系的成果,但業(yè)界權(quán)威人士認(rèn)為該公司計(jì)劃不久將宣布其有能力在自己的標(biāo)準(zhǔn)化單元ASIC內(nèi)嵌入FPGA芯核。

Altera對ASIC的態(tài)度一直在演變,值得觀察和分析。直到幾個(gè)月前,Altera公司還像自己的主要競爭對手Xilinx公司那樣對ASIC技術(shù)進(jìn)行大肆批評。然而,Altera公司最近卻推出了HardCopy FPGA轉(zhuǎn)換平臺(tái)的最新版本,目標(biāo)是最新一代Stratix FPGA。成套的每年2000美元的Quartus II 第三版設(shè)計(jì)軟件現(xiàn)在支持能直接將你的設(shè)計(jì)編譯到HardCopy的引人注目的功能,因此避開了中間的Stratix步驟,事實(shí)上將Altera公司變成了結(jié)構(gòu)化ASIC供應(yīng)商。Altera公司銷售副總裁Tim Colleran說,公司有可能考慮每年5000件以上的HardCopy業(yè)務(wù)量,并將根據(jù)用戶和器件對這一數(shù)字進(jìn)行修改。NRE費(fèi)用大約為200000美元,并且同樣適用于不同的用戶、器件和批量。Altera公司能將HardCopy樣品在大約8個(gè)星期后交付給您,并在大約18個(gè)星期后將產(chǎn)品單元交付給您。直到您收到HardCopy產(chǎn)品芯片為止,您才可以使用FPGA;但要記住:在某些情況下HardCopy器件具有的片上存儲(chǔ)器比對等的FPGA器件還少,而且它們重用的成本優(yōu)化封裝的選擇余地更小。

Altera公司估計(jì),HardCopy芯片平均要比對等的FPGA芯片運(yùn)行速度快50%,體積小70%,功耗低40%。Altera 公司產(chǎn)品功能的這種擴(kuò)展可能反映出Altera公司新任首席執(zhí)行官John Daane的影響。他曾是LSI Logic公司的副總裁。Xilinx公司不再考慮HardCopy的重要性,推出了自己的能降低成本的工具,即EasyPath。不過,不久前,Xilinx公司擁有類似HardCopy的產(chǎn)品系列,即HardWire系列,該公司也沒有泄漏他們實(shí)驗(yàn)室中正在醞釀的研究計(jì)劃。EasyPath的硅基礎(chǔ)同樣是您通常買的FPGA,但是Xilinx公司采用通常能夠?qū)е赂叱善仿实挠脩魧S昧鞒虒ζ溥M(jìn)行測試。修改后的流程不再測試芯片上沒有使用的潛在不工作的區(qū)域,并放寬通常非常嚴(yán)格的交流和直流規(guī)范,適合你設(shè)計(jì)的需要。

作為生產(chǎn)FPGA的新公司,Leopard Logic公司也認(rèn)為ASIC加可編程邏輯混合電路是有前途的。該公司是為了向ASIC供應(yīng)商和硅片代工廠及其終端客戶推廣嵌入式FPGA技術(shù)而在幾年前創(chuàng)辦的。就像Actel 公司、Adaptive Silicon公司以及其他在Leopard Logic公司之前走嵌入式FPGA 道路的公司一樣,Leopard Logic公司在廣告宣傳上幾乎沒有取得成功;該公司官員們將主要責(zé)任歸咎于規(guī)避風(fēng)險(xiǎn)的風(fēng)險(xiǎn)投資者,他們停止對知識(shí)產(chǎn)權(quán)(IP)公司投資時(shí),就造成資金短缺。Leopard Logic公司正在重新將自己改造成為無工廠的ASIC供應(yīng)商,利用自己的嵌入式FPGA技術(shù),于2003年年底將首批產(chǎn)品投放市場。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605428 -

芯片

+關(guān)注

關(guān)注

456文章

51157瀏覽量

426552 -

asic

+關(guān)注

關(guān)注

34文章

1206瀏覽量

120682

發(fā)布評論請先 登錄

相關(guān)推薦

ASIC和FPGA的優(yōu)勢與劣勢

ASIC和FPGA有什么區(qū)別

基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程

可編程邏輯器件和ASIC,兩者有什么不同區(qū)別?

請問arm提供的標(biāo)準(zhǔn)單元庫中的track是什么意思

GaAs ASIC 標(biāo)準(zhǔn)單元庫建庫技術(shù)研究

MOS電流模邏輯標(biāo)準(zhǔn)單元設(shè)計(jì)方法

基于標(biāo)準(zhǔn)單元ASIC設(shè)計(jì)

標(biāo)準(zhǔn)單元ASIC和FPGA的權(quán)衡及結(jié)構(gòu)化ASIC

ASIC設(shè)計(jì)轉(zhuǎn)FPGA時(shí)的注意事項(xiàng)

面向近亞閾值的標(biāo)準(zhǔn)單元庫設(shè)計(jì)方法

采用標(biāo)準(zhǔn)單元庫和陣列方法的混合模擬/數(shù)字ASIC設(shè)計(jì)

如何使用Synopsys PAC進(jìn)行標(biāo)準(zhǔn)單元布局的改進(jìn)

標(biāo)準(zhǔn)單元ASIC和FPGA的權(quán)衡解決方案及應(yīng)用優(yōu)勢

標(biāo)準(zhǔn)單元ASIC和FPGA的權(quán)衡解決方案及應(yīng)用優(yōu)勢

評論