1、 概 述

隨著大規(guī)模集成電路水平的發(fā)展,以數(shù)字信號處理器(Digital Signal Process,DSP)為基礎(chǔ)的實(shí)時數(shù)字信號處理技術(shù)正在迅速發(fā)展,現(xiàn)已廣泛應(yīng)用于圖像處理技術(shù)、語聲處理、智能化儀表、生物醫(yī)學(xué)與工程、通信、自動控制等領(lǐng)域。由Analog Device公司生產(chǎn)的ADSP是應(yīng)用非常廣泛的一類DSP,其典型產(chǎn)品有定點(diǎn)的ADSP2181和浮點(diǎn)的ADSP21060。在許多實(shí)際系統(tǒng)中,需要采用多片DSP級聯(lián)的方式進(jìn)行處理。因此,ADSP2181經(jīng)常經(jīng)級聯(lián)后用在實(shí)際系統(tǒng)中,我們設(shè)計(jì)了基于ISA總線的通用多DSP目標(biāo)系統(tǒng),這種系統(tǒng)可以用于早期研發(fā)及各種算法的硬件平臺,他對縮短實(shí)際系統(tǒng)開發(fā)周期、項(xiàng)目預(yù)研等都有重要意義和應(yīng)用價值。

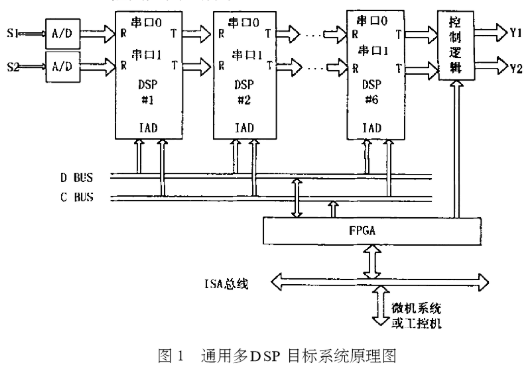

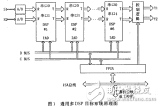

2、 通用多DSP 目標(biāo)系統(tǒng)的構(gòu)成

通用多DSP 目標(biāo)系統(tǒng)的構(gòu)成由6片ADSP2181、2片A/D變換器以及實(shí)現(xiàn)邏輯功能的FPGA組成,其原理框圖如圖1所示。

(1)處理系統(tǒng)

整個處理系統(tǒng)由6片DSP構(gòu)成,他完成對2路模擬信號的采集和數(shù)據(jù)處理。本系統(tǒng)采用的是Analog Device公司較為典型的定點(diǎn)DSP系列ADSP2181,相鄰2片DSP之間的串口數(shù)據(jù)的發(fā)送與接收、幀同步信號的發(fā)送與接收分別對應(yīng)相連,數(shù)據(jù)的傳輸采用自動緩沖的方式。

(2)系統(tǒng)輸入

系統(tǒng)輸入的模擬信號由2路精度為12b的串行A/D變換器完成,采樣率最高達(dá)400kS/s,輸入模擬量為單極性(0~2.5V)信號。模擬信號經(jīng)A/D變換器后以串行方式送入第1片DSP。

(3)時序控制

系統(tǒng)時序控制由FPGA(Field Programmable Gate Array,現(xiàn)場可編程門陣列)實(shí)現(xiàn),系統(tǒng)采用Altera公司的FPGA芯片EPFl0K10,其實(shí)現(xiàn)的主要功能有:

①產(chǎn)生ISA總線對各片DSP訪問的地址譯碼與控制;

②產(chǎn)生通過IDMA端口訪問DSP所需的控制信號IAL,IWR, IRD和IS;

③產(chǎn)生各個DSP的復(fù)位信號;

④產(chǎn)生滿足A/D轉(zhuǎn)換器時序要求的控制信號CLK(串口時鐘)和CONV(轉(zhuǎn)換控制)。

另外,F(xiàn)PGA還完成了DSP與ISA總線之間數(shù)據(jù)傳輸所需的控制時序,有效地保證了數(shù)據(jù)傳輸?shù)目煽啃浴?/p>

3 、通用多DSP目標(biāo)系統(tǒng)的硬件設(shè)計(jì)

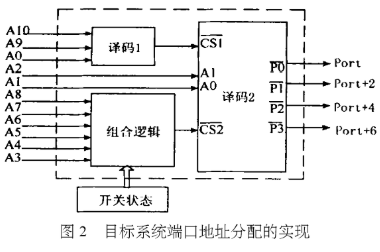

(1)目標(biāo)系統(tǒng)的地址分配與實(shí)現(xiàn)

每塊DSP目標(biāo)板只占用一組端口地址,每組地址共4個:數(shù)據(jù)端口、地址端口、復(fù)位端口和控制端口。組起始地址通過4b跳線開關(guān)加以選擇,設(shè)開關(guān)值為n,則板卡起始地址為360-4×n(記作port),其他3個端口地址分別為port+2,port+4,port+6。在FPGA中采用如圖2所示的邏輯,實(shí)現(xiàn)了目標(biāo)系統(tǒng)板端口地址的動態(tài)分配。

數(shù)據(jù)端口port 用于實(shí)現(xiàn)對DSP內(nèi)部存儲器的讀寫操作,完成DSP與上位機(jī)之間的數(shù)據(jù)傳輸。

地址端口port+2 用于提供對DSP進(jìn)行讀寫操作時DSP內(nèi)部程序存儲區(qū)(PM)或數(shù)據(jù)存儲區(qū)(DM)的起始地址。

復(fù)位端口port+4 用于對DSP進(jìn)行復(fù)位操作,實(shí)現(xiàn)對DSP的軟復(fù)位。

控制端口port+6 用于選擇要操作的DSP。

(2)控制信號的形成

目標(biāo)板上6片DSP占用同一端口地址,系統(tǒng)工作時,可以對任意DSP的任一數(shù)據(jù)區(qū)進(jìn)行讀寫操作。對DSP的片選信號是通過對控制端口的操作來實(shí)現(xiàn)的。當(dāng)A2A1=11時,對應(yīng)于DSP的控制端口,這時數(shù)據(jù)線的低3位(DATA[2..0])用于指定6個DSP中的一個。

4 、下載軟件設(shè)計(jì)

ADSP2181片內(nèi)集成了一個可以訪問其內(nèi)部存儲器的16 b IDMA端口,主機(jī)通過此端口可以訪問ADSP2181片內(nèi)的程序存儲器和數(shù)據(jù)存儲器的任一單元,實(shí)現(xiàn)對DSP下載文件、傳輸數(shù)據(jù)等操作,這一過程是通過上位機(jī)對DSP的IDMA端口的操作來完成的。本文設(shè)計(jì)了基于VB的通用多DSP目標(biāo)系統(tǒng)的下載軟件,通過上位機(jī)對目標(biāo)系統(tǒng)進(jìn)行各種操作。

(1)端口選擇 選擇一組端口地址,他應(yīng)與目標(biāo)板的端口地址相一致;

(2)處理器選擇 選擇所要進(jìn)行讀寫操作及下載的處理器號(1#~6#);

(3)下載文件選擇 選擇要加載到指定DSP的程序;

(4)下載 執(zhí)行下載操作,并自動檢查加載是否成功,若不成功,則重新加載;

(5)讀處理器選擇 調(diào)用讀處理器模塊,讀選定處理器的指定單元的內(nèi)容;

(6)寫處理器選擇 調(diào)用寫處理器模塊,在所選的處理器的指定單元寫入數(shù)據(jù)。

5 、結(jié) 語

通用多DSP目標(biāo)系統(tǒng),在地址分配上充分考慮到了ISA總線和定點(diǎn)ADSP2181的特點(diǎn),采用地址的動態(tài)分配技術(shù),有效地節(jié)省了系統(tǒng)的資源。下載軟件可以對1片或多片DSP進(jìn)行文件下載、讀、寫等操作,極大地增強(qiáng)了系統(tǒng)的通用性與靈活性。該系統(tǒng)可用于各種算法的硬件平臺和早期研發(fā),具有較高的應(yīng)用價值。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

554文章

8058瀏覽量

349696 -

FPGA

+關(guān)注

關(guān)注

1630文章

21781瀏覽量

604913 -

芯片

+關(guān)注

關(guān)注

456文章

51069瀏覽量

425835

發(fā)布評論請先 登錄

相關(guān)推薦

基于定點(diǎn)DSP系列ADSP2181芯片實(shí)現(xiàn)通用多DSP目標(biāo)系統(tǒng)的設(shè)計(jì)

[討論]FPGA培訓(xùn)—基于FPGA的DSP系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

怎么設(shè)計(jì)一款基于ISA總線的通用多DSP目標(biāo)系統(tǒng)?

如何采用ADSP2181實(shí)現(xiàn)語音信號的識別?

基于ADSP-2181的語音識別模塊

在ADSP2181上實(shí)現(xiàn)Rake接收機(jī)路徑搜索

ADSP實(shí)驗(yàn)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

基于ADSP2181的語音識別模塊

基于ADSP_TS201S的多DSP并行系統(tǒng)設(shè)計(jì)

ISA總線的通用多DSP目標(biāo)系統(tǒng)分析

ADSP2181實(shí)時語音處理DSP的方案

EE-82:使用ADSP-2181 DSP的IO空間IDMA引導(dǎo)另一個ADSP-2181

AN-400:選擇DSP處理器的考慮因素--為什么購買ADSP-2181?

EE-82:使用ADSP-2181 DSP的IO空間對另一個ADSP-2181進(jìn)行IDMA引導(dǎo)

基于ADSP2181芯片和FPGA器件實(shí)現(xiàn)通用多DSP目標(biāo)系統(tǒng)的設(shè)計(jì)

基于ADSP2181芯片和FPGA器件實(shí)現(xiàn)通用多DSP目標(biāo)系統(tǒng)的設(shè)計(jì)

評論