只有最初級的邏輯電路才使用單一的時(shí)鐘。大多數(shù)與數(shù)據(jù)傳輸相關(guān)的應(yīng)用都有與生俱來的挑戰(zhàn),即跨越多個(gè)時(shí)鐘域的數(shù)據(jù)移動,例如磁盤控制器、CDROM/DVD 控制器、調(diào)制解調(diào)器、網(wǎng)卡以及網(wǎng)絡(luò)處理器等。當(dāng)信號從一個(gè)時(shí)鐘域傳送到另一個(gè)時(shí)鐘域時(shí),出現(xiàn)在新時(shí)鐘域的信號是異步信號。

在現(xiàn)代 IC、ASIC 以及 FPGA 設(shè)計(jì)中,許多軟件程序可以幫助工程師建立幾百萬門的電路,但這些程序都無法解決信號同步問題。設(shè)計(jì)者需要了解可靠的設(shè)計(jì)技巧,以減少電路在跨時(shí)鐘域通信時(shí)的故障風(fēng)險(xiǎn)。

基礎(chǔ)

從事多時(shí)鐘設(shè)計(jì)的第一步是要理解信號穩(wěn)定性問題。當(dāng)一個(gè)信號跨越某個(gè)時(shí)鐘域時(shí),對新時(shí)鐘域的電路來說它就是一個(gè)異步信號。接收該信號的電路需要對其進(jìn)行同步。同步可以防止第一級存儲單元(觸發(fā)器)的亞穩(wěn)態(tài)在新的時(shí)鐘域里傳播蔓延。

亞穩(wěn)態(tài)是指觸發(fā)器無法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既無法預(yù)測該單元的輸出電平,也無法預(yù)測何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。在這個(gè)穩(wěn)定期間,觸發(fā)器輸出一些中間級電平,或者可能處于振蕩狀態(tài),并且這種無用的輸出電平可以沿信號通道上的各個(gè)觸發(fā)器級聯(lián)式傳播下去。

對任何一種觸發(fā)器,在時(shí)鐘觸發(fā)沿前后的一個(gè)小時(shí)間窗口內(nèi),輸入信號必須穩(wěn)定。這一時(shí)間窗口是多種因素的函數(shù),包括觸發(fā)器設(shè)計(jì)、實(shí)現(xiàn)技術(shù)、運(yùn)行環(huán)境以及無緩沖輸出上的負(fù)載等。輸入信號陡峭的邊沿可以將此窗口減至最小。隨著時(shí)鐘頻率的升高,會出現(xiàn)更多有問題的時(shí)間窗口,而隨著數(shù)據(jù)頻率的提升,這種窗口的命中概率則會增加。

FPGA 制造商和 IC 晶片廠用“MTBF”來標(biāo)識合格的觸發(fā)器,并且確定它們的特性。“MTBF”(平均無故障時(shí)間)用統(tǒng)計(jì)方法描述了一個(gè)觸發(fā)器的亞穩(wěn)態(tài)特性,即確定某個(gè)觸發(fā)器出現(xiàn)故障的概率。在計(jì)算 MTBF 時(shí),制造商部分基于輸入信號改變導(dǎo)致觸發(fā)器不穩(wěn)定期間的時(shí)間窗口長度。另外,MTBF 的計(jì)算還使用了輸入信號的頻率以及驅(qū)動觸發(fā)器的時(shí)鐘頻率。

在一個(gè) ASIC 或 FPGA 庫中,每種觸發(fā)器都有時(shí)序要求,以幫助你確定容易出問題的窗口。“建立時(shí)間”(Setup time)是指在時(shí)鐘沿到來之前,觸發(fā)器輸入信號必須保持穩(wěn)定的時(shí)間。“保持時(shí)間”(Hold time)則是指在時(shí)鐘沿之后,信號必須保持穩(wěn)定的時(shí)間。這些指標(biāo)通常比較保守,以應(yīng)對電源電壓、工作溫度、信號質(zhì)量以及制造工藝等各種可能的差異。如果一個(gè)設(shè)計(jì)滿足了這些時(shí)序要求,則觸發(fā)器出現(xiàn)錯誤的可能性可以忽略不計(jì)。

現(xiàn)代 IC 與 FPGA 設(shè)計(jì)中使用的綜合工具可以保證設(shè)計(jì)能滿足每個(gè)數(shù)字電路觸發(fā)器對建立與保持時(shí)間的要求。然而,異步信號卻給軟件提出了難題。對新的時(shí)鐘域來說,從其它時(shí)鐘域傳來的信號是異步的。大多數(shù)綜合工具在判定異步信號是否滿足觸發(fā)器時(shí)序要求時(shí)遇到了麻煩。因?yàn)樗鼈儾荒艽_定觸發(fā)器處于非穩(wěn)態(tài)的時(shí)間,所以它們也就不能確定從一個(gè)觸發(fā)器通過組合邏輯到達(dá)下一個(gè)觸發(fā)器的總延遲時(shí)間。所以,最好的辦法是使用一些電路來減輕異步信號的影響。

信號同步

信號同步的目的是防止新時(shí)鐘域中第一級觸發(fā)器的亞穩(wěn)態(tài)信號對下級邏輯造成影響。簡單的同步器由兩個(gè)觸發(fā)器串聯(lián)而成,中間沒有其它組合電路。這種設(shè)計(jì)可以保證后面的觸發(fā)器獲得前一個(gè)觸發(fā)器輸出時(shí),前一個(gè)觸發(fā)器已退出了亞穩(wěn)態(tài),并且輸出已穩(wěn)定。設(shè)計(jì)中要注意將兩個(gè)觸發(fā)器放得盡可能近,以確保兩者間有最小的時(shí)滯(clock skew)。

IC 制造廠提供同步單元,幫助完成信號同步工作。這些單元通常包括一個(gè)有非常高增益的觸發(fā)器,它比普通觸發(fā)器耗電更高,也比較大。這種觸發(fā)器降低了對輸入信號建立-保持時(shí)間的要求,并且當(dāng)輸入信號導(dǎo)致亞穩(wěn)態(tài)時(shí),它可以防止出現(xiàn)振蕩。另一種同步器單元包括兩個(gè)觸發(fā)器,省去了將兩個(gè)單獨(dú)觸發(fā)器靠近放置的工作,也防止設(shè)計(jì)人員誤在兩個(gè)觸發(fā)器間加入任何其它的組合邏輯。

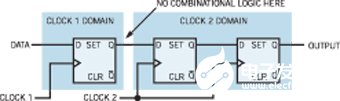

為了使同步工作能正常進(jìn)行,從某個(gè)時(shí)鐘域傳來的信號應(yīng)先通過原時(shí)鐘域上的一個(gè)觸發(fā)器,然后不經(jīng)過兩個(gè)時(shí)鐘域間的任何組合邏輯,直接進(jìn)入同步器的第一個(gè)觸發(fā)器中(圖 1)。這一要求非常重要,因?yàn)橥狡鞯牡谝患売|發(fā)器對組合邏輯所產(chǎn)生的毛刺非常敏感。如果一個(gè)足夠長的信號毛刺正好滿足建立-保持時(shí)間的要求,則同步器的第一級觸發(fā)器會將其放行,給新時(shí)鐘域的后續(xù)邏輯送出一個(gè)虛假的信號。

圖1,在一個(gè)全同步器電路中,從某個(gè)時(shí)鐘域傳來的信號應(yīng)先通過原時(shí)鐘域上的一個(gè)觸發(fā)器,然后不經(jīng)過原觸發(fā)器和同步器的第一個(gè)觸發(fā)器兩個(gè)時(shí)鐘域間的任何組合邏輯,直接進(jìn)入同步器的第一個(gè)觸發(fā)器中。

一個(gè)經(jīng)同步后的信號在兩個(gè)時(shí)鐘沿以后就成為新時(shí)鐘域中的有效信號。信號的延遲是新時(shí)鐘域中的一到兩個(gè)時(shí)鐘周期。一種粗略的估算方法是同步器電路在新時(shí)鐘域中造成兩個(gè)時(shí)鐘周期的延遲,設(shè)計(jì)者需要考慮同步延遲將對跨時(shí)鐘域的信號時(shí)序造成的影響。

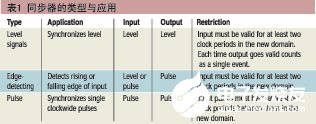

同步器有許多種設(shè)計(jì)方法,因?yàn)橐环N同步器不能滿足所有應(yīng)用的

需求。同步器的類型基本上有三種:電平、邊沿檢測和脈沖(表 1)。雖然還存在著其它類型的同步器,但這三種類型的同步器可以解決設(shè)計(jì)者遇到的多數(shù)應(yīng)用問題。在電平同步器中,跨時(shí)鐘域的信號在新時(shí)鐘域中要保持高電平或低電平兩個(gè)時(shí)鐘周期以上。這種電路的要求是,在再次成為有效信號前,信號需要先變成無效狀態(tài)。每一次信號有效時(shí),接收邏輯都會把它看作一個(gè)單個(gè)事件,而不管信號的有效狀態(tài)保持了多久。這種電路是所有同步器電路的核心。

表 1

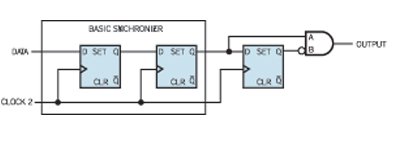

邊沿檢測同步器在電平同步器的輸出端增加了一個(gè)觸發(fā)器(圖 2)。新增觸發(fā)器的輸出經(jīng)反相后和電平同步器的輸出進(jìn)行與操作。這一電路會檢測同步器輸入的上升沿,產(chǎn)生一個(gè)與時(shí)鐘周期等寬、高電平有效的脈沖。如果將與門的兩個(gè)輸入端交換使用,就可以構(gòu)成一個(gè)檢測輸入信號下降沿的同步器。將與門改為與非門可以構(gòu)建一個(gè)產(chǎn)生低電平有效脈沖的電路。

圖2,邊沿檢測同步器在電平同步器的輸出端增加了一個(gè)觸發(fā)器。

當(dāng)一個(gè)脈沖進(jìn)入更快的時(shí)鐘域中時(shí),邊沿檢測同步器可以工作得很好。這一電路會產(chǎn)生一個(gè)脈沖,用來指示輸入信號上升或下降沿。這種同步器有一個(gè)限制,即輸入脈沖的寬度必須大于同步時(shí)鐘周期與第一個(gè)同步觸發(fā)器所需保

持時(shí)間之和。最保險(xiǎn)的脈沖寬度是同步器時(shí)鐘周期的兩倍。如果輸入是一個(gè)單時(shí)鐘寬度脈沖進(jìn)入一個(gè)較慢的時(shí)鐘域,則這種同步器沒有作用,在這種情況下,就要采用脈沖同步器。

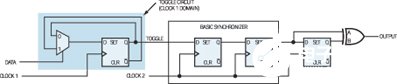

脈沖同步器的輸入信號是一個(gè)單時(shí)鐘寬度脈沖,它觸發(fā)原時(shí)鐘域中的一個(gè)翻轉(zhuǎn)電路(圖 3)。每當(dāng)翻轉(zhuǎn)電路接收到一個(gè)脈沖時(shí),它就會在高、低電平間進(jìn)行轉(zhuǎn)換,然后通過電平同步器到達(dá)異或門的一個(gè)輸入端,而另一個(gè)信號經(jīng)一個(gè)時(shí)鐘周期的延遲進(jìn)入異或門的另一端,翻轉(zhuǎn)電路每轉(zhuǎn)換一次狀態(tài),這個(gè)同步器的輸出端就產(chǎn)生一個(gè)單時(shí)鐘寬度的脈沖。

圖3,脈沖同步器的輸入信號是一個(gè)單時(shí)鐘寬度脈沖,它觸發(fā)原時(shí)鐘域中的一個(gè)翻轉(zhuǎn)電路

脈沖同步器的基本功能是從某個(gè)時(shí)鐘域取出一個(gè)單時(shí)鐘寬度脈沖,然后在新的時(shí)鐘域中建立另一個(gè)單時(shí)鐘寬度的脈沖。脈沖同步器也有一個(gè)限制,即輸入脈沖之間的最小間隔必須等于兩個(gè)同步器時(shí)鐘周期。如果輸入脈沖相互過近,則新時(shí)鐘域中的輸出脈沖也緊密相鄰,結(jié)果是輸出脈沖寬度比一個(gè)時(shí)鐘周期寬。當(dāng)輸入脈沖時(shí)鐘周期大于兩個(gè)同步器時(shí)鐘周期時(shí),這個(gè)問題更加嚴(yán)重。這種情況下,如果輸入脈沖相鄰太近,則同步器就不能檢測到每個(gè)脈沖。

握手與 FIFO

在許多應(yīng)用中,跨時(shí)鐘域傳送的不只是簡單的信號,數(shù)據(jù)總線、地址總線和控制總線都會同時(shí)跨域傳輸。工程師們用一些其它的手段來處理這些情況,如握手協(xié)議和 FIFO 等。

當(dāng)幾個(gè)電路不能預(yù)知相互的響應(yīng)時(shí)間時(shí),握手方法能讓數(shù)字電路間實(shí)現(xiàn)有效的通信。例如,仲裁總線結(jié)構(gòu)可以讓一個(gè)以上的電路請求使用單個(gè)的總線,用仲裁方法來決定哪個(gè)電路可以獲得總線的訪問權(quán),例如 PCI 或 AMBA(高級微控制器總線架構(gòu))。每個(gè)電路都發(fā)出一個(gè)請求信號,由仲裁邏輯決定誰是“贏家”。獲勝的電路會收到一個(gè)應(yīng)答,表示它可以訪問總線。該電路于是中斷請求,開始使用總線。

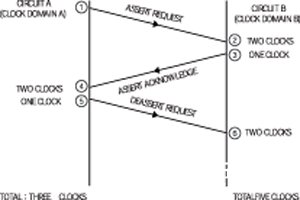

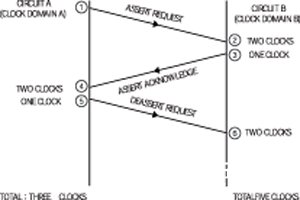

不同時(shí)鐘域電路使用的握手協(xié)議有兩種基本類型:全握手(Full-handshake)和部分握手(partial-handshake)。每種類型的握手都要用同步器,每種都各有自己的優(yōu)缺點(diǎn)。對全握手信號,雙方電路在聲明或中止各自的握手信號前都要等待對方的響應(yīng)(圖 4)。首先,電路 A 聲明它的請求信號,然后,電路 B 檢測到該請求信號有效后,聲明它的響應(yīng)信號。當(dāng)電路 A 檢測到響應(yīng)信號有效后,中止自己的請求信號。最后,當(dāng)電路 B 檢測到請求無效后,它中止自己的響應(yīng)信號。除非電路 A 檢測到無效的響應(yīng)信號,否則它不會再聲明新的請求信號。

圖4,對全握手信號,雙方電路在聲明或中止各自的握手信號前都要等待對方的響應(yīng)。

這種類型的握手使用了電平同步器。設(shè)計(jì)人員將這種技術(shù)用在如下情況:響應(yīng)電路(電路 B)需要告知請求電路(電路 A)它可以處理請求。這種握手方法要求請求電路延遲它的下一個(gè)請求,直到它檢測到響應(yīng)信號無效。可以用經(jīng)驗(yàn)估算法判斷這個(gè)協(xié)議的時(shí)序:信號跨越一個(gè)時(shí)鐘域要花兩個(gè)時(shí)鐘周期的時(shí)間,信號在跨越多個(gè)時(shí)鐘域前被電路寄存。全部的時(shí)間序列是:A 時(shí)鐘域中最多五個(gè)周期加上 B 時(shí)鐘域最多六個(gè)周期。全握手類型很強(qiáng)健,因?yàn)橥ㄟ^檢測請求與響應(yīng)信號,每個(gè)電路都清楚地知道對方的狀態(tài)。這種方式的不足之處是完成所有交互的整個(gè)過程要花費(fèi)很多時(shí)鐘周期。

另一種類型是部分握手,它可以縮短這些事件的過程。使用部分握手信號時(shí),通信雙方的電路都不等對方的響應(yīng)就中止各自的信號,并繼續(xù)執(zhí)行握手命令序列。部分握手類型比全握手類型在健壯性方面稍弱,因?yàn)槲帐中盘柌⒉恢甘靖髯噪娐返臓顟B(tài),每一電路都必須保存狀態(tài)信息(在全握手信號里這個(gè)信息被送出去)。但是,由于無需等待其它電路的響應(yīng),完整的事件序列花費(fèi)時(shí)間較少。

當(dāng)使用部

分握手信號方式時(shí),響應(yīng)的電路必須以正確的時(shí)序產(chǎn)生它的信號。如果響應(yīng)電路要

求先處理完一個(gè)請求,然后才能處理下一個(gè)請求,則響應(yīng)信號的時(shí)序就很重要。電路用它的響應(yīng)信號來指示它的處理任務(wù)何時(shí)完成。一種部分握手方法混合了電平與脈沖信號,而其它的方法則只使用脈沖信號。

在第一種部分握手方法中,電路 A 以有效電平聲明其請求信號,電路 B 則以一個(gè)單時(shí)鐘寬度脈沖作為響應(yīng)。此時(shí),電路 B 并不關(guān)心電路 A 何時(shí)中止它的請求信號。但為了使這種方法成立,電路 A 中止請求信號至少要有一個(gè)時(shí)鐘周期長,否則,電路 B 就不能區(qū)別前一個(gè)請求和新的請求。在這種握手方式下,電路 B 為請求信號使用一個(gè)電平同步器,電路 A 為響應(yīng)信號使用一個(gè)脈沖同步器。只有當(dāng)電路 B 檢測到請求信號時(shí)才發(fā)出響應(yīng)脈沖。這種情況可以使電路 A 通過控制其請求信號的時(shí)序,控制同步器接收到的脈沖間隔(圖 5)。同樣可以用經(jīng)驗(yàn)估算法確定時(shí)序,即信號跨越一個(gè)時(shí)鐘域要花兩個(gè)時(shí)鐘周期并且在跨越時(shí)鐘域前被電路寄存。

圖5,在一種部分握手方法中,電路 A 發(fā)出它的請求信號,電路 B 則以一個(gè)單時(shí)鐘寬度脈沖作為響應(yīng)。

全部的序列為 A 時(shí)鐘域最多三個(gè)周期加上 B 時(shí)鐘域最多五個(gè)周期。這種部分握手方法比全握手方法在 A、B 兩個(gè)時(shí)鐘域分別少用了兩個(gè)和一個(gè)時(shí)鐘周期。如果采用第二種部分握手方法可以再減少一些時(shí)鐘周期,此時(shí)電路 A 用一個(gè)單時(shí)鐘寬度脈沖發(fā)出它的請求,而電路 B 也用一個(gè)單時(shí)鐘寬度脈沖響應(yīng)這個(gè)請求。這種情況下,兩個(gè)電路都需要保存狀態(tài),以指示請求正待處理。

圖6,這種握手類型使用的是脈沖同步器,但如果其中一個(gè)電路時(shí)鐘比另一個(gè)電路時(shí)鐘快兩倍,則可以用邊沿檢測同步器來代替。

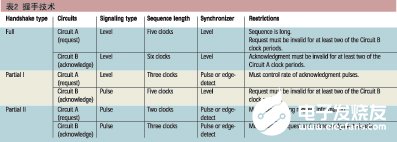

這種握手類型使用的是脈沖同步器,但如果其中一個(gè)電路時(shí)鐘比另一個(gè)電路時(shí)鐘快兩倍,則可以用邊沿檢測同步器來代替(圖 6)。完整的時(shí)序是:A 時(shí)鐘域最多兩個(gè)周期加上 B 時(shí)鐘域最多三個(gè)周期。所以這種部分握手技術(shù)與全握手方法相比,在 A 時(shí)鐘域少用三個(gè)時(shí)鐘周期,在 B 時(shí)鐘域也少用三個(gè)時(shí)鐘周期。同時(shí),也比第一種部分握手方法分別在 A、B 時(shí)鐘域快了一個(gè)和兩個(gè)周期(表 2)。這些握手協(xié)議針對的都是跨越時(shí)鐘域的單一信號。但當(dāng)幾組信號要跨越時(shí)鐘域時(shí),設(shè)計(jì)人員就需要使用更加復(fù)雜的信號傳送方法。

表 2

數(shù)據(jù)路徑設(shè)計(jì)

在進(jìn)行信號同步時(shí)有一個(gè)重要的規(guī)則,那就是不應(yīng)當(dāng)在設(shè)計(jì)中的多個(gè)地方對同一信號進(jìn)行同步,即單個(gè)信號扇出至多個(gè)同步器。因?yàn)橥揭ㄒ坏絻蓚€(gè)時(shí)鐘周期,設(shè)計(jì)者不能確切地預(yù)測到每個(gè)信號何時(shí)跨越一個(gè)時(shí)鐘域。此外,在新時(shí)鐘域中一組經(jīng)同步后的信號其時(shí)序是不定的,因?yàn)橥窖舆t可以是一到兩個(gè)時(shí)鐘周期,這與輸入信號到達(dá)同步器的時(shí)間有關(guān)。這種情況會在各個(gè)同步信號間形成一種“競爭狀況”。這種競爭狀況在需要跨越時(shí)鐘域傳輸?shù)亩嘟M信號間也會發(fā)生,例如數(shù)據(jù)總線、地址總線和控制總線等。因此,不能對組中的每個(gè)信號單獨(dú)使用同步器,也不能對數(shù)據(jù)或地址總線的每一位單獨(dú)使用同步器,因?yàn)樵谛碌臅r(shí)鐘域中,要求每個(gè)信號同時(shí)有效。

一種解決總線同步問題的方法是使用一個(gè)保持寄存器和握手信號。這種電路包括一個(gè)保持信號總線的寄存器,以及一個(gè)握手機(jī)制(圖 7)。握手信號指示新時(shí)鐘域的電路何時(shí)可以對總線采樣,以及源電路何時(shí)可以更換當(dāng)前寄存器中保存的內(nèi)容。

圖7,一種數(shù)據(jù)路徑同步器設(shè)計(jì)使用一個(gè)保持寄存器和握手信令。

在這種設(shè)計(jì)中,傳輸電路將數(shù)據(jù)(信號總線)存儲在保持寄存器,同時(shí)發(fā)出請求信號。這兩個(gè)動作可以同時(shí)發(fā)生,因?yàn)檎埱笮盘栔辽僖ㄒ粋€(gè)時(shí)鐘周期才能讓接收電路檢測到它(最小的握手-同步延遲)。當(dāng)接收電路采樣到數(shù)據(jù)(信號總線)時(shí),它發(fā)出一個(gè)響應(yīng)信號。這種設(shè)計(jì)使用了全握手方法,所以要花較長時(shí)間才能完成整個(gè)傳輸。對接收電路而言,使用全握手信號的設(shè)計(jì)有較大的時(shí)間窗口用于對信號總線采樣,因而效率較低。如用部分握手方法代替全握手方法則可以加快傳輸速度。

用這種總線同步方式,你可以同步握手信號,但不能同步信號總線。信號總線來自于保持寄存器,它在接收電路采樣前一直保持穩(wěn)定。注意,如果傳輸電路向接收電路提交數(shù)據(jù)太快以致來不及處理,則應(yīng)用中的總線同步可能不起作用。

高級數(shù)據(jù)路徑設(shè)計(jì)

在許多情況下,數(shù)據(jù)在跨越時(shí)鐘域時(shí)需要“堆積”起來,因此使用單個(gè)保持寄存器無法完成工作。例如一種情況是某個(gè)傳輸電路猝發(fā)式發(fā)送數(shù)據(jù),接收電路來不及采樣。另一種情況是接收電路采樣速度超出傳輸電路發(fā)送數(shù)據(jù)的速度,但采樣的數(shù)據(jù)寬度不夠。這些情況就要使用 FIFO 了。

基本上,設(shè)計(jì)者使用 FIFO 有兩個(gè)目的:速度匹配或數(shù)據(jù)寬度匹配。在速度匹配時(shí),F(xiàn)IFO 較快的端口處理猝發(fā)的數(shù)據(jù)傳輸,而較慢的端口則維持恒定的數(shù)據(jù)流。但是,雖然訪問方式和速度不同,但進(jìn)出 FIFO 的平均數(shù)據(jù)速率必須是相同的,否則 FIFO 就會出現(xiàn)上溢(overflow)或下溢(underflow)問題。與單寄存器設(shè)計(jì)相同,F(xiàn)IFO 將數(shù)據(jù)保存在寄存器或存儲器中,同時(shí)同步狀態(tài)信號,判斷何時(shí)可以把數(shù)據(jù)寫入 FIFO 或從 FIFO 中讀出。

在速度匹配應(yīng)用中,每個(gè)端口(讀或?qū)?的時(shí)鐘不同。FIFO 中的寄存器使用寫端口時(shí)鐘,就像保持寄存器使用電路時(shí)鐘來改變寄存器內(nèi)容一樣。信號同步發(fā)生在指針邏輯中,而且比握手信號要復(fù)雜得多。

現(xiàn)在指針邏輯的設(shè)計(jì)有多種方法。第一種方法是將讀、寫選通進(jìn)行同步,同時(shí)在各個(gè)時(shí)鐘域使用計(jì)數(shù)器來跟蹤 FIFO 中可用的項(xiàng)。計(jì)數(shù)器反映出可用于讀寫的 FIFO 項(xiàng)目號,計(jì)數(shù)器也與相應(yīng)的端口同步。讀計(jì)數(shù)器跟蹤包含有效數(shù)據(jù)的項(xiàng)數(shù),而寫計(jì)數(shù)器則跟蹤可以存儲數(shù)據(jù)的項(xiàng)數(shù)。當(dāng)對指針邏輯進(jìn)行復(fù)位時(shí),由于沒有數(shù)據(jù)可讀,讀計(jì)數(shù)器從零起始。寫計(jì)數(shù)器則從 FIFO 中項(xiàng)的總數(shù)開始計(jì)數(shù),即所有項(xiàng)均可用來存儲數(shù)據(jù)。

讀選通信號累減讀計(jì)數(shù)器,并與寫時(shí)鐘域同步,因?yàn)樗瑫r(shí)也累加寫計(jì)數(shù)器。寫選通信號則累減寫計(jì)數(shù)器,并與讀時(shí)鐘域同步,因?yàn)樗瑫r(shí)也累加讀計(jì)數(shù)器。

這種設(shè)計(jì)需要單時(shí)鐘寬度脈沖以及用于讀、寫選通的脈沖同步器,因?yàn)楫?dāng)一個(gè)電平信號從一個(gè)時(shí)鐘域跨越到

另一個(gè)更快的時(shí)鐘域時(shí),在較快時(shí)鐘域中它能在更多的時(shí)鐘周期中保持有效。由于只要讀或?qū)懶盘柺怯行У模總€(gè)計(jì)數(shù)器就會發(fā)生變化,因此較快的時(shí)鐘域就檢測到更多的讀、寫,超出較慢時(shí)鐘域?qū)嶋H發(fā)生的數(shù)量。脈沖同步器可以將一個(gè)時(shí)鐘域的時(shí)鐘寬度脈沖轉(zhuǎn)換為新時(shí)鐘域的時(shí)鐘寬度脈沖,每個(gè)脈沖都表示一次 FIFO 的讀或?qū)憽?/p>

這種 FIFO 狀態(tài)技術(shù)對讀、寫狀態(tài)都不太有利。當(dāng) FIFO 中所有項(xiàng)均充滿時(shí),寫端口狀態(tài)指示為滿,并在讀選通觸發(fā)后繼續(xù)指示 FIFO 滿,因?yàn)橥竭^程會使選通信號延遲送給寫計(jì)數(shù)器。讀端口為空時(shí)也會出現(xiàn)這種情況,因?yàn)橥竭^程會使寫選通信號延遲到達(dá)讀計(jì)數(shù)器。

這種設(shè)計(jì)的另一種考慮是及時(shí)檢測全滿/全空狀態(tài)。如果 FIFO 還有一項(xiàng)可用,并且有寫選通觸發(fā),則 FIFO 必須立即置為全滿狀態(tài)。這樣才能提前一個(gè)時(shí)鐘給出全滿標(biāo)志,使 FIFO 有足夠時(shí)間防止下一個(gè)數(shù)據(jù)寫入而產(chǎn)生溢出。對 FIFO 的讀端口也是這樣。這種情況下,如果 FIFO 里只有一個(gè)數(shù),并且有讀選通觸發(fā),則必須置全空狀態(tài),以給讀電路足夠的時(shí)間防止讀空 FIFO。

這種指針邏輯限制電路在每個(gè)時(shí)鐘周期中訪問 FIFO,即使在慢速時(shí)鐘域中也是這樣。這一功能的優(yōu)點(diǎn)在于訪問 FIFO 的電路至少有一個(gè)時(shí)鐘周期來評估 FIFO 的狀態(tài)。FIFO 可以將所有項(xiàng)都填滿數(shù)據(jù),而不會出現(xiàn)數(shù)據(jù)被覆蓋或全空無數(shù)據(jù)可讀的情況。這種設(shè)計(jì)的另一個(gè)優(yōu)點(diǎn)是每一端都可以讀其相應(yīng)的計(jì)數(shù)器,來判斷 FIFO 中還有多少項(xiàng)可用。設(shè)計(jì)者可以將這種 FIFO設(shè)計(jì)用在進(jìn)行多次數(shù)據(jù)讀/寫的電路中,而不會造成上溢或下溢的情況。

這種設(shè)計(jì)的不足之處是由計(jì)數(shù)器來判斷狀態(tài),而不是直接比較讀、寫指針。對大型 FIFO 來說,這些計(jì)數(shù)器也很大。而且,由于使用脈沖同步時(shí),來自較快時(shí)鐘域的讀、寫脈沖在較慢時(shí)鐘域的脈沖間至少必須有兩個(gè)時(shí)鐘周期,因此平均數(shù)據(jù)速率為最低時(shí)鐘頻率的一半。解決這些問題的一種方法是采用直接指針比較法。

在這種 FIFO 設(shè)計(jì)中,讀、寫指針的比較決定了 FIFO 的狀態(tài)。異步設(shè)計(jì)中的指針比較更富有挑戰(zhàn)性,因?yàn)槊總€(gè)指針位于不同的時(shí)鐘域中,對信號總線的同步要求在同步握手信號期間總線不發(fā)生改變。將這種技術(shù)用于指針同步的 FIFO 設(shè)計(jì)可能會很慢。要解決這個(gè)問題,F(xiàn)IFO 指針邏輯使用了格雷碼,代替指針使用的二進(jìn)制碼。

格雷碼在每一次計(jì)數(shù)增減時(shí)只改變其中的一位(表 3)。你可以在格雷碼總線上使用同步器,因?yàn)槊恳淮慰偩€改變時(shí)只有一根信號線有變化,于是就消除了格雷碼總線各位通過不同同步器時(shí)的競爭情況。這種設(shè)計(jì)的指針為格雷碼計(jì)數(shù)器。使用二進(jìn)制指針時(shí)需要將其變換成格雷碼后的同步指針,而使用變換邏輯會違反對同步信號的限制,即同步的信號在跨越時(shí)鐘域前要來自觸發(fā)器。

表 3

格雷碼計(jì)數(shù)器是一個(gè)二進(jìn)制累加器,在累加器前、后各帶有一個(gè)轉(zhuǎn)換器,分別用于格雷碼轉(zhuǎn)換為二進(jìn)制碼,和二進(jìn)制碼轉(zhuǎn)換為格雷碼(圖 8)。格雷碼與二進(jìn)制碼的轉(zhuǎn)換是一個(gè)異或運(yùn)算,所以只需比一個(gè)二進(jìn)制計(jì)數(shù)器多幾個(gè)邏輯電平。在格雷碼轉(zhuǎn)換成二進(jìn)制碼時(shí),使用:BN=GN;BN-1=BN+GN-1;BN-2=BN-1+GN-2 . B1=B2+G1;B0=B1+G0。而將二進(jìn)制碼轉(zhuǎn)換成格雷碼時(shí),使用:GN=BN;GN-1=BN+BN-1;GN-2=BN-1+BN-2 . G1=B2+B1;G0=B1+B0。在設(shè)計(jì)中可以采用同樣的技術(shù)來比較格雷碼指針的值,即在各個(gè)指針與二進(jìn)制比較邏輯之間增加轉(zhuǎn)換器。

圖8,格雷碼計(jì)數(shù)器是一個(gè)二進(jìn)制累加器,在累加器前、后各帶有一個(gè)轉(zhuǎn)換器。

用這種指針邏輯的 FIFO 很快,每個(gè)時(shí)鐘周期中電路都可以讀寫 FIFO。但是,在每個(gè)周期都訪問 FIFO 意味著 FIFO 狀態(tài)要包括“將滿”和“將空”兩種指示,這樣讀寫 FIFO 的電路才能有停止時(shí)間。“將滿”表示只能再寫入一項(xiàng),“將空”則表示只有一項(xiàng)可讀。這種情況描述了一個(gè)要求最少的可能狀態(tài)信號的設(shè)計(jì),以及一個(gè)需要更多指示的設(shè)計(jì),如果在固定的最小尺寸情況下用猝發(fā)方式訪問 FIFO 的電路的話。

這種 FIFO 狀態(tài)技術(shù)會給讀、寫帶來不良狀態(tài)。當(dāng) FIFO 滿時(shí),寫端口的狀態(tài)指示已滿,而在電路從 FIFO 中讀出一項(xiàng)后,該狀態(tài)仍為滿,因?yàn)橥綑C(jī)制使讀指針相對寫入一側(cè)的比較邏輯有個(gè)延遲。同樣,在讀出一側(cè)的空狀態(tài)指示也有這個(gè)問題,因?yàn)橥綑C(jī)制使寫指針相對讀出一側(cè)的比較邏輯有延遲。

如果你在設(shè)計(jì)跨不同時(shí)鐘域電路時(shí),使用一些技術(shù)來降低通信失敗的風(fēng)險(xiǎn),則處理跨時(shí)鐘域的信號就不再是艱巨的任務(wù)。同步機(jī)制可以防止接收跨時(shí)鐘域信號的觸發(fā)器出現(xiàn)亞穩(wěn)態(tài),從而避免導(dǎo)致不可預(yù)知的電路行為。對于在多個(gè)時(shí)鐘周期內(nèi)一直保持有效的信號來說,電平同步器的效果很好。對于要轉(zhuǎn)換成新時(shí)鐘域脈沖的較慢時(shí)鐘域電平信號,要采用邊沿檢測同步器。最后,對跨時(shí)鐘

域的脈沖信號應(yīng)使用脈沖同步器。還要記住,當(dāng)一個(gè)信號總線跨越時(shí)鐘域時(shí),整個(gè)總線要在同一個(gè)時(shí)鐘周期內(nèi)到達(dá)新的時(shí)鐘域。不要分別同步每一個(gè)信號,而要采用一個(gè)保持寄存器和握手方式。握手用來表示寄存器中的信號何時(shí)有效,何時(shí)可以采樣。對數(shù)據(jù)總線來說,握手和一個(gè)保持寄存器很有用,但每次向新時(shí)鐘域傳送的數(shù)據(jù)字不超過一個(gè)。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1630文章

21778瀏覽量

604823 -

控制器

+關(guān)注

關(guān)注

112文章

16421瀏覽量

178848 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2002瀏覽量

61267

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA電路設(shè)計(jì)的一些技巧

FPGA/CPLD 數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)和一些設(shè)計(jì)方法

我想學(xué)習(xí)一些接口電路設(shè)計(jì)

數(shù)字電路一些經(jīng)典問答

記錄一些關(guān)于電路設(shè)計(jì)上的一些知識

PLD設(shè)計(jì)技巧—采用同步電路設(shè)計(jì)

資深電子工程師教你:電路設(shè)計(jì)中的一些錯誤想法與原因分析

電子電路設(shè)計(jì)的一些技巧注意事項(xiàng)

同步電路設(shè)計(jì):將系統(tǒng)狀態(tài)的變化與時(shí)鐘信號同步

硬件設(shè)計(jì)——關(guān)于電路設(shè)計(jì)的一些知識

在電路設(shè)計(jì)中采用一些技巧解決信號同步問題

在電路設(shè)計(jì)中采用一些技巧解決信號同步問題

評論