引言

對于碼分多址的擴頻通信方式而言,只有當接收端本地偽碼與發端偽碼處于相同相位狀態時,有用的信息才能被解出。因此,擴頻序列相位的捕獲與跟蹤是擴頻通信系統的關鍵,而偽碼序列相位的捕獲尤為重要。滑動相關法是常用的方法之一。擴頻通信系統要求實時性,以及較高的數據處理速度,這正是FPGA的優勢。所以在擴頻通信系統中,大量應用FPGA芯片作為前級處理芯片。

實現原理

原理分析

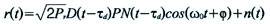

接收機端接收到的擴頻信號可以表示為:

其中,P_{r}為接收信號功率,τ_a5mgapgs4i為傳輸時延,D(t)為信息碼, PN(t)為偽碼, n(t)為傳輸過程的加性噪聲。擴頻接收機要完成的任務就是去掉PN(T-τ_a5mgapgs4i) 偽碼項和cos(ω_{0}t+φ) 載波項,從而得到信息數據DZ(t)。

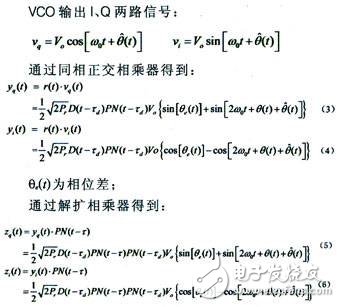

VCO輸出I、Q兩路信號:

通過同相正交相乘器得到:

利用PN碼的相關特性,即相位對齊時,相關結果最大。當載波和碼相位都對準時,經過累加清洗(低通濾波)輸出為:

經過平方相加可去掉載波對相關結果的影響,得到相關峰。

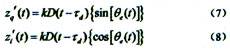

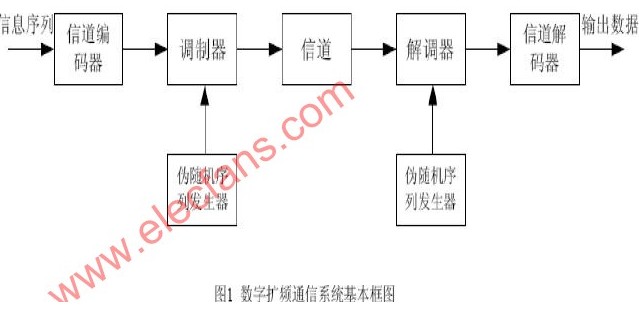

實現框圖

在直接序列擴頻系統中,偽碼的捕獲是構成碼同步系統的重要結構,也是直擴系統中必不可少的部分。接收機若要把偽碼擴展的信號解出,接收方就必須能產生一個與發方一樣的偽碼序列(保證最大相關值),而且,該本地偽碼速率、相位要與接收到的偽碼保持一致。對于約定好的收、發方用同一個偽碼很容易辦到,但是,如果要從解擴相關器得到傳送的信息,僅僅保證一樣的碼型是遠遠不夠的。因為即使相同的偽隨機碼,當相位差大于一個碼片時,它們的相關峰就完全消失。在實際通信中,由于收、發信機時鐘的不穩定性,接收、發射時刻的不確定性,信道傳輸延遲及干擾等因素的影響,收、發偽碼序列的相位差是隨機的。因此解擴的第一步就是要在接收信號的偽碼相位中捕獲到一個與本地偽碼一致的相位狀態。當這種狀態出現時相關器就會有一個相關峰值輸出,峰值與門限相比,若超出則確定相位已捕捉到,立即停止捕捉動作,轉入相位跟蹤狀態;若小于門限則改變本地碼相位,繼續進行捕獲。系統實現原理如圖1所示。

實現方法

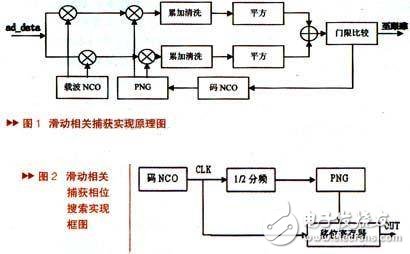

根據相位捕獲的方法可分為:連續相位滑動相關法和在此思路上改進的不連續相位相關法。

連續相位滑動相關法

此方法是通過改變本地偽碼時鐘速率,與發端偽碼時鐘速率保持一個合適偏移量,使接收信號中偽碼相位與本地偽碼相位在相關器內進行相對滑動。這種方法的相位捕獲是連續進行的,所以相關峰值是一個連續量。相關值一旦超過捕獲門限,標志正確相位已被搜索到,接收機立即恢復本地偽碼時鐘速率(收、發信機都使用穩定度很高的振蕩源,所以它們的碼速率可以基本保持一致),停止相位滑動,啟動跟蹤電路,使相位差進一步縮小(意味著相關性增大),獲得更高解擴信噪比,滿足其后解調門限要求。此種捕獲方法捕獲時間和檢測概率相互矛盾。例如,對于一個N=215位的PN碼,兩偽碼之間最大相對滑動速率約為5kc/ps,遍歷其所有相關狀態需要的時間為6.55S。在實際通信過程中,由于干擾及其它原因造成偽碼相位失鎖需要重新捕捉時,這么長的捕捉時間會嚴重影響通信質量,因而是不可取的。由以上分析可知,這種捕捉方法相位搜索精度高但同時導致了過長的捕捉時間,在實際中很少應用,但其思路值得借鑒。不連續滑動相關法就是在此基礎上的改進。

不連續相位滑動相關法

所謂連續與不連續的區別是對搜索中相位的滑動變化量而言,后一種方法是把連續的相位搜索改為跳躍式的搜索,即兩個碼之間的相位滑動量不再是連續地以一定的步進量產生相位滑動。不連續滑動相關法是利用一個相位搜索電路,在捕獲過程中使本地偽碼相位以一定的步進值跳躍變化,這樣遍歷整個偽碼時間大大減少。與前一種方法相比,它的收、發偽碼時鐘速率保持一致,從而不會造成碼片寬度不一致,導致相關峰值下降。本地偽碼與接收偽碼相位的相對改變是靠搜索電路對偽碼發生器時鐘的超前、滯后控制來實現的,因此相位搜索電路(如圖2所示)是不同于前者的關鍵所在。下面重點討論實現半碼片滑動的實現方法。

捕獲方法1 (滑動步進為TC/2)

時鐘取反法:

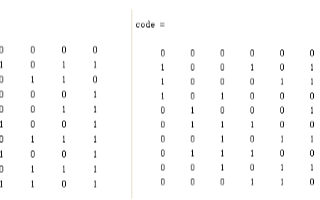

如圖1所示,當信號包絡的平方小于門限時,輸出控制信號,對圖2中CLK取反,取反的結果相當于利用原CLK時鐘下降沿進行觸發。經過二分頻后作為偽碼產生器的時鐘,同時把CLK作為移位寄存器的時鐘,三位移位寄存器的輸出相當于移動了半個碼片。FPGA仿真結果如圖3所示。

圖中data1,data2,data3,分別為三位移位寄存器的輸出,01表示+1,11表示1,clk1為碼NCO的輸出,clk2為它的二分頻。此方法在整個系統中要多次對時鐘進行取反操作,會帶來比較嚴重的時序問題,使系統工作時序滿足不了。為了解決此問題,可采用改進的方法。

捕獲方法2 (滑動步進為TC/2)

時鐘取反法改進:

此方法采用觸發器結構,把2倍的CLK作為輸入,CLK作為使能端,利用FPGA自帶的IP核--鎖相環使CLK相位超前,包住2倍CLK的上升沿,觸發器的輸出即為CLK,FPGA仿真結果如圖4所示。圖中,co為輸入端,pn為鎖相環的輸出作為使能端。對使能端取反操作,通過圖2的電路結構即可完成半碼片的移動。但是,同時要對二分之一CLK進行鎖相操作,如果實現多路,由于FPGA內部只有2個鎖相環,所以,實用性受到限制。

捕獲方法3 (滑動步進為TC/2)

加脈沖移位法:

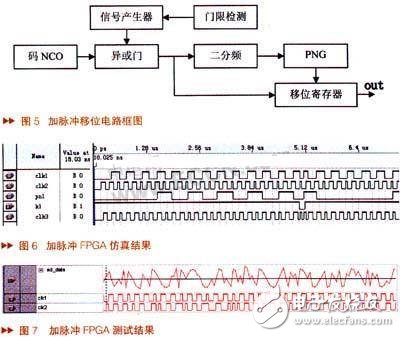

此方法是采用一個異或門,如圖5所示,使碼NCO的輸出CLK與一個信號異或輸出,此信號平時一直為高(或低)電平,一旦收到低于門限值時,輸出一個低(或高)脈沖,與CLK異或后,相當于在原CLK時鐘上加了一個脈沖,通過圖示的電路后,偽碼產生器前進了半個相位,通過移位寄存器后,即可實現半個碼相位的移動(超前半個碼片)。

FPGA仿真結果如圖6所示。圖中CLK1為碼NCO的輸出,CLK2為它的二分頻作為偽碼產生器的時鐘,pn1為偽碼產生器輸出,k1為信號,平常輸出高電平,當門限檢測結果為低時,輸出一個低脈沖與CLK1異或輸出,結果為CLK3。從仿真圖中可以看出CLK3相對于CLK2在k1為低脈沖時,增加了一個脈沖。

下載到FPGA中,利用SIGNALTAP,測試結果如圖7所示。圖中CLK1為碼NCO輸出時鐘,CLK2為異或門的輸出,從圖中可以看出,在門限檢測為低時,CLK2比CLK1多增加了一個脈沖,測試結果與仿真結果一致。

實現結果

通過以上的分析,再結合擴頻通信的有關理論,可以知道要實現信號的捕獲,必須通過載波和偽碼相位的二維搜索。首先,對接收的信號進行數字下變頻,變為零中頻I、Q兩路信號,再與本地PN碼進行解擴運算。結果與門限值比較,如果小于門限則按照前面分析的方法順序移動半個碼片,直到包絡的平方大于門限轉入跟蹤狀態。捕獲電路如圖1所示。

采用上述方法,在實際中對某一擴頻信號進行捕獲

信號參數

中頻40MHz ;

調制樣式為DS-BPSK;

偽碼長度為1024;

數據率5Kb/s;

采樣時鐘60MHz;

各個模塊功能描述

數字下變頻:

載波NCO的輸出與輸入信號在乘法器中進行數字下變頻,功能是去除輸入信號載頻而保留了用于基帶相關的碼。

數字相關器:

累加清除器的作用是對經過數字正交下變頻后的I、Q兩路信號與本地再生偽碼相乘的結果進行積分累加。采用的是一個累加器對數字混頻后輸入信號與本地碼相乘的每一位結果進行累加。經過一定時間(本方案為12000次)的積分累積后,得到一個數據位的相關值。此相關值與預設門限比較,進行捕獲判決。如果小于門限,則認為捕獲失敗,清除累加結,滑動半個碼片后,重新進行累加積分。累加清洗器進行一個碼周期的數據累加,輸出一次相關累加值。最大的捕獲時間為0.4094秒(0.2mS*2047)。

載波NCO:

載波NCO是載波跟蹤環的重要組成部分,它的主要功能是產生本地復制載波信號。載波NCO模塊設置有頻率控制字輸入接口,模塊內部通過32位相位累加其對輸入控制字進行累加,獲得相位值的映射地址,通過查表獲得正余弦兩路信號。載波環路通過不斷調整載波NCO的頻率字來保持對接收信號載波頻率和相位的跟蹤。

碼NCO:

碼NCO是碼跟蹤環的核心。它的主要功能是為再生偽碼發生器提供精確的時鐘信號,保證實現對接收信號的碼捕獲和跟蹤。碼NCO設置有頻率控制字,頻率控制字負責碼率的調整和碼相位延時。

實現結果

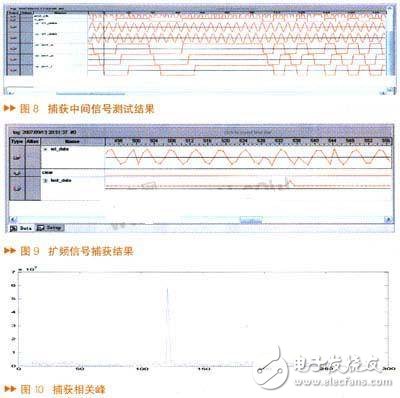

A/D采用AD9288-100,是8位的轉換結果,最高工作頻率可達到100M,數字下變頻和捕獲電路在EP1C12Q240C8(Cyclong)中實現,運算的中間測試結果如圖8所示,圖中pn2_clk為NCO輸出時鐘,x_pn為偽碼,c1_data和s1_data為載波NCO產生的用于下變頻的I、Q路載波信號。pn_e、pn_p、pn_l分別為移位寄存器輸出的超前、即時和滯后碼,它們相差半個碼片。

最后的捕獲結果如圖9所示。圖中ad_data為接收的數字中頻信號,last_data為最后捕獲的結果。

保存數據,在Matlab中的相關結果如圖10所示。

結束語

加脈沖法可以使本地碼相位超前半個碼片相位,實現非連續相位滑動相關,電路結構簡單,在FPGA中容易實現,是一種簡單實用的方法,在實際系統設計中已被采用并獲得了理想的結果。

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603431 -

通信

+關注

關注

18文章

6032瀏覽量

135995 -

發生器

+關注

關注

4文章

1368瀏覽量

61697

發布評論請先 登錄

相關推薦

擴頻通信理論基礎+主要介紹bpsk的調制

基于FPGA實現CDMA擴頻通信中的同步系統畢業設計

擴頻通信系統簡介

擴頻通信調制器的FPGA設計與仿真

什么是擴頻通信,擴頻通信的定義

跳時擴頻通信系統

FPGA在多進制正交擴頻通信系統中的應用

擴頻通信的基本原理(SystemView仿真)

FPGA芯片在擴頻通信系統中的優勢及應用介紹

FPGA芯片在擴頻通信系統中的優勢及應用介紹

評論