引言

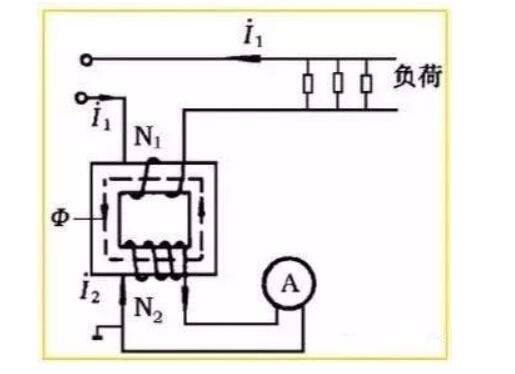

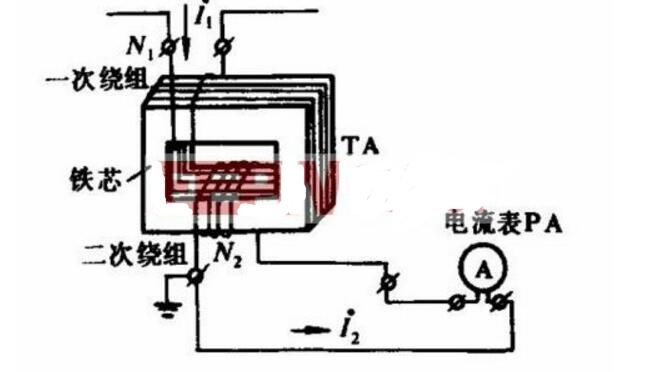

電流互感器是電力系統(tǒng)中用于繼電保護和電流測量的重要設(shè)備,其精確度和可靠性對電 力系統(tǒng)的安全、穩(wěn)定和經(jīng)濟運行有著重要影響。隨著電力系統(tǒng)的發(fā)展,發(fā)電和輸變電容量不 斷增加,電網(wǎng)電壓不斷提高,對互感器提出了許多新的和更加嚴格的要求,而傳統(tǒng)的電磁式 互感器已經(jīng)越來越不適應(yīng)這種發(fā)展的需要。基于光學(xué)技術(shù)、電子技術(shù)、現(xiàn)代信號處理技術(shù)的 新一代光電電流互感器克服了傳統(tǒng)電流互感器存在的磁飽和及鐵磁諧振等一系列問題,與新 型的光電子技術(shù)相結(jié)合,具有精度高、智能化等傳統(tǒng)電磁式互感器無法比擬的優(yōu)勢,應(yīng)用前 景十分樂觀。現(xiàn)在光電電流互感器的研究方向主要是有源電子式電流互感器。有源電子式電 流互感器系統(tǒng)主要分為三個部分:高壓側(cè),低端側(cè)和供電電源。

高壓側(cè)部分主要包括:傳感器和高壓側(cè)電路模塊。傳感器現(xiàn)在主要是采用Rogowski 線圈 (羅氏線圈)。而高壓側(cè)電路模塊主要包括:積分器,放大器,低通濾波器,模數(shù)轉(zhuǎn)換器和嵌 入式微處理器。高壓側(cè)電路模塊是光電電流互感器的重要組成部分,其精度、暫態(tài)響應(yīng)速度 和功耗等主要性能參數(shù)對互感器有著重要的影響。

2 高壓側(cè)電路模塊設(shè)計

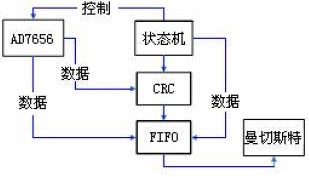

傳統(tǒng)的高壓側(cè)電路模塊是由前期處理電路、模數(shù)轉(zhuǎn)換模塊、控制單元MCU、CRC 校驗碼單 元與曼切斯特編碼單元幾部分組成。作為高壓側(cè)主控單元的MCU,它主要反映了暫態(tài)響應(yīng)速度和功耗兩個參數(shù),MCU 的選擇可以是DSP、單片機。DSP 速度快功耗大;低功耗單片機則在速 度方面很難達到要求。隨著大規(guī)模集成電路技術(shù)和計算機技術(shù)的不斷發(fā)展,FPGA(Field programmable Gate Array)作為當今比較流行的嵌入式芯片有著其他芯片無法替代的優(yōu)點, 成為當今應(yīng)用最廣泛的可編程專用器件。本文將A/D 控制模塊,CRC 校驗碼模塊和曼切斯特編 碼模塊的功能合并到FPGA 當中,圖1 為FPGA 內(nèi)部功能框圖。

2.1 利用狀態(tài)實現(xiàn)對A/D 的控制

模數(shù)轉(zhuǎn)換器是整個系統(tǒng)中比較重要的器件,本文采用ADI 公司生產(chǎn)的6 通道同時采樣模 數(shù)轉(zhuǎn)換器AD7656。設(shè)計中,F(xiàn)PGA 對AD7656 的控制、讀寫時序由狀態(tài)機來實現(xiàn)。本文把控制 過程分成4 個狀態(tài)分別為ST0、ST1、ST2、ST3。ST0:AD 初始化,ST1:啟動轉(zhuǎn)換、等待轉(zhuǎn)換 結(jié)束,ST2:轉(zhuǎn)換結(jié)束、準備讀出數(shù)據(jù),ST3:讀出數(shù)據(jù)、給計數(shù)器控制信號。

2.2 FPGA 芯片內(nèi)的存儲器的設(shè)計

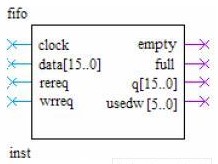

本文在FPGA 內(nèi)部設(shè)計一個16 位的FIFO 來實現(xiàn)數(shù)據(jù)的存儲,用VHDL 語言來實現(xiàn),芯片 內(nèi)存儲器的結(jié)構(gòu)圖如圖2 所示。圖中data 為數(shù)據(jù)輸入端,wreq 為寫控制信號,rdreq 為讀控 制線,q 為數(shù)據(jù)輸出端,clock 為時鐘。Usedw 為地址信號輸出線。

2.3 CRC 校驗碼的FPGA 設(shè)計

光纖通信過程中,在接收方檢查所接收的數(shù)據(jù)是否正確,可采用多種檢測方法。其中循環(huán)冗 余校驗碼(CRC 校驗)是目前在計算機網(wǎng)絡(luò)通信及存儲器等方面應(yīng)用最為廣泛的一種校驗編碼方 法,是一種強有力的檢測手段。人們將該技術(shù)用于多處數(shù)據(jù)通信系統(tǒng)中,收到了令人滿意的效果。

為了滿足電力通信的快速性、可靠性要求,本文采用CRC 并行算法來實現(xiàn)CRC 編碼。 CRC 校驗碼的原理是發(fā)送端運用CRC 算法計算出待發(fā)送數(shù)據(jù)的CRC 校驗碼。并附加在待發(fā)送 數(shù)據(jù)的末尾,即在發(fā)送數(shù)據(jù)的同時增加CRC 碼(編碼過程)。發(fā)送后,接收端計算機檢測數(shù)據(jù)和CRC 碼之間的數(shù)學(xué)關(guān)系是否正確(譯碼過程),若不正確則說明數(shù)據(jù)信息在傳輸過程中有誤碼。

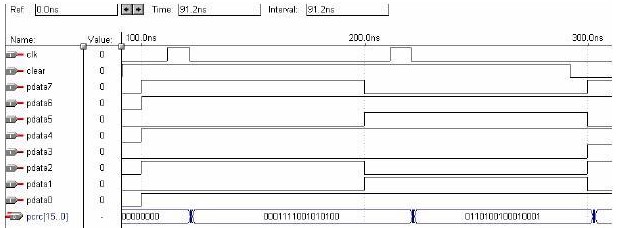

FPGA 已經(jīng)成為當今應(yīng)用最廣泛的可編程專用器件,它解決了傳統(tǒng)數(shù)字電路設(shè)計中所遇到的許多問題,能夠快捷地、靈活地實現(xiàn)復(fù)雜數(shù)字系統(tǒng)的設(shè)計。本文開發(fā)軟件采用Max+plusⅡ,用VHDL 語言編譯實現(xiàn)CRC 檢驗算法。并給出了一組隨機的16 進制數(shù)做了仿真,仿真結(jié)果如圖3 所示:從 圖中可以看出結(jié)果不僅可以準確地反應(yīng)出CRC 校驗碼的數(shù)組,而且由于優(yōu)化的原因波形比較平滑, 達到了預(yù)期的效果。

2.4 曼徹斯*的實現(xiàn)

光纖傳送數(shù)據(jù)的速率很高,用異步方法恢復(fù)時序己經(jīng)很不實際了,如果在接收端不能從數(shù)據(jù) 中恢復(fù)時鐘信號,那么就需要另一條光纖來傳時鐘,這樣不經(jīng)濟而且會造成時基擺動。所以在光 纖數(shù)據(jù)傳輸系統(tǒng)中又要選用合適的線路碼,而曼徹斯*(Manchester)是當今光纖數(shù)據(jù)通信中 最常用的一種。

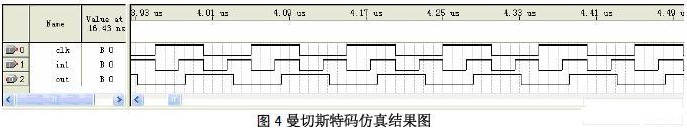

曼徹斯*又叫做數(shù)字雙相碼,是用碼元中心的電平跳變來表示要傳輸?shù)亩M制信息,是一 種時鐘自同步編碼技術(shù)。曼徹斯*的編碼方法是將每一個碼元再分成兩個相等的間隔。碼元1 是在前一個為高電平而后一個間隔為低電平。碼元0 則剛好相反,從低電平變到高電平。它的優(yōu) 點在于可以保證在每個碼元的正中間出現(xiàn)一次電平的轉(zhuǎn)換,這除了可以防止基帶信號出現(xiàn)連1 或 連0 的現(xiàn)象,又對接收端提取位同步信號是非常有利的。在實際電路設(shè)計中,本文用異或門來實 現(xiàn)編碼的設(shè)計,但是在編碼過程中由于時鐘信號有上升時間和下降時間導(dǎo)致編碼完的信號有毛刺, 本文用D 觸發(fā)器來消除這些毛刺。

本文對曼切斯特編碼電路作了仿真,圖4 為曼切斯特編碼仿真圖,從圖中可以看出輸出信號 在輸入信號的中心位置跳變,并且信號沒有毛刺比較平滑,成功地完成了編碼。

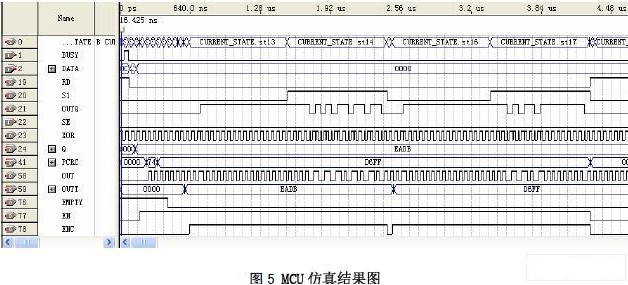

2.5 MCU 綜合模快

本文已將圖1 中的各個主要模塊用VHDL 語言進行了編譯和仿真,由仿真結(jié)果可以看出每一個 模塊已經(jīng)完成了它自己的功能。但是作為FPGA 的時序綜合又是一個很復(fù)雜的工作,如何將各個模 塊的功能結(jié)合在一起完成整個系統(tǒng)的功能、如何搭配各個模塊間的時序讓整個系統(tǒng)的時序比較合 理都是要考慮的問題。

本文對高壓側(cè)MCU 綜合模快電路作了仿真,如圖5 所示。給出了一個采集周期的仿真結(jié)果。

從仿真圖可以看出整個MCU 模塊完成了從控制A/D 采集數(shù)據(jù);控制CRC 校驗碼電路進行校驗碼的生成;將數(shù)據(jù)存入存儲器經(jīng)過組合之后送入曼切斯特編碼模塊進行編碼,最后將結(jié)果輸出。

3 結(jié)論

本文把FPGA 技術(shù)應(yīng)用在高壓側(cè)模數(shù)轉(zhuǎn)換器的控制、CRC 校驗碼、曼切斯特編碼等各模塊的電 路設(shè)計上。主要功能包括:控制模數(shù)轉(zhuǎn)換器采集信號;對采集的數(shù)字信號進行CRC 校驗;把校驗 碼和采集數(shù)據(jù)存入存儲器并按格式進行排序;把排序好的數(shù)據(jù)輸入曼切施*編碼電路在通過光 纖傳到低壓側(cè)。采用現(xiàn)場可編程門矩陣FPGA 來做整個高端側(cè)的時序控制器。同時采用FPGA 來實 現(xiàn)編碼、解碼部分的設(shè)計,這樣可以把多個功能集成到一個芯片當中進一步提高效率。通過仿真 結(jié)果可以證明本文的高壓側(cè)信號處理電路設(shè)計是可行的,且能夠滿足電力系統(tǒng)中IEC60044-8 標準 所規(guī)定的高效性、時效性要求。

-

電源

+關(guān)注

關(guān)注

184文章

17740瀏覽量

250566 -

mcu

+關(guān)注

關(guān)注

146文章

17171瀏覽量

351506 -

互感器

+關(guān)注

關(guān)注

12文章

782瀏覽量

38706

發(fā)布評論請先 登錄

相關(guān)推薦

[原創(chuàng)]電流互感器的作用是什么

電流互感器二次側(cè)測量電路

漲知識:告訴你什么是電流互感器

電流互感器二次側(cè)為什么不能開路的原因何在

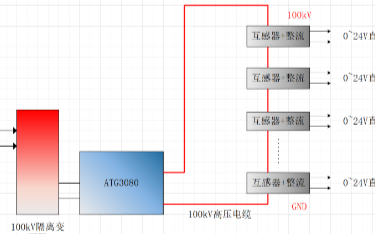

ATG-3080功率信號源在電流互感器高壓側(cè)電源研發(fā)測試中的應(yīng)用

功率放大器在電流互感器高壓側(cè)電源研發(fā)測試中的應(yīng)用

光電電流互感器高壓側(cè)編碼模塊的設(shè)計

10+kV低功耗光電電流互感器的研究

電流互感器的原理_電流互感器二次側(cè)為什么不能開路

關(guān)于電流互感器高壓側(cè)電源的研發(fā)

采用FPGA技術(shù)的光電電流互感器高壓側(cè)信號處理電路的設(shè)計方案

采用FPGA技術(shù)的光電電流互感器高壓側(cè)信號處理電路的設(shè)計方案

評論