傳統的綜合技術越來越不能滿足當今采用 90 納米及以下工藝節點實現的非常大且復雜的 FPGA 設計的需求了。問題是傳統的 FPGA 綜合引擎是基于源自 ASIC 的方法,如底層規劃、區域內優化 (IPO,In-place Optimization) 以及具有物理意識的綜合 (physically-aware synthesis) 等。然而,這些從 ASIC 得來的綜合算法并不適用于 FPGA 的常規架構和預定義的布線資源。

最終的結果是,所有的三種傳統 FPGA 綜合方法需要在前端綜合與下游的布局布線工具之間進行多次耗時的設計反復,以獲得時序收斂。這個問題的解決方案是一種基于圖形的獨特物理綜合技術,能夠提供一次通過、按鈕操作的綜合步驟,不需要 ( 或者需要很少 ) 與下游的布局布線引擎的設計反復。而且,基于圖形的物理綜合在總體的時鐘速度方面可以將性能提高 5% 到 20% 。 Synplify Premier 先進 FPGA 物理綜合工具就是這樣一種工具,專門針對那些設計很復雜的高端 FPGA 設計工程師而定制,他們的設計需要真正的物理綜合解決方案。

本文首先介紹了主要的傳統綜合方法,并說明這些方法存在的相關問題,然后介紹基于圖形的物理綜合概念,并指出這種技術如何滿足當前先進 FPGA 的設計需求。

傳統綜合解決方案存在的問題

對于 2 微米的 ASIC 技術節點以及上世紀 80 年代早期以前來說,電路單元 ( 邏輯門 ) 相關的延時與互連 ( 連接線 ) 相關延時的比例約 80:20 ,也就是說門延時約占每個延時路徑的 80% 。這樣一來,設計師可以用連線負載模型來估計互連延時,在連線負載模型中,每個邏輯門輸入被賦予某個 “ 單位負載 ” 值,與某個特定路徑相關的延時可以作為驅動門電路的強度和連接線上的總電容性負載的函數來計算得出。

類似地,當在上世紀 80 年代后期 ( 大約引入 1 微米技術節點的時候 ) 第一個 RTL 綜合工具開始用在 ASIC 設計中的時候,電路單元的延時與連線延時相比還是占主導地位,比例約為 66:34 。因此,早期的綜合工具還是基于它們的延時估計方法,并使用簡單的連線負載模型進行優化。由于電路單元的延時占據主導,因此初期綜合引擎使用的基于連線負載的時序估計足夠準確,下游的布局布線引擎通常能在相對較少的幾次反復 ( 在 RTL 和綜合階段之間 ) 條件下實現設計。

然而,隨著每個后續技術節點的引入,互連延時大大地增加 ( 事實上,就 2005 年采用 90 納米技術實現的標準單元 ASIC 來說,電路單元與互連的延時比例現在已經接近 20:80) 。這使得綜合引擎的延時估計與布局布線后實際延時的關聯性越來越低。

這具有一些很重要的牽連性,因為綜合引擎在不同的優化方法之間選擇,以及在實現功能的替代方法 ( 諸如基于它們的時序預測的加法器 ) 之間選擇。例如,假設某個包含一個加法器 ( 以及其它組件 ) 的特定時序路徑被預知具有一些 ( 時序 ) 裕量,這種情況下,綜合工具可以選擇一個占用芯片面積相對較小的較慢加法器版本。但是,如果時序估計與實際的布局布線后延遲情況出入比較大的話,這個路徑可能最后非常慢。這樣一來,不準確的延時估計意味著綜合引擎最后才對不正確的對象進行優化,只有在完成了布局布線后你才發現問題并不是像你 ( 或綜合引擎 ) 所想的那樣,其結果是獲得時序收斂所需的工作量將大大地增加,因為從前端到后端的設計反復次數大大增加了。

為了解決這些問題,有必要了解在綜合過程中與設計相關的物理特性。因此,隨著時間的推移, ASIC 綜合技術 ( 緊跟著 FPGA 綜合技術 ) 采用了一系列的方法 ( 某些情況下也拋棄了一些方法 ) ,例如下面討論的底層規劃、 IPO 和具有物理意識的綜合。

底層規劃

對于 ASIC 的 RTL 綜合,底層規劃技術在上世紀 90 年代早期出現,稍晚于綜合技術本身的問世。底層規劃工具允許設計師在器件上定義物理區域,通過手工或者使用自動交互技術來對這些區域布局,并將設計的不同部分分配到這些區域。

底層規劃涉及到逐個模塊地綜合和優化設計,然后在最后將所有東西 “ 縫合 ” 在一起 ( 早期底層規劃工具使用的綜合算法都是基于連接線負載模型 ) 。這意味著底層規劃工具不能按每個單元優化邏輯,只能影響邏輯模塊的布局。而且,在定義上,底層規劃工具不會全局性地考慮布線資源,在設計完全布線完成之前,它不可能準確分析所有的時序路徑。這會導致在前端和后端工具之間的大量耗時的設計反復。盡管這種方法可以提高 ASIC 設計的時序性能和降低功耗,但它需要對設計的復雜分析和很高的專業技術水準。

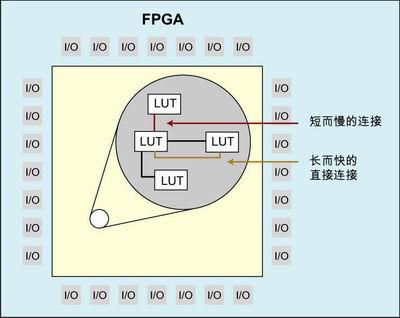

圖 1 : FPGA 的主流架構。

在早期,采用 ASIC 底層規劃有下面幾個原因:作為一種獲得時許收斂的方法解決有限容量的問題,并支持基于逐個模塊的遞增變化。最近,底層規劃不再被認為是一種其本身能獲得時序收斂的方法;底層規劃依然是一種有用的方法,但只是在與其它方法 ( 例如物理優化 ) 結合的時候才有用,使用綜合后門級網表的底層規劃依然需要非常多的專門技術。

對于 FPGA 來說,直到上世紀 90 年代晚期,底層規劃技術還沒有成為主流應用。平均而言,在一個 FPGA 設計中,關鍵路徑一般會經過 3 個區域。由于 FPGA 一般用到的設計方法,如果使用綜合后 (“ 門級 ”) 網表來執行底層規劃,即使對 RTL 的相對較小的改變都可能導致先前所做的底層規劃工作付之東流。解決這個問題的方法是在 RTL 級進行底層規劃。然而,為了更有用,這必須和某種形式的物理優化相結合,源于 ASIC 的物理綜合算法并不適合于 FPGA 的常規架構以及預定義的布線資源。

布局優化

隨著底層規劃在 ASIC 領域的作用逐漸弱化,在上世紀 90 年代中期, IPO 技術對其進行了強化 / 或者替代。這再次地涉及到時序分析和估計是基于連接線負載模型的綜合。

在這種情況下,所產生的網表被傳遞到下游的布局布線引擎。在布局布線和寄生提取之后,實際的延時被背注到綜合引擎。這些新值觸發器在綜合引擎中的遞增優化,例如邏輯重構和復制。其結果是得到一個被部分修改的新網表。然后,這個網表被遞交到遞增布局布線引擎,產生一個改進的設計拓撲。

基于 IPO 流程所得到的最后結果比那些采用底層規劃方法獲得的通常更好。然而,這種方法同樣可能需要在前端和后端工具之間進行很多次設計反復。而且基于 IPO 方法的一個重要的問題是對布局布線的修改可能導致新的關鍵路徑,這個路徑在前一次反復中是看不到的,即修正一個問題可能會激起其它的問題,這可能導致收斂的問題。

對于 FPGA 設計,基于 IPO 的設計流程大約在 2003 年開始受到主流關注。然而,盡管這樣的流程已經可用,但那時這些流程并沒有以一種有意義的方式得到采用,因為單個地優化時序路徑的 IPO 技術通常導致其它路徑時序的劣化和時序收斂不完全。設計師需要可使他們在不犧牲之前設計版本獲得的成果的基礎上對設計進行改變的可靠結果。但是基于 IPO 的方法并不能在多次設計反復之上產生穩定的結果,因為在一次反復中優化關鍵路徑會在下一次反復中產生新的關鍵路徑。類似地,增加約束以改進一個區域的時序可能使其它的區域的時序惡化。

具有物理意識的綜合

當前先進的 ASIC 綜合技術是具有物理意識的綜合,這種綜合技術在大約 2000 年開始受到主流關注。不考慮實際的技術 ( 有幾種不同的算法 ) ,具有物理意識的綜合的基本概念是在一次性完成的過程中結合布局和綜合。

這在 ASIC 領域中的實踐效果很好,因為了解布局的綜合引擎能根據已布局的單元的周邊和 Steiner 以及 Manhattan 布線估計進行時序的預估。這種綜合方法在 ASIC 中效果很好的原因是連接線有序地布置。這意味著與最后的布局和布線設計相關的延時與綜合引擎所估計的結果具有非常好的相關性。

從 2002 年到 2003 年期間開始,很多的 EDA 供應商開始考慮將從 ASIC 中得到的具有物理意識的綜合技術應用到 FPGA 設計中,但是他們并沒有進一步將這種思路深入下去,而 Synplicity 公司新的基于圖形的綜合方法是一個例外,現在沒有供應商能提供具有布局意識的 RTL 綜合工具用于 FPGA 設計。問題是,與 ASIC 中的連線 “ 按序構建 ” 不同的是, FPGA 具有固定數量的預先確定的布線資源,并不是所有的布線都設置成一樣 ( 某些連線短且快,某些長而快,某些短而慢,某些長而慢 ) 。

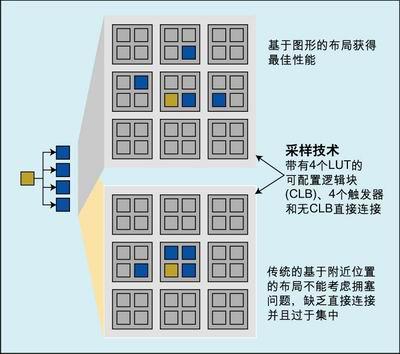

對于實際的情況而言,基于 ASIC 的具有物理意識的綜合可以根據形成設計的已布局單元的附近來進行布線和時序估計。而對于 FPGA 來說,將兩個邏輯功能放在相鄰的區域并不一定能實現它們之間的快速連接。 - 取決于可用的布線資源,將相連接的邏輯功能布局位置更遠可能反而能獲得更好的布線和時序結果,盡管這有一點違背常理。這就是為什么從 ASIC 設計中得來的具有物理意識的綜合技術用于 FPGA 架構時并不能得到最佳結果的原因。同樣,使用這些技術的設計流程需要大量耗時的前端 ( 綜合 ) 與后端 ( 布局與布線 ) 引擎之間的設計反復,以獲得相關性和時序收斂。

與 FPGA 架構相關的一些考量

在詳細介紹基于圖形的物理綜合概念之前,先了解設計任務的復雜性很重要。正如前面談到的, FPGA 具有固定的連接資源,所有連線已經構建好,但并不是所有的路徑都是一樣的 ( 有短的、中等的和長的連線,而每個連線都可能具有快、中等或者慢的特性 ) 。

圖 2 :比較傳統和基于圖形的布局。

每個路徑都可能具有多個 “ 抽頭點 ”( 就像高速路的出口道 ) 。這里的問題是,你可能具有一個能迅速地將一個信號從源點函數 ( 高速路的最初的入口道 ) 快速地傳遞到一個目的函數 ( 高速路的最后出口道 ) 的快速路徑。然而,如果我們對一個內部抽頭點增加第二個目的函數,這可能大大地減慢信號速度。

而且,當今 FPGA 的主流架構基于一個查找表 (LUT) 具有幾個輸入和單個輸出的概念。一些 FPGA 架構具有通過與查找表相關的每個輸入輸出路徑的不同延時。然而,更重要的事實是,到 LUT 的每個輸入可能只能使用一部分的不同連線類型。如果來自一個 LUT 的輸出驅動另外一個 LUT ,它們之間可能同時存在慢速和快速的路徑,這取決于我們在接收 LUT 上所使用的特定輸入 。

總的情形被 FPGA 架構的分層特性進一步復雜化。例如,一個小的邏輯模塊可能有幾個 LUT ;在一個較大的邏輯模塊中有幾個這樣的小模塊;在整個的 FPGA 中具有大量的這種大邏輯模塊。在這些大邏輯模塊中的某個邏輯塊中,一個 LUT 的輸出與另外一個 LUT 的輸入直接相連接的概率很小;為了實現額外的連接,可能必須繞道邏輯模塊的外部,然后再繞回到模塊內部來實現。這一點再次地說明所處理問題的復雜性:如果你知道將它們放置在什么地方以及使用哪個引腳,將兩個對象 / 實例放在不同的邏輯模塊將獲得比放在采用非最佳互連資源的同一模塊中會得到更短的延時。

; 另外,任何被提出的綜合方案必須解決圍繞固定的硬宏資源,例如 RAM 、乘法器等相關的連線延時。同樣的,方案必須解決增加的布線擁塞,這種擁塞常出現在靠近這些硬宏的地方。所有這些硬宏都屬于特定器件具有的,因此任何被提出的方案必須能用于每個 FPGA 系列的每個器件。

基于圖形的獨特物理綜合方案

能真正處理 FPGA 架構相關復雜性的具有物理意識的綜合解決方案將以完全不同的觀點來處理上述問題。這種方法將對 FPGA 中所有連線的特點進行描述,包括入口點、端點和內部出口點,然后對所有這些連線構建一個 “ 地圖 ” 。對于軟件行業來說,這種地圖被稱為圖形 (Graph) ;這就是為什么這種方法稱為 “ 基于圖形的物理綜合 ” 的原因。

除了連線本身,這個圖形還包括這些細節:哪個 LUT 引腳連接到哪類的連線;通過每個 LUT 的輸入到輸出的延時差異;以及器件中的任何硬宏的大小和位置。打個比方,這類似于通過查地圖來顯示你將驅車經過的街道、高速路以及像停車場 ( 硬宏 ) 這樣的地方。當希望穿行于城市中的兩個地方時,你將使用地圖來選擇最快的路徑,這個路徑通常并不是最短的點到點路徑。

類似地,基于圖形的物理綜合引擎不是尋找最近的路徑,而是使用一種以互連為中心的方法專注于速度。從最關鍵的路徑開始處理,然后逐步到次關鍵路徑 ( 這樣確保最關健的路徑獲得最快的路線 ) ,基于圖形的物理綜合引擎將選擇連線和它們相關的入口點和出口點;從這些連線得到電路布局;從這些連線和布局得到準確的延時;最后按照要求進行優化和設計反復。

關鍵點是,所有的優化和反復在流程的前端部分 ( 綜合 ) 執行。基于圖形的物理綜合的輸出是一種完整布局的網表 ( 包括將與每個連線相關聯的特定 LUT 引腳 ) ,這種網表可以交給 FPGA 的后端布局布線引擎。

最終得到一種一次通過的、按鍵操作的綜合步驟,下游布局布線引擎不需要 ( 或者需要很少的 ) 設計反復。而且,根據對超過 200 個實際的設計進行分析顯示,就系統的總體時鐘速度而言,基于圖形的物理綜合可以獲得 5% 到 20% 的性能提升。

本文小結

以 ASIC 為中心的具有物理意識的綜合中,連線從布局選擇中衍生出來,與此不同的是,在 FPGA 設計中使用基于圖形的物理綜合時,布局源自于連接線選擇。

對于時序收斂問題,基于已有的 ( 源于 ASIC) 物理綜合引擎可能需要在流程的前端 ( 綜合 ) 與后端 ( 布局布線 ) 之間進行很多次耗時的設計反復。在所有這些反復之后,它們可能依然不能收斂。相比較而言,對于 200 多個采用基于圖形的物理綜合的設計進行分析之后顯示, 90% 的設計處于最后實際時序的 10% 之內, 80% 的設計在實際時序值的 5% 以內,而采用邏輯綜合的設計只有 30% 在實際時序值的 5% 以內,很多設計的誤差很容易地達到 30% ,甚至更高 ) 。而且,基于圖形的物理綜合能提高 5% 到 20% 的總體時鐘速度性能。

此外,基于圖形的物理綜合的已布局網表的質量大大地提高,這意味著時序驅動的布線工具的工作量很少,優化了執行,這樣運行將非常快。

-

FPGA

+關注

關注

1629文章

21754瀏覽量

604231 -

asic

+關注

關注

34文章

1204瀏覽量

120556 -

引擎

+關注

關注

1文章

361瀏覽量

22588

發布評論請先 登錄

相關推薦

將基于圖形的物理綜合添加到FPGA的設計中

將基于圖形的物理綜合添加到FPGA的設計中

評論