引 言

利用現場可編程邏輯器件產生VGA時序信號和彩條圖像信號,并將其作為信號源,應用于電視機或計算機等彩色顯示器的電路開發,方便彩色顯示器驅動控制電路的調試。計算機顯示器的顯示有許多標準,常見的有VGA,SVGA等。在這里嘗試用FPGA實現 VGA圖像顯示控制器,這一過程通過編程實現,之后通過軟件的測試和仿真,當軟件驗證無誤后完成硬件的下載驗證,最終在CRT顯示器上實現輸出,基本原理就是利用FPGA的可編程原理和VGA的時序控制原理,這在產品開發設計中有許多實際應用。

1 VGA顯示原理

VGA(Video Graphics Array)作為一種標準的顯示接口得到了廣泛的應用。VGA在任何時刻都必須工作在某一顯示模式下,其顯示模式分為字符顯示模式和圖形顯示模式,而在應用中討論的都是圖形顯示模式。

VGA的圖形模式分為三類:CGA,EGA兼容的圖形模式;標準VGA圖形模式;VGA擴展圖形模式,后兩種圖形模式統稱為VGA圖形模式。文中基于標準VGA模式來實現。工業標準的VGA顯示模式為:640×480×16×60。

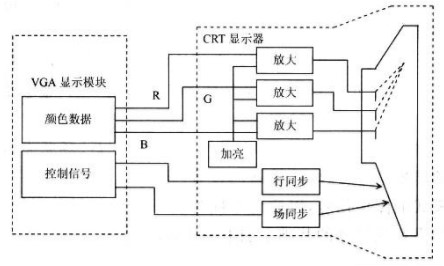

常見的彩色顯示器一般由陰極射線管(CRT)構成,彩色由GRB(Green Red Blue)基色組成。顯示采用逐行掃描的方式解決,陰極射線槍發出電子束打在涂有熒光粉的熒光屏上,產生GRB基色,合成一個彩色像素。掃描從屏幕的左上方開始,從左到右,從上到下,逐行掃描,每掃完一行,電子束回到屏幕的左邊下一行的起始位置,在這期間,CRT、對電子束進行消隱,每行結束時,用行同步信號進行行同步;掃描完所有行,用場同步信號進行場同步,并使掃描回到屏幕的左上方,同時進行場消隱,并預備進行下一次的掃描。VGA顯示控制器控制 CRT顯示圖象的過程如圖1所示。

2 VGA信號時序

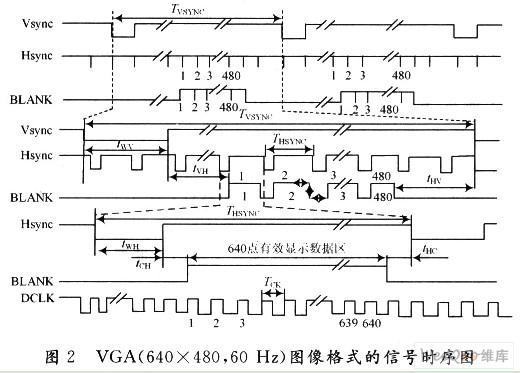

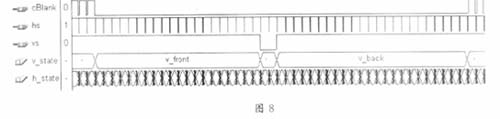

圖2所示是計算機VGA(640×480,60 Hz)圖像格式的信號時序圖。圖2中,V_sync為場同步信號,場周期TVSYNC=16.683 ms,每場有525行,其中480行為有效顯示行,45行為場消隱期。場同步信號Vs中每場有1個脈沖,該脈沖的低電平寬度tWV=63μs(2行)。場消隱期包括場同步時間tWH、場消隱前肩tHV(13行)、場消隱后肩tVH(30行),共45行。行周期THSYNC=31.78μs,每顯示行包括 800點。其中,640點為有效顯示區,160點為行消隱期(非顯示區)。行同步信號Hs中每行有一個脈沖,該脈沖的低電平寬度tWV=3.81 μs(即96個DCK);行消隱期包括行同步時間tWH,行消隱前肩tHC(19個DCLK)和行消隱后肩tCH(45個DCLK),共160個點時鐘。復合消隱信號是行消隱信號和場消隱信號的邏輯與,在有效顯示期復合消隱信號為高電平,在非顯示區域它是低電平。

3 VGA時序信號及彩條信號產生模塊設計

3.1 VGA時序信號產生模塊

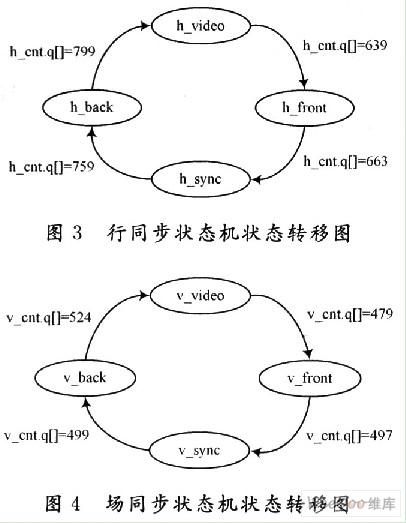

VGA時序信號產生模塊包括行點數計數器h_cnt、場行數計數器v_cnt、行同步產生狀態機h_state和場同步產生狀態機v_state等。其中,行點數計數器是800進制計數器,場行數計數器是525進制計數器。行同步狀態機h_state有h_video,h_front,h_sync, h_back四種狀態,它根據行點數計數器的計數值來進行狀態轉換;場同步狀態機v_state有v_video,v_Front,v_sync, v_Back四種狀態,它根據場行數計數器的計數值來進行狀態翻轉。這兩個狀態機的狀態轉移圖分別如圖3和圖4所示。

當行狀態機h_state復位時,即進入h_video狀態,它對應每行的有效顯示區域。行計數器h_cnt對25 MHz的點時鐘進行計數,當行計數器h_cnt的計數值到達639時,行同步狀態機即進入行消隱前肩h_front狀態;當h_cnt的計數值為663 時,行同步狀態機進入行同步狀態h_sync,此時,行同步信號Hs輸出低電平。當h_cnt的計數值為759時,狀態機即進入行消隱后肩h_back狀態;當行狀態機為h_front,h_sync,h_back狀態時,行消隱信號輸出低電平。當h_cnt的計數值為799時,行同步狀態機進人 h_video狀態,同時,行計數器的同步復位信號為高電平,使行計數器復位。

場狀態機v_state開始時進入v_video狀態,對應每場的有效顯示行,場計數器v_cnt的計數值每行加1。當場計數器的計數值到達479時,場狀態機翻轉,進入場消隱前肩v_ront狀態;當v_cnt的值為497時,狀態機v_state進入場同步狀態v_sync,場同步信號Vs此時輸出低電平;當v_cnt的值為499時,狀態機v_state進入場消隱后肩v_back狀態;當v_cnt的值為524時,狀態機v_state又翻轉進入 v_video狀態,同時輸出高電平到場計數器v_cnt的同步清零端使其清零。當場狀態機v_state的狀態為v_Front,v_sync, v_Back三種狀態時,場消隱信號輸出低電平,其余時刻為高電平。行、場消隱信號的邏輯與即為復合消隱信號。

3.2 VGA彩條信號產生模塊

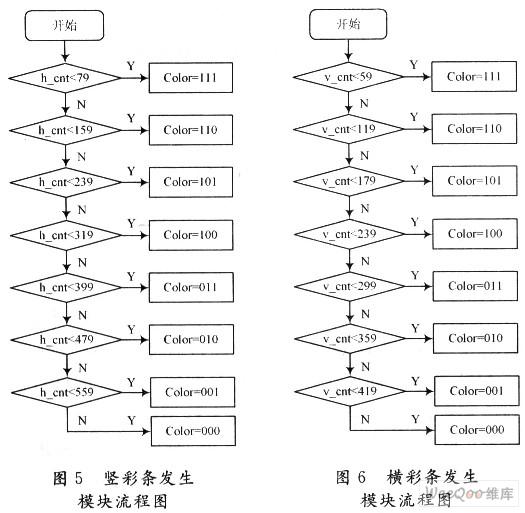

彩條信號產生模塊包括了彩條模式控制、豎彩條發生和橫彩條發生等三個模塊。豎彩條發生模塊根據行點數器h_cnt的計數值來產生彩條,其流程圖如圖5所示。它對行點數計數器的數值進行判斷,每80條豎線生成一種豎彩條,共8種豎彩條橫彩條發生模塊與豎彩條發生模塊相似。它根據場行數計數器v_cnt的計數值來產生橫彩條,流程圖如圖6所示。每60條掃描線為一個彩條寬度,共8種橫彩條模式。計數器mode的值又決定著輸出彩條信號的類型,當mode為0 時,輸出的彩條為豎彩條;當mode為1時,輸出的彩條橫彩條。

3.3 用FPGA下載驗證結果

對上述分析的兩個模塊,已經用QuartusⅡ軟件進行仿真驗證,并得到正確的仿真圖形。通過了軟件的測試,設計進入了最終階段——硬件的調試與通過,本設計采取的是FPGA開發板,圖7就是FPGA開發板的實物圖,將程序寫入PC機經過FPGA芯片在VGA接口處輸出數據,并顯示在CRT顯示器中。圖 8,圖9就是設計出的8種彩色條紋輸出顯示控制器設計的最終輸出結果。

由實驗結果可以看出,該設計可以正確地輸出8種彩色的橫條紋和豎條紋。從而驗證VGA模塊的時序及彩條信號模塊的正確性。

4 結 語

在調試電路時,使用FPGA中多余的邏輯產生VGA信號和彩條信號,所產生的信號穩定可靠,為電路調試帶來了很多方便。

在實際應用中,還可以方便地修改彩條信號產生模塊。比如,可以修改行、場計數器的判斷值,以調整彩條的大小,增加延時跳變的功能,使輸出的彩條信號產生各種變化。此外,與VGA信號類似,改變行、場狀態機的轉換值和行、場計數器的設置,還可以產生其他各種模式的圖像信號,以適應不同分辨率圖像顯示的需要。如果在該設計的基礎上加上采集模塊,就可以顯示希望顯示的圖片。

-

顯示器

+關注

關注

21文章

4980瀏覽量

140020 -

控制器

+關注

關注

112文章

16374瀏覽量

178157 -

可編程邏輯

+關注

關注

7文章

515瀏覽量

44089

發布評論請先 登錄

相關推薦

應用于彩色顯示器的VGA時序信號和彩條圖像信號的設計與實現

應用于彩色顯示器的VGA時序信號和彩條圖像信號的設計與實現

評論