引言

在復(fù)雜的空間環(huán)境中存在各種高能粒子和宇宙射線,星載系統(tǒng)的電子器件容易發(fā)生單粒子翻轉(zhuǎn)等錯(cuò)誤,造成整個(gè)系統(tǒng)的崩潰。對于星載系統(tǒng)而言,可靠性是非常重要的一項(xiàng)性能指標(biāo)。在系統(tǒng)研制時(shí),必須保證系統(tǒng)在局部出現(xiàn)故障時(shí)屏蔽和容忍錯(cuò)誤,把錯(cuò)誤造成的損失降到昀低。比較常用的可靠性措施包括選用抗擾等級高的元器件和適當(dāng)?shù)钠帘卧O(shè)計(jì)等,但是這些措施都無法絕對預(yù)防永久性故障的發(fā)生,為了滿足衛(wèi)星可靠性的要求必須進(jìn)行冗余設(shè)計(jì)。

本文中的設(shè)計(jì)就采用 Flash型 FPGA取代了 SRAM型 FPGA,前者在結(jié)構(gòu)上的特點(diǎn)決定了它不容易發(fā)生單粒子翻轉(zhuǎn)等錯(cuò)誤,從而在固件上提高了可靠性。同時(shí)采用了改進(jìn)型的 TMR冗余設(shè)計(jì),在保障可靠性的同時(shí)也兼顧了實(shí)時(shí)性。

3 基本思想和系統(tǒng)實(shí)現(xiàn)

3.1 Flash型 FPGA概述目前廣泛用于電子產(chǎn)品的 FPGA(Field-Programmable Gate Array,現(xiàn)場可編程門陣列)主要有反熔絲型、SRAM型和 Flash型三種。反熔絲型 FPGA利用熔絲點(diǎn)的通斷來存儲(chǔ)編程信息,只能燒寫一次,可靠性很高,但是同時(shí)開發(fā)成本也很高,一般只在成熟正品中使用。

SRAM型 FPGA使用非常廣泛,它的可編程單元是六管結(jié)構(gòu),編程信息是保存在附加的 PROM里的,每次上電時(shí)從 PROM中加載到 FPGA中,斷電后編程內(nèi)容消失。在航天應(yīng)用中,SRAM型 FPGA昀大的缺點(diǎn)是容易發(fā)生單粒子翻轉(zhuǎn)(Single Event Upset, SEU),以及上電加載過程中容易產(chǎn)生錯(cuò)誤指令。

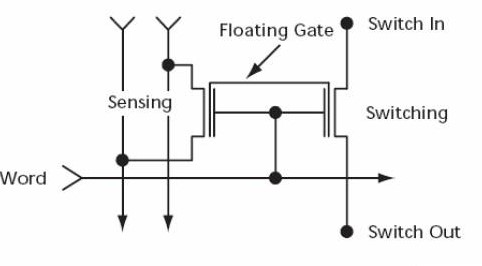

Flash型 FPGA的可編程單元是兩個(gè)三極管組成的 flash開關(guān),其中一個(gè)只在編程時(shí)起傳感器作用,另一個(gè)控制開關(guān)的通斷,兩個(gè)管子共享的浮柵門存儲(chǔ)了編程信息。 Flash型 FPGA無需附加 PROM,上電時(shí)間也很短,另外 flash相比于 SRAM不容易出現(xiàn)單粒子翻轉(zhuǎn),因此 Flash型 FPGA很適合航天應(yīng)用。

本文中的遙控系統(tǒng)采用 Actel公司的 ProASIC plus系列的 APA300芯片。

3.2 系統(tǒng)描述

本文主要實(shí)現(xiàn)了高可靠遙控系統(tǒng)中將地面和星載計(jì)算機(jī)發(fā)送的串行碼字譯碼成對應(yīng)通道指令脈沖的功能,全部功能在一塊 FPGA中實(shí)現(xiàn)。遙控電路板上采用兩塊相同的 FPGA進(jìn)行雙機(jī)熱備份,通過 54LVC244選擇輸出。每塊 FPGA內(nèi)部又采用了下面描述的改進(jìn)型 TMR設(shè)計(jì)。該系統(tǒng)完成了遙控譯碼的功能,各指令響應(yīng)正常。

本文重點(diǎn)介紹 FPGA片內(nèi)的改進(jìn)型 TMR冗余設(shè)計(jì)。

3.3 改進(jìn)型 TMR設(shè)計(jì)

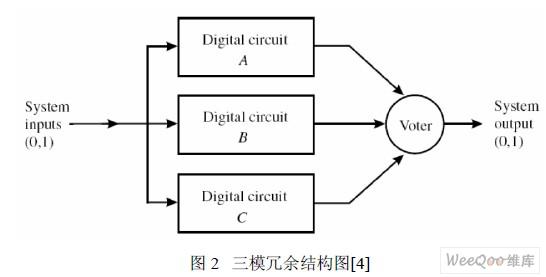

三模冗余(TMR)是一種常用的容錯(cuò)技術(shù),把需要容錯(cuò)的部分復(fù)制三份,然后由表決器根據(jù)多數(shù)表決原則輸出結(jié)果。TMR屬于靜態(tài)冗余技術(shù),它能夠掩蓋 1個(gè)子系統(tǒng)的錯(cuò)誤,而不能修復(fù)錯(cuò)誤。當(dāng) 2個(gè)或 2個(gè)以上的子系統(tǒng)出錯(cuò),或者表決器出錯(cuò)時(shí),TMR系統(tǒng)將輸出錯(cuò)誤的結(jié)果。TMR技術(shù)的優(yōu)點(diǎn)是簡單易行,對于瞬時(shí)出現(xiàn)的錯(cuò)誤具有良好的容錯(cuò)效果,但是代價(jià)是付出了 3倍的面積開銷。

本文設(shè)計(jì)中采用的改進(jìn)型 TMR,實(shí)質(zhì)上是一種 3+n模冗余,N個(gè)子系統(tǒng)中昀多只有三個(gè)子系統(tǒng)同時(shí)處于運(yùn)行狀態(tài),其余的 N-3個(gè)子系統(tǒng)作為備份隊(duì)列,當(dāng)某個(gè)子系統(tǒng)出現(xiàn)錯(cuò)誤時(shí),表決模塊用備份的子系統(tǒng)替換下錯(cuò)誤的子系統(tǒng),繼續(xù)維持 TMR結(jié)構(gòu)。當(dāng)已無備份可用時(shí), 3模冗余系統(tǒng)可以進(jìn)行降級重構(gòu),由 3模冗余降級為 1模。由于延長了三模冗余系統(tǒng)的工作時(shí)間,整個(gè)系統(tǒng)的可靠性得到了很大提高。

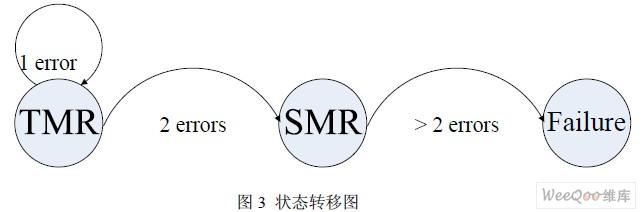

考慮到資源消耗與可靠性提高的平衡,本文設(shè)計(jì)中采用了 3+1模結(jié)構(gòu),也就是 3模冗余, 1模備份。3+1模結(jié)構(gòu)的工作方式為:正常時(shí)進(jìn)行三模冗余表決輸出,出現(xiàn)第 1次永久性故障時(shí)表決處理模塊能夠檢測出錯(cuò)誤,在輸出正常信號的同時(shí)用備用子系統(tǒng)替換故障子系統(tǒng),繼續(xù)維持 TMR結(jié)構(gòu);出現(xiàn)第 2 次永久故障時(shí),表決處理模塊仍然能夠檢測出錯(cuò)誤,在輸出正常信號的同時(shí)切除故障子系統(tǒng),自動(dòng)降級為單模工作直至單模子系統(tǒng)完全損壞。這種 3+1模結(jié)構(gòu)借鑒了軟件容錯(cuò)中的恢復(fù)塊技術(shù)和動(dòng)態(tài)冗余結(jié)構(gòu),能夠容忍至少 2個(gè)子系統(tǒng)錯(cuò)誤。由于 APA300實(shí)現(xiàn)遙控系統(tǒng)資源余量較大,采用了單片 FPGA片內(nèi)冗余的方案,進(jìn)一步簡化了系統(tǒng)的復(fù)雜度。

3+1模結(jié)構(gòu)的狀態(tài)轉(zhuǎn)移圖如下, TMR、SMR和 Failure三個(gè)狀態(tài)分別代表三模冗余、單模工作和系統(tǒng)失效。

在設(shè)計(jì)中,通過冗余單元的互鎖機(jī)制(Inter-Lock, IL)來防止錯(cuò)誤數(shù)據(jù)通過冗余單元邊界傳播,為此采用了分區(qū)約束的方法進(jìn)行布局布線設(shè)計(jì)。分區(qū)設(shè)計(jì)不僅能夠隔離錯(cuò)誤,而且可以充分利用 APA300的 Spine分布,減少路徑延遲。

在用戶約束文件 GCF文件中作如下約束:

這四條語句把 U1~U4四個(gè)子系統(tǒng)分別限制在一個(gè) spine內(nèi),除了全局時(shí)鐘線和輸入輸出線以外,子系統(tǒng)之間沒有直接的連接,這樣分區(qū)布局布線以后就能夠有效地隔離錯(cuò)誤。

在保證可靠性的同時(shí),3+1模設(shè)計(jì)昀大程度的保證了輸出的實(shí)時(shí)性,不需要經(jīng)過關(guān)機(jī)等待周期、重發(fā)指令周期或者輸出不確定周期,能夠連續(xù)輸出正確結(jié)果直到系統(tǒng)完全倒向錯(cuò)誤狀態(tài)。為了避免系統(tǒng)重構(gòu)時(shí)過快降級,考慮到很多錯(cuò)誤是瞬時(shí)出現(xiàn)又隨即恢復(fù)的軟錯(cuò)誤,因此設(shè)定錯(cuò)誤出現(xiàn)一定次數(shù)(例如 3次)以后才去掉故障模塊。

對于 3+1模結(jié)構(gòu),可靠性提高的代價(jià)是付出了 4倍的資源開銷,另外輸出時(shí)間延遲會(huì)略有增加,因?yàn)殛P(guān)鍵路徑上的表決器增加了判斷、替換的邏輯單元。因此這種結(jié)構(gòu)只適用于資源充裕、系統(tǒng)頻率不高的場合。在空間應(yīng)用系統(tǒng)中,工作速度往往不是昀重要的,因而 3+1模結(jié)構(gòu)實(shí)質(zhì)上是用速度換面積(可靠性),在資源不足的情況下可以只對關(guān)鍵模塊、錯(cuò)誤敏感率高的模塊進(jìn)行冗余,以節(jié)省資源。

4 系統(tǒng)可靠性分析

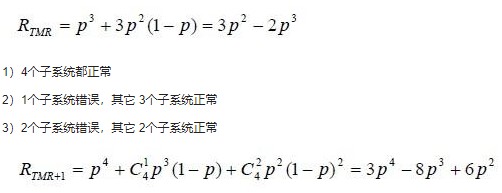

假設(shè)單機(jī)的可靠性為(運(yùn)行 5年后) , 普通 TMR和本文中改進(jìn)型 TMR的可靠性分別為。由于 2個(gè)以上子系統(tǒng)同時(shí)發(fā)生錯(cuò)誤的概率很小,假定同一時(shí)刻昀多只有一個(gè)子系統(tǒng)發(fā)生錯(cuò)誤。

TMR可以容忍 1個(gè)子系統(tǒng)錯(cuò)誤,可靠性相當(dāng)于 3個(gè)子系統(tǒng)都正常的可靠性加上某一個(gè)子系統(tǒng)錯(cuò)誤、其它兩個(gè)子系統(tǒng)正常的可靠性:

同理,改進(jìn)型 TMR的可靠性相當(dāng)于以下三種情況的可靠性之和:

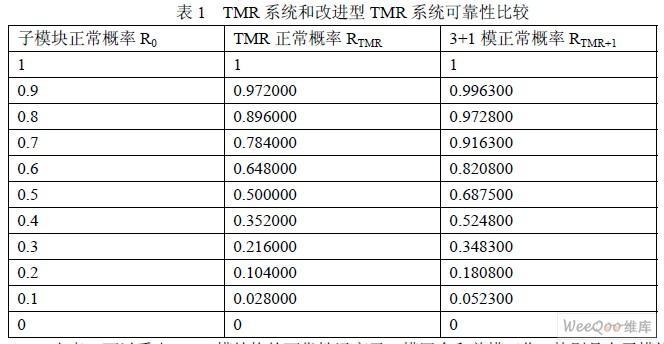

取一系列的 R0值(0≤R0≤1),按(1)(2)兩式計(jì)算出 RTMR和 RTMR+1如下表 1:

由表 1可以看出, 3+1模結(jié)構(gòu)的可靠性遠(yuǎn)高于 3模冗余和單模工作,特別是在子模塊可靠性降低的情況下提高可靠性的效果更為顯著。

5 結(jié)論

本文提出了一種基于 Flash型 FPGA的高可靠系統(tǒng)解決方案,改進(jìn)型的 TMR冗余利用片內(nèi)備份的子系統(tǒng)替換出錯(cuò)的系統(tǒng),能夠長期維持 TMR系統(tǒng),有效地提高可靠性。本文所述思想同樣適用于多芯片 /多機(jī)情況下的冗余方案。本系統(tǒng)即將應(yīng)用于某航天型號設(shè)備中,經(jīng)過初步聯(lián)試證明本系統(tǒng)能夠滿足可靠性和性能的要求。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21769瀏覽量

604651 -

芯片

+關(guān)注

關(guān)注

456文章

51019瀏覽量

425409 -

FlaSh

+關(guān)注

關(guān)注

10文章

1640瀏覽量

148298

發(fā)布評論請先 登錄

相關(guān)推薦

基于FPGA的SPI Flash控制器的設(shè)計(jì)方案

基于FPGA的SPI Flash控制器的設(shè)計(jì)方案

一種基于雙MCU的安全光幕軟硬件設(shè)計(jì)方案介紹

一種基于FPGA和DSP的高速數(shù)據(jù)采集設(shè)計(jì)方案介紹

分享一種基于Actel Flash FPGA的高可靠設(shè)計(jì)方案

分享一款不錯(cuò)的采用FPGA的集群通信移動(dòng)終端設(shè)計(jì)方案

基于cyclone EP1C6的LED 屏設(shè)計(jì)方案

一種基于Flash型FPGA的高可靠系統(tǒng)設(shè)計(jì)

NAND Flash的驅(qū)動(dòng)程序設(shè)計(jì)方案

采用FPGA技術(shù)的智能導(dǎo)盲犬設(shè)計(jì)方案

采用VC++程序的FPGA重配置設(shè)計(jì)方案

多種EDA工具的FPGA設(shè)計(jì)方案

基于eMMC芯片技術(shù)特點(diǎn)工作原理以及控制器的設(shè)計(jì)方案

Virtex-6FPGA的eMMC控制器設(shè)計(jì)資料

基于FPGA的SPI Flash控制器的設(shè)計(jì)方案

采用Flash FPGA芯片的高可靠設(shè)計(jì)方案介紹

采用Flash FPGA芯片的高可靠設(shè)計(jì)方案介紹

評論