1.引言

為了提高傳輸速率,擴大通信容量,減少信道數量,通常把多路信號復用成一路信號進行傳輸。在多種復用方式中,時分復用是一種常用的方式。時分復用是多路信號按照時間間隔共享一路信道進行傳輸。復接是把多路速率相對較低的數字信號通過某種協議復合成一路信號進行傳輸;而分接正好相反,是把一路速率相比高的信號按照對應的協議分割成發送端對應的速率相對較低的信號。為了規范復接與分接協議,ITU(國際電信聯盟)根據傳輸速率的不同等級,將復接的數字信號為基群、二次群、三次群、四次群等,以我國實際應用為例,速率分別:2.048MHz、8.4.48MHz、34.368MHz、139.264MHz。本文介紹基于FPGA實現二次群數字信號的分接部分的功能,包括幀頭捕獲、幀丟失告警、基群信號提取,去除插入碼、負碼速調整等二次群分接的關鍵技術。

2.二次群幀結構介紹

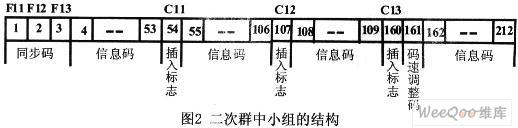

二次群幀結構如圖1所示,幀長為848bit,復幀包含的比特內容如下:

(1)幀定位10bit,表示為F11F12~F13F23,碼型為1111010000;

(2) 公務2bit,其中1bit(11位)用來向對端發出告警指示;另外1bit(12位)留作國內使用;

(3)支路信息820bit,第1組為200bit(13~212),第Ⅱ組為208bit(217~424),第Ⅲ組為208bit(429~636),第Ⅳ組為204bit(645~848);

(4) 碼速調整4bit,表示為V1,V2,V3,V4(641~*位),各基群1bit,共4bit;

(5)插入標志12bit,以C表示,填充脈沖4bit。為了使接收端能知道是否有插入及插在何處,在復接端發出插入指令的同時需要發出插入標志信號,以告知分接器有插入。目前常用的辦法是定位插入。在這里規定:第1基群第1位插入標志C11在213位插入,第1基群第2位插入標志C12在425位插入,第1基群第3位插入標志C13在637位插入。由此可知:

C11C21C31C41是第1位插入標志;

C12C22C32C42是第2位插入標志;

C13C23C33C43是第3位插入標志;

插入標志信號是3位,采用3位碼來組成插入標志信號,可提高標志信號的可靠性。用"111"表示有插入,用"000"表示無插入。當C11C12C13為"111"時,表示在641時隙的脈沖是插入脈沖;當C11C12C13為"000"時,表示在641時隙的脈沖是信息碼。

一幀分為4組,每組為212bit,這212bit的分配如圖2所示,4個基群相似,以第1基群為例。將212bit分為4組,每組53bit。第1組的1,2,3三個碼位,供插入復接器幀同步碼用,以F表示;然后是50bit的信息碼;Ⅱ,Ⅲ,Ⅳ組的第1位碼用作標志信號,用C表示;第Ⅳ組的第2個碼位就是碼速調整的碼位,用V表示,需要插入時,就在這個位置上插入一個不帶信息的脈沖,不必插入時,這個碼位仍傳信息碼;Ⅱ、Ⅲ、Ⅳ組的其他位置都是信息碼。4個基群的第1~3個碼位復接在一起,共12位,其中前10位作為復接器的幀同步碼,第12位為告警指示,第12位作為備用。4個基群的插入標志信號碼和碼速調整比特,復接后又分別連在一起。

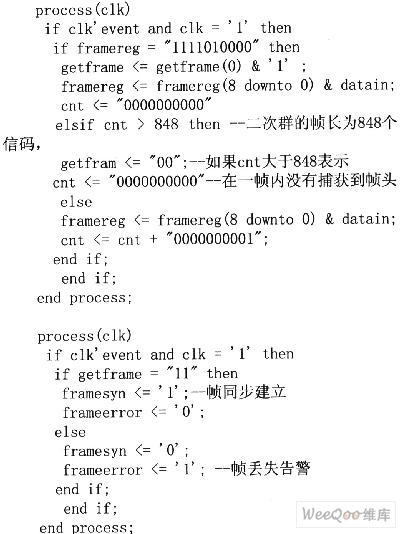

3.二次群幀頭捕獲及幀丟失告警

根據上面二次群幀結構的分析,二次群的幀頭信碼為:”1111010000“10個bit,在FPGA中,定義一個10位的寄存器,二次群信碼從右向左進入10位寄存器,如果10位寄存器的值連續兩次為:”1111010000"則表示幀頭捕獲成功,幀同步建立。同樣如何連續兩個二次群幀時間長度內沒有捕獲到幀頭信碼,則表示幀丟失,產生幀丟失告警。VHDL語言代碼實現如下程序段:

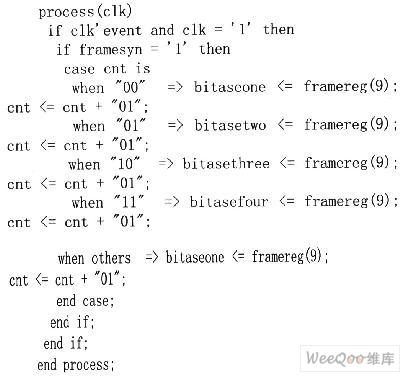

4.基群信號提取

一個二次群信號復接了四個基群信號,基群信號提取是在二次群幀同步的狀態下把二次群信號按一分四的規則進行串并轉化。因為二次的復接是按bit復接,所以二次群一幀中第一位為第一個群的第一位,二次群一幀中第二位為第二個群的第一位,以此類推。VHDL語言代碼實現如下程序段:

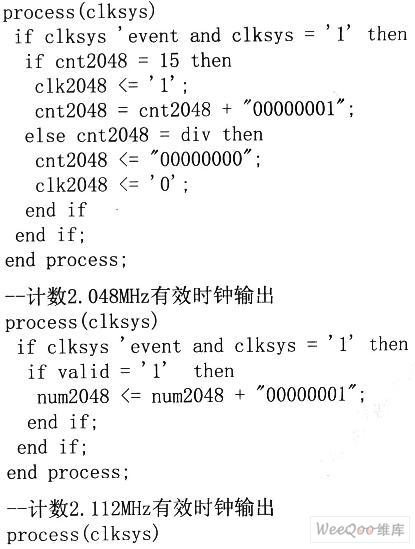

5.去除插入碼及負碼速調整

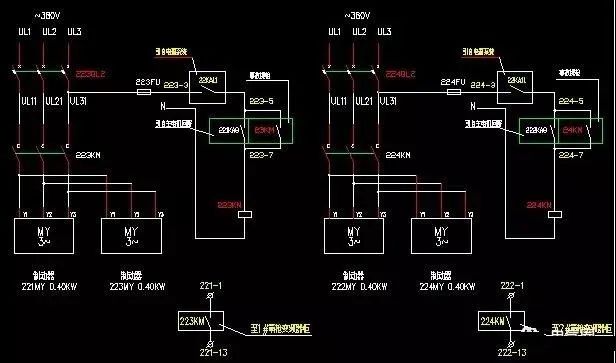

去除插入碼及負碼速調整是二次群的關鍵部分,首先要去除幀頭插入的F1、F2和F3;接著去除C1、C25DC3;最后根據C1、C2和C3值來判斷第161位V否為插入碼,如果C1C2C3為:"1 11",則V是插入碼應去除,如果C1C2C3為:"000",則V是基群的信碼,不應去除。把去除了插入碼的信號輸入到一個FIFO,用經過負碼速調整過的2.048MHz時鐘讀出輸出基群信號如圖3所示。

由于寫到FIF0的時鐘是不均勻的,不利于后端處理,所以必須做負碼速調整,即把2.112MHz速率調整到2.048MHz速率。FPGA實現的原理是根據2.112MHz速率和2.048MHz速率的有效信碼個數是一樣多的,可以根據它們的個數進行調整。如果根據2.048MHz速率輸出的信碼少了則稍微提高2.048MH z時鐘的頻率,如果根據2.048MHz速率輸出的信碼多了則稍微降低2.048MHz時鐘的頻率。

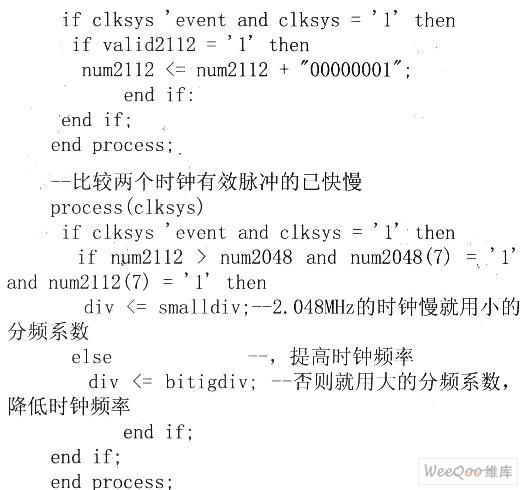

VHDL語言代碼實現如下程序段:一根據div的值動態調整clk2048的頻率,實現負碼速調整

6.結論

本文對二次群的分接處理,提出了一種基于FPGA的方案,介紹了二次群的幀結構,給出了幀頭捕獲、幀丟失告警、負碼速調整等VHDL語言的關鍵程序。在QUARTUSII軟件中編譯完成,資源僅占用三十多個LE,給二次群設備的設計提供了一種參考,具有很高的應用價值。

-

FPGA

+關注

關注

1629文章

21753瀏覽量

604198 -

寄存器

+關注

關注

31文章

5357瀏覽量

120619 -

vhdl

+關注

關注

30文章

817瀏覽量

128169

發布評論請先 登錄

相關推薦

航管二次雷達射頻切換單元FPGA實現

基于EPLD的單脈沖二次雷達應答處理器設計與實現

二次電池是什么_二次電池有哪些_二次電池充放電方程式

變壓器二次側能接地嗎

基于CPLD技術實現PDH通信二次群復接器的設計及應用優勢

電流互感器二次開路處理及二次開路的要素

二次供水設備遠程監控解決方案

基于FPGA實現二次群的分接處理方案

基于FPGA實現二次群的分接處理方案

評論