1 引言

在時分制數字通信系統中,為了擴大傳輸容量和提高傳輸效率,常常利用復接技術將 若干個低速數字信號合并成一個高速數字信號流,以便在高速寬帶信道中傳輸。數字復接 器是把兩個或兩個以上的支路,按時分復用方式合并成一個單一的高次群數字信號設備, 其中包含碼速調整結構。

碼速調整就是把速率不同的各支路信號,調整成與復接設備定時 完全同步的數字信號,以便由復接單元把各個支路信號復接成一個數字流。 碼速調整可以分為正碼速調整、正/負碼速調整和正/零/負碼速調整三種。本文通過 改進了異步FIFO 設計,基于FPGA 提出了一種正碼速調整的設計方案, 通過正碼速調整, 使輸入碼率為1200bps,輸出碼率為1350bps。

2 正碼速調整的基本原理

2.1 正碼速調整的幀結構

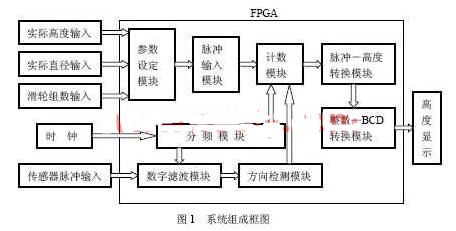

根據設計方案,采用正碼速調整的幀結構有32bit,分為四組,每組8bit。正碼速調 整的幀結構如圖1 所示。

圖1 正碼速調整的幀結構

第一組8bit 信息,第二、三、四組中的第一個比特C1、C2、C3 為碼速調整標志比特。 第四組中第26 bit V 為碼速調整插入比特,其作用是調整基群碼速,使其瞬時碼率保持一 致并和復接器主時鐘相適應。具體調整方法是:在第一組結束時刻進行是否需要調整判決, 若需要進行調整,則在V 位置插入調整比特;若不需要調整,則V 位置傳輸信息比特。為了區分V 位置是插入調整比特還是傳輸信息比特,用碼速調整標志比特C1、C2、C3 來標 志。若V 位置插入調整比特,則在C1、C2、C3 位置插入3 個“1”;若V 位置傳輸信息比 特,則在C1、C2、C3 位置插入3 個“0”。

2.2 正碼速調整系統的構成

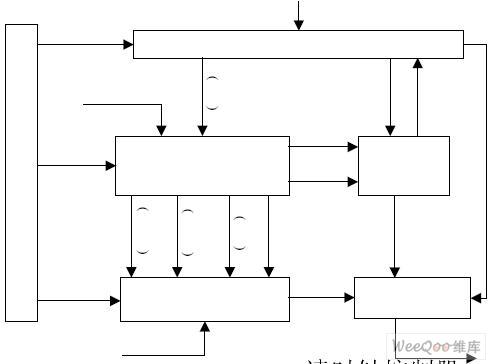

在本方案設計中,采用格雷碼對地址編碼的異步FIFO 設計,使其滿足正碼速調整需 要,同時給出了適合格雷碼的幀結構。正碼速調整系統的構成如圖2 所示。

圖2 正碼速調整系統的構成框圖

正碼速調整單元主要分為3 個模塊:“讀時鐘、調整、輔助信號發生器”、“異步FIFO 模塊”和“調整信號插入”。其中異步FIFO 模塊部分包含“地址發生器”、“相位比較器” 和“雙口RAM”。

首先將寫時鐘以及“整體信號控制器”產生的寫時鐘控制信號送入到“地址發生器”, “地址發生器”通過寫時鐘上升沿產生的寫地址(格雷碼)和寫時鐘一同送入到“雙口 RAM”,將寫地址(自然碼)送入到“相位比較器”。同時未經調整的數據流以及“整體信 號控制器”產生的寫使能信號也送入到“雙口RAM”。為了準確的將數據寫入到雙口RAM 中,以寫時鐘的下降沿將數據寫入到RAM 中。

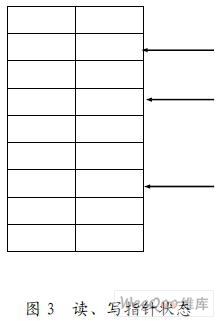

然后當寫時鐘寫到地址“101”時,“整體信號控制器”才將讀時鐘控制信號送入到“讀 時鐘、調整、輔助信號發生器”,其結合送入的均勻時鐘(1350HZ)產生扣除調整標志位 的非均勻讀時鐘送入到“地址發生器”,同時將控制狀態位的輔助信號送入到“相位比較 器”,將調整信號送入到“調整信號插入”。扣除的讀時鐘通過“地址發生器”將讀地址(自 然碼)送入到“相位比較器”,將讀地址(格雷碼)和扣除讀時鐘送入到“雙口RAM”。 此時RAM 通過讀時鐘上升沿依次從地址“000”開始讀取數據。原理圖如圖3 所示。

隨著時間的推移,讀指針與寫指針之間的距離逐漸變小,當相位比較器計算出讀、寫 地址差值小于門限值“100”時,則在圖3 中第8 個比特位置給出高電平的存儲狀態位告 知系統緩存器即將取空,然后在第32 個比特位置將存儲狀態位再次置“0”,等待下一次 的狀態判斷。

最后,“調整信號插入”根據存儲狀態位的電平決定數據流中的調整位是插入3 個“1”還是3 個“0”。

3 正碼速調整的FPGA設計

3.1 讀時鐘、調整、輔助信號發生器模塊

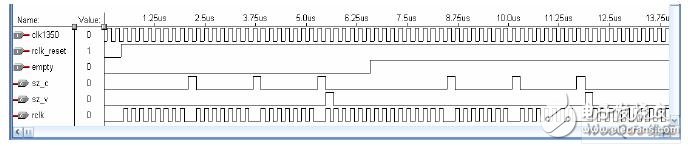

該模塊的主要作用在于根據存儲狀態來生成扣除調整位的缺口讀時鐘,同時產生調整 信號以及相關輔助信號。

扣除前讀時鐘首先通過32 位計數器,當讀時鐘控制開啟時,計數器開始計數。在第9, 17,25 個比特位時置調整標志位高電平;在第26 個比特位置調整位高電平;在第8 個比 特和第32 個比特位上輔助信號分別顯示“00111”和“11111”計數值。

當存儲狀態位為“1”時表示存儲器即將取空,第26 比特處的讀時鐘脈沖扣除,不傳 信碼,其邏輯門的關系如下: r_clk<=(rclk_reset and(clk1350 and (not sz_c))and ((not empty)or(not sz_v))); 其中,r_clk 為扣除后讀時鐘,rclk_reset 為讀時鐘控制,clk1350 為讀時鐘1350HZ,sz_c 為調整標志位,sz_v 為調整位,empty 為存儲狀態位。 具體仿真波形見圖4 所示。

圖4 讀時鐘、調整、輔助信號發生器仿真圖

3.2 異步FIFO 設計

此部分為本文的關鍵部分,FIFO 設計的好壞直接影響系統性能。

(1)地址發生器模塊

該模塊主要功能在于根據讀、寫時鐘以及時鐘控制信號生成相應的讀、寫地址的自然 碼和格雷碼。由于讀地址要在寫地址寫到“101”時才開始從地址“000”讀取數據,因此讀時鐘控制信號是由寫時鐘控制信號延遲5 個寫時鐘周期產生的。

(2)相位比較器模塊

根據由“讀時鐘、調整、輔助信號發生器模塊”中產生的輔助信號在每幀的第8 比特 位置上判斷存儲狀態是否為“空”,若為“空”則在第8 比特位上置存儲狀態位高電平, 然后再次根據輔助信號在第32 比特位置上將狀態輔助位置回初始狀態―低電平。

判決器主要是在輔助信號值為“00111”時,判斷差值是否小于設置的門限“100”,若 小于“100”則存儲狀態置“1”,然后在輔助信號為“11111”時將存儲狀態置“0”;若大 于“100”,存儲狀態維持初始狀態“0”。

(3)雙口RAM 模塊

RAM需要大量的存儲空間,若直接用數組的形式來描述RAM 時,資源利用率相當低。 因此本文選取IP 核來定制RAM,直接生成寬度為1,深度為8 的帶寫使能的雙口RAM, 寫時鐘為下降沿有效,讀時鐘為上升沿有效,寫使能為高電平有效。

3.3 調整信號插入模塊

該模塊主要作用就是將扣除調整位后的數據流根據存儲狀態位在調整標志位插入 “000”或“111”。若插入的是“000”,則在第26 比特傳信碼,若插入的是“111”,則在 第26 比特傳“1”。其邏輯關系為:

if empty= '1' then

dout<=(din or (sv or sc));

elsif empty= '0' then

dout<=((not sc) and din);

end if;

其中,din 為扣除調整位后的數據,dout 為正碼速調整后的數據,由于插入后存在毛刺,于是在其后端加了個D 觸發器去除了毛刺。

4 整體仿真結果

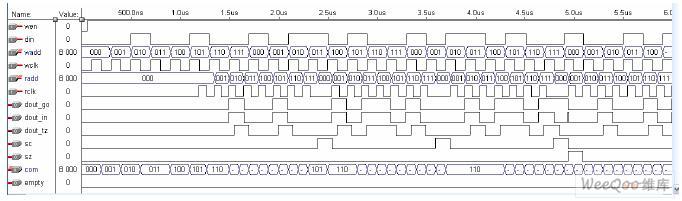

最后在MAXPLUS II 開發平臺上采用原理圖輸入方式,根據同步單元各個功能模塊的劃 分,將各個功能模塊連接起來,編譯成功,其整體仿真如圖5 所示。

圖5 整體仿真圖

其中 dout_go 表示扣除調整位置后的數據流,dout_in 表插入調整信號后的數據流, dout_tz 表示加了D 觸發器的調整數據流。由圖可知,當wen 為高電平時,開始寫入數據 “00100100”到寫地址wadd,當寫到地址“101”時,讀時鐘開始工作,依次從地址“000” 開始從RAM 中讀取數據。當到第8 比特位置時,由于地址差值為“101”未到達門限,因 此存儲狀態位empty 仍舊為“0”表示不需要調整,則在幀的調整標志位置上插入3 個“0”, 調整位繼續傳信碼。在dout_go 上最后一個調整標志位由于插入了“0”,可以清晰的看到由此帶來的毛刺,但加了D 觸發器后的dout_tz 已成功的消除了這個毛刺。

5 結論

系統仿真波形良好,能準確實現正碼速調整,本系統采用芯片EP1K100Q208 實現。通 過正碼速調整,可以把調整后的數字信號進行復接,擴大了傳輸容量,提高了傳輸效率。

-

FPGA

+關注

關注

1630文章

21769瀏覽量

604656 -

芯片

+關注

關注

456文章

51019瀏覽量

425416 -

寬帶

+關注

關注

4文章

992瀏覽量

60399

發布評論請先 登錄

相關推薦

基于EP1C6Q240C8的FPGA芯片實現電子測試系統的設計

EP2C8Q208C JTAG下載的奇怪現象,大家討論下

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8這三種芯片的區別

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8這三種芯片的區別

想要EP2C5Q208C8芯片的中文資料,特別是引腳的對應表!十分...

發現EP1K100QI208-2 IC的VCC和GND引腳之間頻繁短路

回收EP2C8Q208C8N,收購EP2C8Q208C8N

EP2C8Q208C8芯片時鐘主頻由50MHz生成400Hz有何作用

EP2C6Q208+AMD29LV160+HY57V6416

基于FPGA的手持式數字存儲示波器顯示驅動設計

STEVAL-MKI208V1K STMicroelectronics STEVALMKI208V1Ki Nemo慣性模塊套件

基于FPGA和EP1K100Q208芯片的正碼速調整的設計

基于FPGA和EP1K100Q208芯片的正碼速調整的設計

評論