1 DCI技術概述

隨著FPGA芯片越大而且系統時鐘越高,PCB板設計以及結構設計變得越難,隨著速率的提高,板間的信號完整性變的非常關鍵,PCB板上若有關鍵信號,那么需要進行阻抗匹配,從而避免信號的反射和震蕩。Xilinx公司提供DCI可以在芯片內部進行阻抗匹配,匹配電阻更加接進芯片,可以減少元器件,節省PDB板面積,并且也更方便走線。

傳統的阻抗匹配是在PCB板上端接一個電阻。理想情況下,源端輸出阻抗認為是很小的,而接受端的輸入阻抗認為是很大,在實際電路中都可以不去考慮,只考慮PCB上的走線,從接收端看過去PCB特征阻抗應該等于端接電阻,這樣電流從源端流向接收端才不會導致反射。

1.1 阻抗匹配原理

阻抗匹配是指負載阻抗與激勵源內部阻抗互相適配,得到最大功率輸出的一種工作狀態。對于不同特性的電路,匹配條件是不一樣的。在純電阻電路中,當負載電阻等于激勵源內阻時,則輸出功率為最大,這種工作狀態稱為匹配,否則稱為失配。當激勵源內阻抗和負載阻抗含有電抗成份時,為使負載得到最大功率,負載阻抗與內阻必須滿足共扼關系,即電阻成份相等,電抗成份只數值相等而符號相反。這種匹配條件稱為共扼匹配。

在高速的設計中,阻抗的匹配與否關系到信號的質量優劣。阻抗匹配的技術可以說是豐富多樣,但是在具體的系統中怎樣才能比較合理的應用,需要衡量多個方面的因素。例如我們在系統中設計中,很多采用的都是源段的串連匹配。對于什么情況下需要匹配,采用什么方式的匹配,為什么采用這種方式。例如:差分的匹配多數采用并聯終端匹配;時鐘采用串聯源端匹配。

1.2 串聯源端匹配

串聯源端匹配的理論出發點是在信號源端阻抗低于傳輸線特征阻抗的條件下,在信號的源端和傳輸線之間串接一個電阻R,使源端的輸出阻抗與傳輸線的特征阻抗相匹配,抑制從負載端反射回來的信號發生再次反射。

1.2.2 串聯終端匹配后的信號傳輸具有以下特點:

1、由于串聯匹配電阻的作用,驅動信號傳播時以其幅度的50%向負載端傳播。

2、信號在負載端的反射系數接近+1,因此反射信號的幅度接近原始信號幅度的50%.

3、反射信號與源端傳播的信號疊加,使負載端接受到的信號與原始信號的幅度近似相同。

4、負載端反射信號向源端傳播,到達源端后被匹配電阻吸收。

5、反射信號到達源端后,源端驅動電流降為0,直到下一次信號傳輸。

相對串聯匹配來說,不要求信號驅動器具有很大的電流驅動能力。選擇串聯源端匹配電阻值的原則很簡單,就是要求匹配電阻值與驅動器的輸出阻抗之和與傳輸線的特征阻抗相等。理想的信號驅動器的輸出阻抗為零,實際的驅動器總是有比較小的輸出阻抗,而且在信號的電平發生變化時,輸出阻抗可能不同。比如電源電壓為+4.5V的CMOS驅動器,在低電平時典型的輸出阻抗為37Ω,在高電平時典型的輸出阻抗為45Ω[4];TTL驅動器和CMOS驅動一樣,其輸出阻抗會隨信號的電平大小變化而變化。因此,對TTL或CMOS電路來說,不可能有十分正確的匹配電阻,只能折中考慮。鏈狀拓撲結構的信號網路不適合使用串聯終端匹配,所有的負載必須接到傳輸線的末端。可以看出,有一段時間負載端信號幅度為原始信號幅度的一半。顯然這時候信號處在不定邏輯狀態,信號的噪聲容限很低。

串聯匹配是最常用的終端匹配方法。它的優點是功耗小,不會給驅動器帶來額外的直流負載,也不會在信號和地之間引入額外的阻抗;而且只需要一個電阻元件。

1.3 并聯終端匹配

并聯終端匹配的理論出發點是在信號源端阻抗很小的情況下,通過增加并聯電阻使負載端輸入阻抗與傳輸線的特征阻抗相匹配,達到消除負載端反射的目的。實現形式分為單電阻和雙電阻兩種形式。

1.3.3 并聯終端匹配后的信號傳輸具有以下特點:

1、 驅動信號近似以滿幅度沿傳輸線傳播;

2、 所有的反射都被匹配電阻吸收;

3、 負載端接受到的信號幅度與源端發送的信號幅度近似相同。

在實際的電路系統中,芯片的輸入阻抗很高,因此對單電阻形式來說,負載端的并聯電阻值必須與傳輸線的特征阻抗相近或相等。假定傳輸線的特征阻抗為50Ω,則 R值為50Ω。如果信號的高電平為5V,則信號的靜態電流將達到100mA.由于典型的TTL或CMOS電路的驅動能力很小,這種單電阻的并聯匹配方式很少出現在這些電路中。

雙電阻形式的并聯匹配,也被稱作戴維南終端匹配,要求的電流驅動能力比單電阻形式小。這是因為兩電阻的并聯值與傳輸線的特征阻抗相匹配,每個電阻都比傳輸線的特征阻抗大。考慮到芯片的驅動能力,兩個電阻值的選擇必須遵循三個原則:

⑴兩電阻的并聯值與傳輸線的特征阻抗相等;

⑵與電源連接的電阻值不能太小,以免信號為低電平時驅動電流過大;

⑶與地連接的電阻值不能太小,以免信號為高電平時驅動電流過大。

傳統的終端匹配要求電阻盡量靠近芯片管腳,不但增加了PCB的布線的難度,而且還增加了元器件的數量。

2 DCI技術的應用分析

根據I/O的電平標準,DCI技術可以控制驅動器的輸出阻抗,也可以在驅動器或者接收器上添加并行終端。目的都是精確的匹配傳輸線上的特征阻抗。DCI技術根據VRP和VRN上的高精度參考電阻計算I/O內部的阻抗。并且可以持續補償因為溫度和電壓變化引起的阻抗變化。

對于阻抗控制驅動器,DCI使阻抗匹配外部的兩個參考電阻,或者匹配這兩個參考電阻的一半。

對于并行終端,包括發送器和接收器,DCI技術讓終端電阻更加接近輸出驅動器或者輸入buffer. 對于7系列FPGA,DCI技術只用在HP I/O bank,對HR I/O bank 并不適用。Xilinx DCI使用兩個復用管腳來調整驅動器的阻抗或者并聯終端電阻。這兩個管腳分別是VRN 和VRP.VRN必須通過一個參考電阻Rref上拉到VCCO,而VRP則必須通過一個參考電阻Rref下拉到地。這個Rref的阻值一般等于PCB走線的特征阻抗或者是這個阻抗的2倍。

2.1 要在設計中使用DCI技術,需要滿足以下條件:

(1)該信號管腳是在HP I/O BANK,并且在約束中聲明該管腳的標準是帶有DCI的。

(2)在VRN上接一個高精度的參考電阻上拉到Vcco.

(3)在VRP上接一個高精度的參考電阻下拉到地。

(4)VRN和VRP都在同一個HP BANK,除非使用了DCI疊代,DCI迭代只需要HP master BANK的。

DCI計算可以通過DCIRESET原語進行復位。通過發送RST高脈沖給DCIRESET,DCI開始計算阻抗值并且此時所有使用了DCI的I/O都不工作,直到LOCKED信號拉高為止。

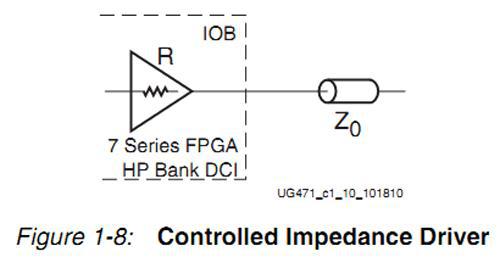

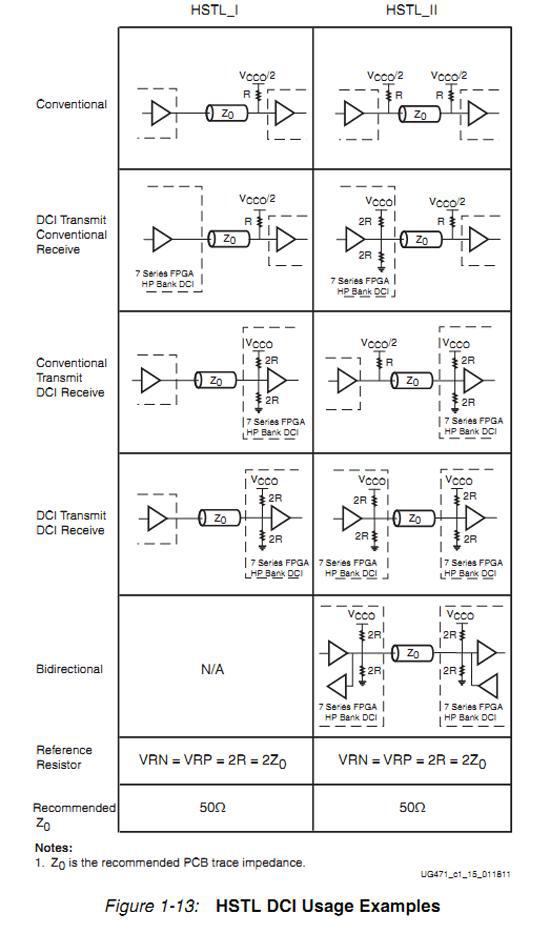

2.2 阻抗控制驅動器

對于阻抗控制驅動器,DCI提供兩種阻抗匹配類型:

1、和參考電阻相等

2、等于參考電阻的一半

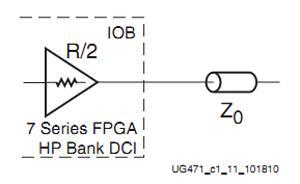

這種的話,R必須等于2Z0,電平標準要選擇DCI_DV2,如LVDCI_DV2_15、LVDCI_DV2_18的原語,使用這種方式主要是為了降低靜態功耗。

2.3 并聯終端(分立電阻)

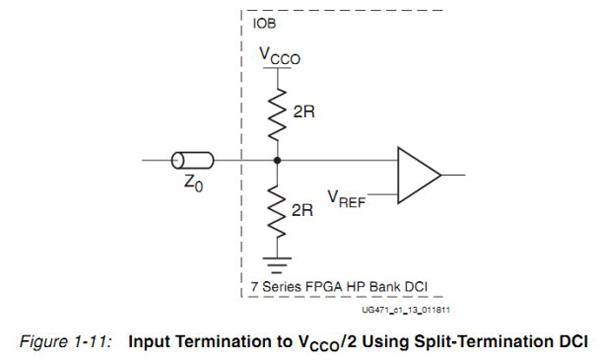

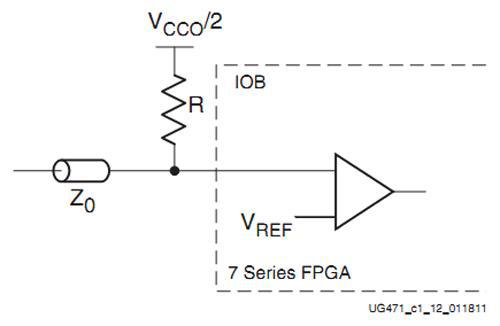

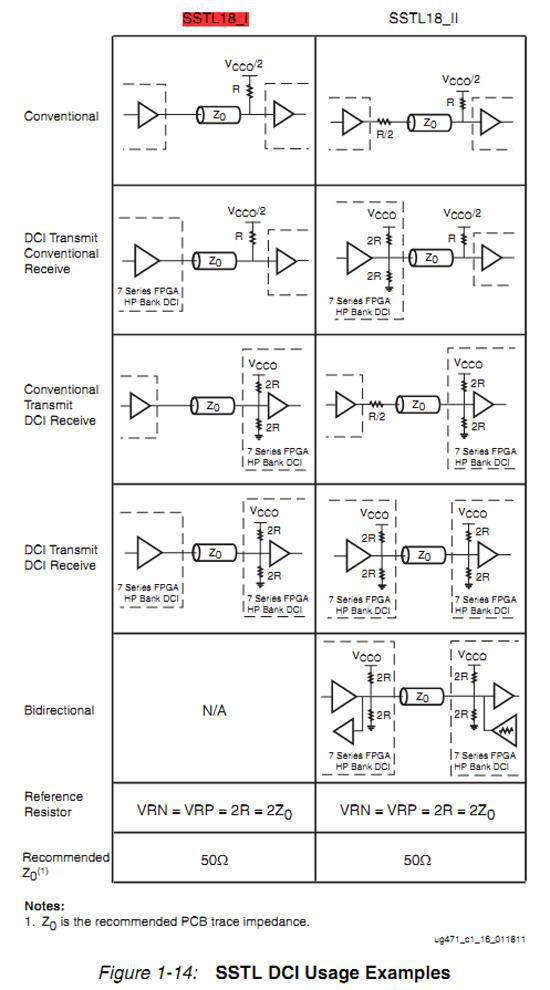

對于并聯終端,DCI使用一種戴維南等效電路或者分立電阻,使用Vcco/2的電平。

其戴維南等效電路是如下圖:

適合于分立電阻的DCI電平標準如下表:

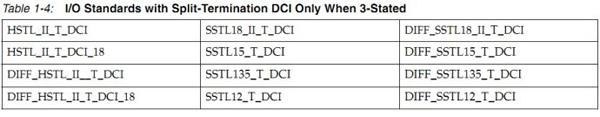

3 三態DCI分析

對于有些電平標準,如SSTL和HSTL的一級標準僅僅支持單向信號,而二級標準既支持單向也支持雙向信號,當分立終端在使用時,DCI只控制分立終端的阻抗而不是驅動器的阻抗,所以對于雙向信號來說,當它作為驅動器時,需要關閉分立終端的應用。XILINX提供了一個DCI-T的標準來滿足這一要求,只需要將相應的電平標準改成這種帶有DCI-T的就行。三態DCI只適合于雙向信號。適用三態DCI的電平標準如下表:

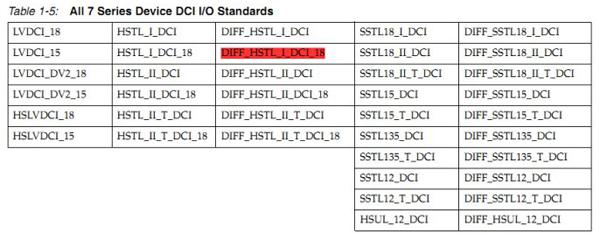

DCI所有的電平標準如下表。

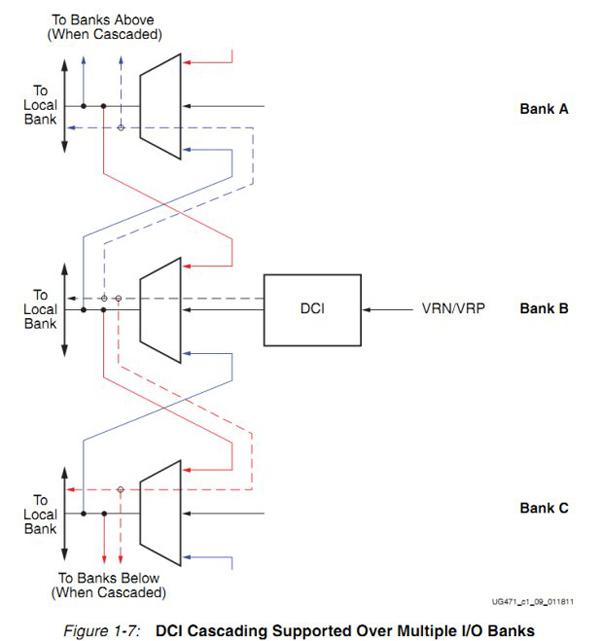

3.1 DCI迭代

7系列FPGA可以使用DCI迭代,DCI迭代就是同在一列的 I/O BANK可以共享一對參考電阻,即只要這一列的I/O BANK中的master BANK的RFN和RFP接了相應的電阻后,其他的slave BANK的RFN和RFP都不需要再接參考電阻了。這樣大大減少了元器件數量同時也減少了功耗。

3.1.1DCI迭代需要遵循如下規則:

(1)需要DCI迭代的管腳必須在同一列BANK上。

(2)同一列BANK需要分成MASTER和SLAVE BANK,他們應該有共同的Vcco和Vref.

(3)在同一列BANK上,但是沒有使用DCI技術的BANK可以不遵循第二條規則。

(4)為了實現這個DCI迭代,需要使用DCI_CASCADE Constraint.

3.1.2 約束語法規則:

CONFIG DCI_CASCADE = “ …”;

例如:

CONFIG DCI_CASCADE = “11 13 15 17”;

總之,對于7系列FPGA要正確使用DCI技術的話,要做如下:

第一、Vcco必須是基于合適的電平標準。

第二、使用正確的DCI I/O BUFFER通過電平標準屬性或者在HDL中例化的代碼中。

第三、DCI技術要求相應的BANK中VRN和VRP管腳用來連接正確的參考電阻,對于DCI迭代技術則只要master bank中的VRN和VRP管腳用來連接正確的參考電阻。有一種情況就是當DCI(帶阻抗控制驅動器)只作為輸入時,并且這些管腳又是僅有的使用了DCI電平的管腳,那么該BANK不需要將VRN和VRP接參考電阻。這些電平標準有以下這些。

3.1.3 遵守DCI I/O BANKING規則

(1)同一BANK的輸入管腳或者使用了DCI迭代的同一組的BANK的輸入管腳 ,其參考電壓Vref必須是一致的。

(2)在同一個BANK中Vcco必須兼容所有的輸入或輸出管腳。

(3)分立終端、阻抗控制驅動器、以及半阻抗控制驅動器,可以在同一BANK中同時存在。

4 DCI使用案例

4.1 注意

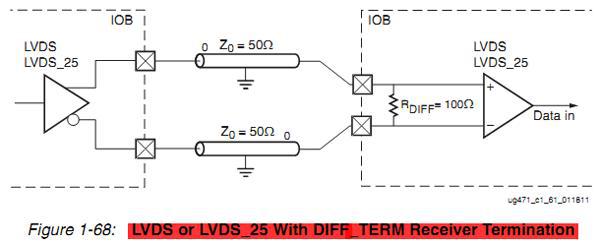

LVDS和LVDS25是不能使用DCI技術來進行終端匹配的,它只能通過內部終端電阻來進行匹配如下圖所示。

-

FPGA

+關注

關注

1629文章

21759瀏覽量

604273 -

芯片

+關注

關注

456文章

50950瀏覽量

424718 -

pcb

+關注

關注

4322文章

23126瀏覽量

398548

發布評論請先 登錄

相關推薦

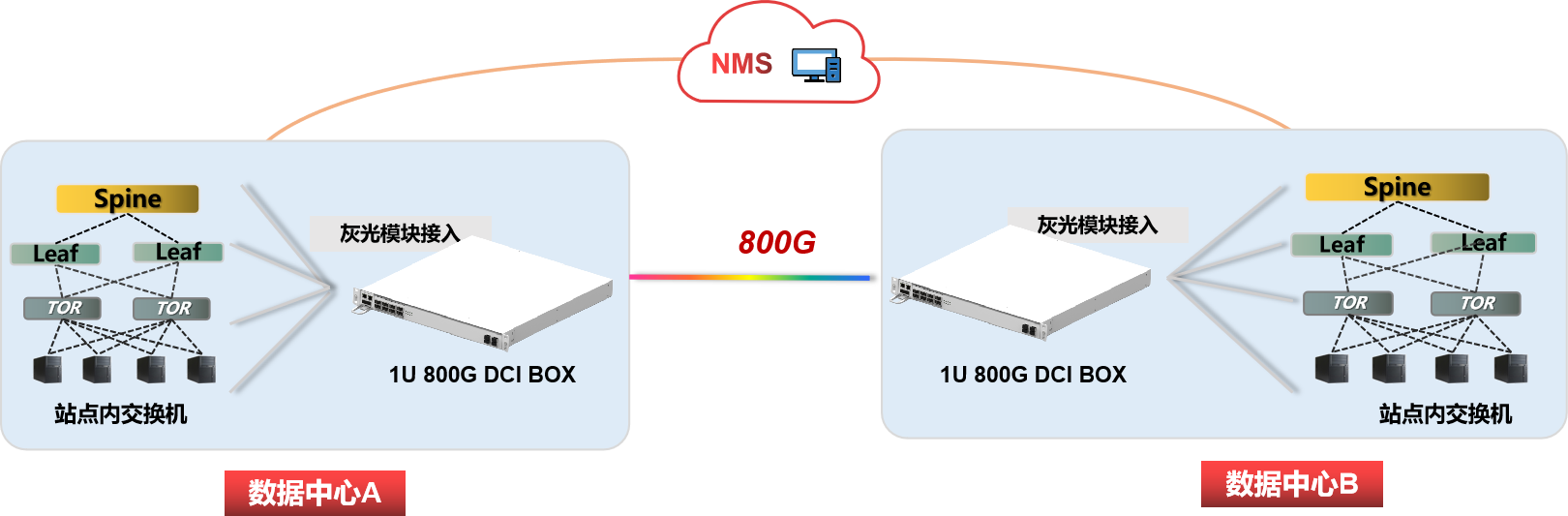

DCI 顛覆光器件產業?

Xilinx FPGA DCI使用方法

Vivado的DCI與內部參考電壓設置步驟

為什么銀行也沒有DCI匹配?

可以使用具有3.3V LVTTL輸入的DCI嗎?

如何在IBIS文件中配置SSTL135 DCI阻抗

最全面的7系列FPGA的DCI技術分析

DCI是什么?Xilinx 7系列FPGA的HP bank都支持DCI

DCI BOX與傳統WDM/OTN設備有什么區別?

易飛揚非相干DCI BOX的DCI傳輸方案介紹

非相干DCI BOX,提供更經濟的DCI傳輸方案

非相干DCI BOX,提供更經濟的DCI傳輸方案

DCI技術應用分析及DCI迭代需要遵循的規則介紹

DCI技術應用分析及DCI迭代需要遵循的規則介紹

評論