高速通信系統(tǒng)已經(jīng)在世界范 圍內(nèi)進入大規(guī)模建設(shè)階段,大量的信息交互促進了通信和計算機技術(shù)的迅猛發(fā)展,高速干線系統(tǒng)作為信息高速公路的主干,研究設(shè)計其所采用的高速芯片勢在必行。數(shù)據(jù)的傳輸方式,由于并行信號彼此之間的耦合與串?dāng)_限制了其工作速度和傳輸距離,而串行方式節(jié)約傳輸媒介,降低了系統(tǒng)互連的復(fù)雜性,傳輸速率更高、距離更遠,已在芯片之間、處理器與外設(shè)之間、高速硬盤接口、背板連接等領(lǐng)域廣泛應(yīng)用。

為了克服時鐘的最大翻轉(zhuǎn)頻率受到工藝限制的缺點,簡化電路設(shè)計的復(fù)雜度以及時鐘分布的難度,實現(xiàn)更高的速率,同時盡量降低系統(tǒng)功耗,半速率電路結(jié)構(gòu)逐步取代全速率結(jié)構(gòu)。本文根據(jù)2.5Gbps高速串行收發(fā)器的工作實際,為降低后續(xù)電路設(shè)計難度,采用工作速率較高的電流模式邏輯(Current Mode Logic,CML)設(shè)計了雙環(huán)時鐘數(shù)據(jù)恢復(fù)電路中的前端1:2解復(fù)用電路,采用SMIC 0.18 um模擬混合信號工藝實現(xiàn)并基于SpectraVerilog進行數(shù)模混合仿真,結(jié)果顯示電路可以正常工作,符合預(yù)期要求。

1 解復(fù)用電路單元

解復(fù)用電路把一路高速信號還原為若干路低速信號,常用結(jié)構(gòu)包括串行、并行、樹形以及上 述3種結(jié)構(gòu)的組合形式。串行解復(fù)用電路結(jié)構(gòu)簡單,時序關(guān)系清楚,可以實現(xiàn)任意1:N的解復(fù)用功能,但所有觸發(fā)器工作在輸入時鐘頻率上,其工作速度會制約電路的速度,因此串行結(jié)構(gòu)對觸發(fā)器設(shè)計和工藝的要求較高,而提高觸發(fā)器速率會帶來芯片功耗增加、電平擺幅減小,噪聲容限變小等問題,因此常用于低速系統(tǒng)中;并行結(jié)構(gòu)中觸發(fā)器工作在輸出數(shù)據(jù)速率上,對觸發(fā)器速率要求小,因此功耗較低、設(shè)計簡單,兼顧了速度與功耗,是1:2解復(fù)用電路的理想結(jié)構(gòu),但對于1:N解復(fù)用而言,N個并行連接的觸發(fā)器對前級電路構(gòu)成很大的電容負載,是速率提升變得困難;樹形解復(fù)用電路充分利用1:2并行解復(fù)用電路的優(yōu)點,使整個電路較前兩種結(jié)構(gòu)有高速低功耗的優(yōu)點。

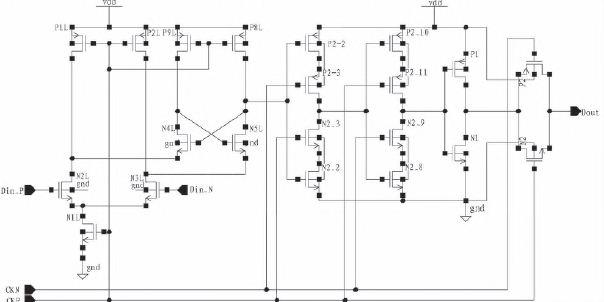

對于采用半速率結(jié)構(gòu)的高速串行收發(fā)器而言,整個電路性能主要受前端1:2解復(fù)用電路的限制,同時考慮到為了增強信號可靠性,待處理的輸人數(shù)據(jù)為差分?jǐn)?shù)據(jù),本文設(shè)計的1:2解復(fù)用電路采用類并行結(jié)構(gòu),如圖1所示,上下兩個電路為采用電流模式邏輯結(jié)構(gòu)的解復(fù)用電路單元,輸入為差分?jǐn)?shù)據(jù)和互補時鐘。

圖1 差分輸入互補時鐘的1:2解復(fù)用電路原理圖

電流模式邏輯電路相比傳統(tǒng)的CMOS電路可以在更低的信號擺幅情況下工作在更高的頻率。基于CML的解復(fù)用電路單元原理圖如圖2所示,其工作原理可以描述為:NMOS管N1L可以看做開關(guān)使用,在時鐘 CKP為低電平期間截止,由N2L、N3L、P1L和P2L構(gòu)成的輸入級處于保持模式,N4L和N5L的漏極被充電到高電平;在時鐘CKP為高電平期間導(dǎo)通,輸入級處于透明狀態(tài),電路接 收差分輸入數(shù)據(jù)Din_P和Din_N.電路中由P4L和P6L構(gòu)成的正反饋電路對前級起到鎖存作用,可以加速輸出數(shù)據(jù)的翻轉(zhuǎn),提高轉(zhuǎn)換速率;左下角的8個晶體管構(gòu)成平衡負載電路,可以保證N4L和N5L輸出線上的負載對稱。輸入數(shù)據(jù)在時鐘信號控制下送到輸出Dout,輸出數(shù)據(jù)與輸入數(shù)據(jù)反相。

圖2 解復(fù)用電路單元原理圖

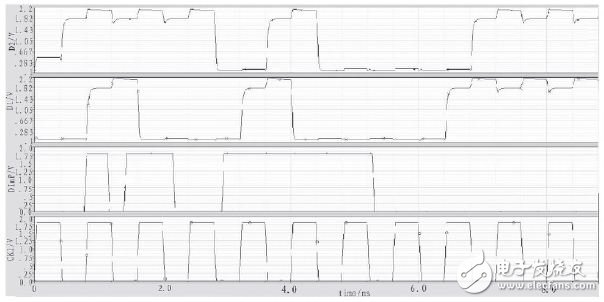

圖3 解復(fù)用單元電路仿真結(jié)果

對圖1所示的解復(fù)用模塊進行仿真,輸入為由互補的PWL分段線性源指定的位周期為400 ps的差分?jǐn)?shù)據(jù),采用周期T=800 ps,上升時間和下降時間為tr=tf=40 ps的脈沖電壓源作為時鐘信號,仿真結(jié)果如圖3所示。從圖中可以看出有效數(shù)據(jù)部分從時鐘的第二個高脈沖開始,從仿真結(jié)果可知,解復(fù)用電路可以正常實現(xiàn)數(shù)據(jù)1:2的串并轉(zhuǎn)換。

2 用于高速收發(fā)器的解復(fù)用電路

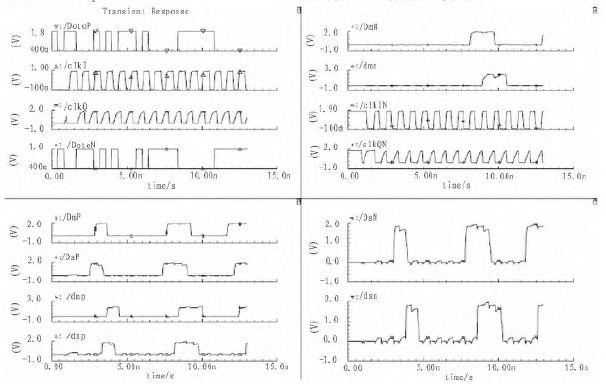

在高速串行收發(fā)器的接收端,為了保證數(shù)據(jù)的魯棒性和電路工作的可靠性,數(shù)據(jù)采用差分形 式。從第二部分可以看出基于CML的1:2解復(fù)用電路可以正常工作,因此可以以此為基礎(chǔ)搭 建用于高速差分串行數(shù)據(jù)半速率收發(fā)器的前端1:2解復(fù)用電路。電路原理圖如圖4所示。其 中clkI與clkIN、clkQ、clkQN為互補時鐘,clkI與clkIQ為正交時鐘,DinP和DinNer位差分 輸入的2.5Gbps串行數(shù)據(jù),DmP與DmN、DsP與DmN為1:2解復(fù)用后的兩路1.25Gbps查分?jǐn)?shù)據(jù)。

圖4 差分輸入差分輸出的1:2解復(fù)用電路原理圖

圖5 整體解復(fù)用電路的仿真波形圖

采用SMIC 0.18um模擬混合信號工藝完成電路設(shè)計,現(xiàn)對圖4所示解復(fù)用單元進行仿真。由于 分段線性電壓源在表示數(shù)據(jù)時特別繁瑣,而且單個指定數(shù)據(jù)難以保證仿真的隨機性和全面性 ,故而這里采用數(shù)模混合的方法進行仿真。輸入數(shù)據(jù)采用VerilogHDL語言編寫的偽隨機序列 ,采用Cadence的SpectreVerilog進行仿真。仿真結(jié)果如圖5所示,比較輸入數(shù)據(jù)和由主時鐘 采樣輸出的數(shù)據(jù),可以看出電路的解復(fù)用操作是正確的。

3 結(jié)論

本文描述了解復(fù)用電路的 傳統(tǒng)設(shè)計方法并分析了各自特點,根據(jù)2.5Gbps高速串行收發(fā)器的應(yīng)用實際,采用類并行結(jié)構(gòu)、基于電流模式邏輯設(shè)計了收發(fā)器的前端解復(fù)用電路,并分析了其工作原理,采用SMIC O.18 um混合信號工藝完成了電路設(shè)計,并采用SpectreVerilog進行了數(shù)模混合仿真,結(jié)果表明該電路在2.5Gbps收發(fā)器電路中可以穩(wěn)定可靠地工作。

-

芯片

+關(guān)注

關(guān)注

456文章

51019瀏覽量

425419 -

晶體管

+關(guān)注

關(guān)注

77文章

9711瀏覽量

138592 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2000瀏覽量

61256

發(fā)布評論請先 登錄

相關(guān)推薦

照明器具及其應(yīng)用電路 pdf免費下載

IGBT和IPM及其應(yīng)用電路教程pdf

集成電路應(yīng)用電路識圖方法分享

實用電子元器件學(xué)習(xí)+實戰(zhàn)書籍(圖表細說典型電路與失效分析)

給大家介紹一種PCB設(shè)計復(fù)用方法

照明器具及其應(yīng)用電路--應(yīng)用電路百例叢書

鏡像電流源原理及其應(yīng)用電路

電話接口及其PCM編譯碼和時分復(fù)用實驗

先進的PFC/PWM組合控制器UCC28510系列及其應(yīng)用電

波分復(fù)用技術(shù)與光密集波分復(fù)用在光纖通信網(wǎng)中的應(yīng)用和發(fā)展介紹

復(fù)用電路的設(shè)計方法及其特點介紹

復(fù)用電路的設(shè)計方法及其特點介紹

評論