引言

傳統的存儲設備雖然具有價格低廉的優勢,但是在高溫、高速、高沖擊的測試環境中,往往存在設備存放空間有限、測試參數較多、采集速率高、環境復雜等因素。為了得到準確的測試數據,對存儲設備的性能也提出了較高的要求,如高存儲速度、大存儲容量、小巧輕便、抗沖擊等。此時傳統的存儲設備便無法完成復雜環境測試數據的存儲任務。為解決這個問題,本文設計了基于NAND Flash的數據存儲系統,該系統采用Xilinx公司提出的靈活、高效、低成本的解決方案SOPC,把通用的RISC處理器MicroBlaze與用戶設計的特定功能邏輯電路集成到FPGA上,在FPGA的控制下將數據存儲到NAND Flash存儲設備中,實現了一個基于SOPC方案的嵌入式數據存儲系統。

NAND Flash存儲設備是Flash內存的一種,其內部采用非線性宏單元模式,為固態大容量內存的實現提供了廉價有效的解決方案。NAND Flash存儲器具有體積小、功耗低、讀寫速度快等優點,適用于大量數據的存儲,被廣泛應用到數碼相機、MP3、U盤等嵌入式產品中。

1 系統整體設計方案

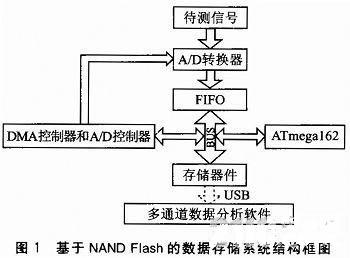

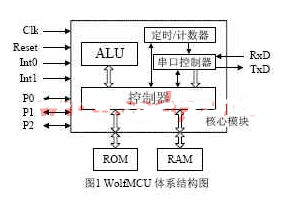

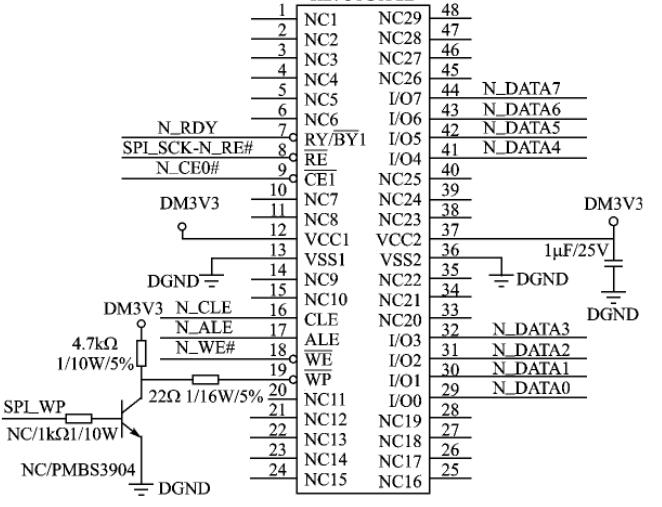

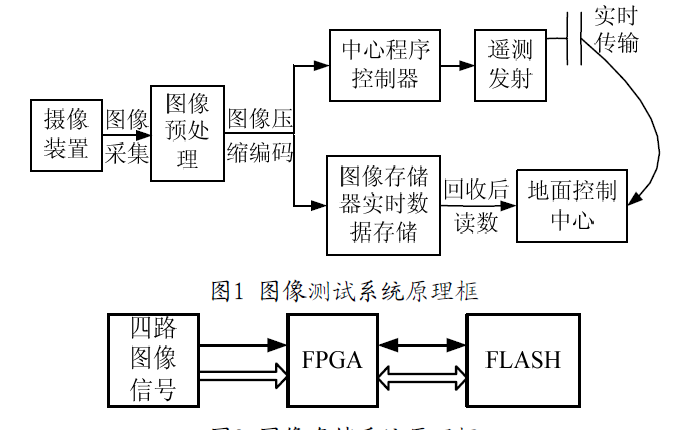

基于NAND Flash的數據存儲系統結構框圖如圖1所示。

本文采用Samsung公司的NAND Flash芯片K9F4GOSUOA作為主要存儲器件,控制器件使用Atmel公司的ATmega162和Xilinx公司Spartan-3E系列的XC3S500E,結合對NAND Flash的讀、寫、擦除等操作進行時序配置。A/D轉換芯片使用Maxim公司的MAX1308.另外,為實現通過USB總線將數據從采集設備傳送至PC,采用FTDI公司的FT245R芯片作為USB2.0接口控制器;并以LabVIEW為平臺設計開發了專用"多通道數據分析軟件",用于對存儲系統中數據后期的分析與處理。

2 NAND Flash陣列式存儲原理

Flash存儲器編程是以頁為單位,單片NAND Flash的單頁編程操作時,命令鎖存信號CLE向端口寫入編程操作命令,地址鎖存信號ALE寫入操作塊地址,并傳輸2 KB數據到數據寄存器后,Flash進入編程階段。此時其端口R/B信號被拉低,顯示Flash正處于忙工作狀態,直到編程結束,這段時間系統不能對該Flash再進行任何操作,一般該階段典型的時間為200μs.如果使用單片Flash存儲器進行存儲,則需等待編程結束后才能再寫入數據。這樣大量的時間耗費在編程過程中,極大限制了系統存儲速度的提高。

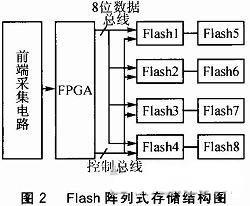

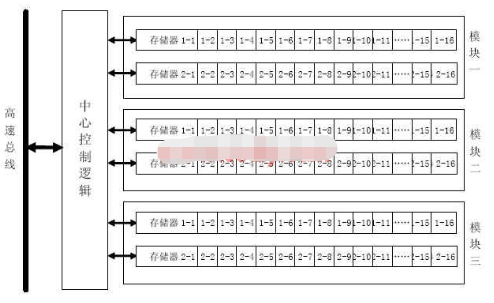

為提高系統的存儲容量和存儲速度,系統使用8片NAND Flash存儲器,每4片為一組構成一個總線寬度為8位的存儲陣列。控制信號中除設置獨立的片選信號CE外,其他的控制信號為8片共用;兩組Flash共用數據總線,存儲數據時先對第一組Flash進行存儲操作,待第一組存儲完畢后再對第二組進行數據存儲操作。Flash陣列式存儲結構圖如圖2所示。

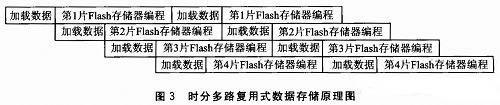

由以上分析可以看出,Flash存儲數據的過程由寫地址命令、數據傳輸以及Flash編程階段組成。為提高系統整體的存儲速度,減少系統等待時間,根據NAND Flash存儲器的特點,借鑒時分多路復用技術,設計了Flash存儲陣列,即利用上一片Flash的編程時間對下一片Flash進行操作,將數據加載到該片數據寄存器中,以此類推實現四級的流水線。這樣整個系統每個時刻都能對Flash加載數據,保證了數據存儲的連續性。

時分多路復用(Time Division Multiplexing,TDM)是按傳輸信號的時間進行分割的,它使不同的信號在不同的時間內傳送,將整個傳輸時間分為許多時間間隔,每個時間片被一路信號占用,這樣既可以保證各傳輸信號的相互獨立,又提高了系統的傳輸效率。借鑒該原理,可以將Flash的編程時間看成一個固定的時間段,將這個時間段分成4個時間片,在這4個時間片上分別對Flash陣列的一個模塊中的4個Flash加載數據,輸入存儲系統的高速數據流看作是以傳輸一組數據所需時間的一個時間片。

具體的操作如下:首先加載數據到第1片Flash存儲器中,該Flash進入編程狀態;在第1片Flash的編程時段內,對第2片Flash進行數據加載操作;當第2片進入編程狀態時,再對第3片進行數據加載操作;依次執行下去,待一次整體操作完成后4片Flash都已加載完數據。此時,第1片Flash的編程已經完成,處于準備就緒狀態,可以寫入新的數據,由此可以等效為Flash存儲器的編程時間為0.這樣就可以實現Flash陣列的連續傳輸數據,提高系統的整體速度。

多片Flash時分多路復用式數據存儲原理如圖3所示。

3 系統硬件實現

系統采用了Xilinx公司的FPGA進行SOPC開發,處理器選用了MicroBlaze軟核,并配置相應的參數使標準IP核適應用戶所設計的系統,結合外圍電源電路、USB接口電路、程序配置電路,構成了一套穩定的數據存儲系統。

3.1 FPGA片上系統的實現

FPGA程序主要的功能是:軟件控制啟動存儲,在控制邏輯的作用下將前端A/D轉換之后的數據先存入內部FIFO緩存中,同時啟動DMA將緩存中的數據存儲到外部NAND Flash存儲陣列中。本文利用VHDL語言編寫程序,在FPGA芯片上實現了數據的高速存儲和傳輸控制。

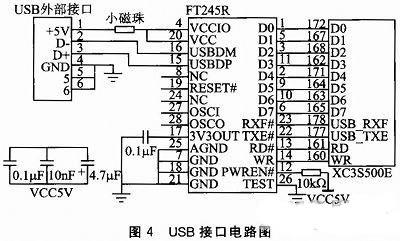

3.2 USB接口電路模塊

USB器件主要用于實現SOPC系統在聯機模式下與主機通信以及數據的傳輸。USB芯片使用由FTDI公司推出的FT245R,該接口能夠將USB接口信號轉換為8位并行信號,上傳至時鐘頻率為150 MHz的MicroBlaze處理器進行分析處理;并將處理器發送的數據轉換成標準的USB接口數據傳向PC機,完成SOPC系統與PC機之間的通信。USB接口電路如圖4所示。

3.3 FPGA配置電路模塊

本系統在FPGA配置電路中采用了主串配置模式。外部的配置芯片選用了XCF04S系列的PROM串行配置芯片。當系統上電時,芯片以主動配置方式來實現系統中FPGA的硬件配置。通過高速的串行接口,整個芯片的配置工作可以在很短的時間內完成。

3.4 電源模塊

電源模塊不僅能夠為系統各器件提供各種高性能的功率輸出,還能夠選擇合適的旁路、去耦電容來濾除各種干擾信號,保證系統的穩定工作。本系統電源模塊采用了TI公司的TPS75003芯片配置相應的外圍電路,實現了由5 V輸入電壓到3.3 V、2.5 V和1.2 V輸出電壓的精確轉換。

4 系統驗證與分析

在系統的軟硬件程序設計完成并生成BIT流文件后,下載到FPGA電路板上,結合PC機中的專用軟件對系統功能進行驗證測試。

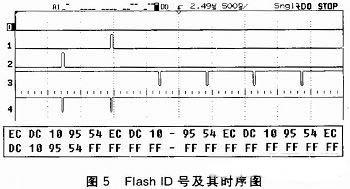

4.1 對NAND Flash的操作驗證

在數據存儲硬件系統設計過程中,用戶IP核設計得好壞決定著整個系統設計的成敗。系統IP核設計中集成了Flash控制器、DMA控制器以及數據和地址FIFO,為驗證該IP核是否能正常工作,對其進行了Flash操作驗證。示波器捕獲的讀Flash存儲器ID號時序圖如圖5所示。其中通道0~4分別代表Flash的CE(片選)、ALE(地址鎖存)、CLE(命令鎖存)、RE(讀)、WE(寫)信號。圖中Flash陣列的4片Flash的ID號都為EC DC 10 95 54,這與實際Flash ID相符。實驗證明,Flash存儲器的ID號是準確的。

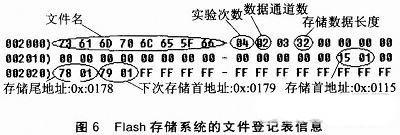

4.2 文件登記表驗證

實驗中在Flash存儲器的特定位置存有標記數據特征的文件登記表,應用程序讀取文件登記表中的信息并將相應數據傳輸到PC機上進行后期分析。文件登記表的存儲內容有:文件名、實驗的次數、存儲數據的長度、本次存儲的首尾地址以及下次存儲的首地址等。

圖6為某次存儲實驗的文件登記表信息,圖中前8個字節為文件名,往后依次為實驗次數和數據通道數。本次實驗中存儲的長度為50 MB,存儲首地址和存儲尾地址分別為0x0115、0x0178.由于所用的存儲策略為4片流水線式存儲,每片Flash每塊為128 KB,4片組成的模塊中每個大塊為512 KB(128 KB×4),所以可以計算出存儲的數據為512 KB×(0x0178-0x0115+1)=50 MB.這與所指定的本次存儲數據的長度吻合,表明存儲系統正確可靠。

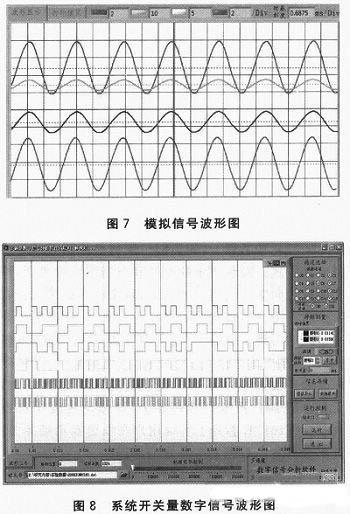

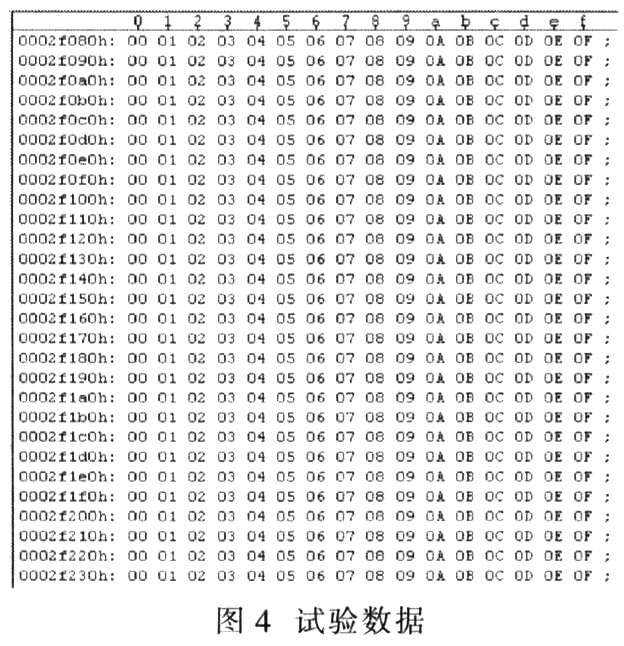

4.3 數據存儲驗證

系統構建完成后,在實驗室環境中,對信號發生器產生的正弦波信號進行采集存儲,通過USB接口將存儲在NAND Flash芯片中的數據上傳到PC機中,利用以LabVIEW為平臺設計開發的"多通道數據分析軟件"進行分析處理,得到的模擬信號及系統開關量數字信號波形如圖7、圖8所示。

對比原始信號發現,系統能夠快速、無失真地采集并存儲信號發生器產生的波形數據,并且能夠利用不同的采樣速率來記錄系統開關量數字信號信息,具有較高的可靠性。

結語

本文設計了基于NAND Flash的數據存儲系統,通過時分多路復用式流水線操作,極大地提高了Flash芯片的存儲速度。實驗表明,該系統能夠快速、準確地記錄信號發生器產生的波形數據,且具有性能穩定可靠、操作簡單、抗過載能力強等優點。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604299 -

FlaSh

+關注

關注

10文章

1638瀏覽量

148193 -

vhdl

+關注

關注

30文章

817瀏覽量

128174

發布評論請先 登錄

相關推薦

基于FPGA器件實現大容量高速存儲系統的方案設計

標準NAND FLASH控制器

標準NAND FLASH控制器/超高速NAND FLASH陣列控制器

NAND閃存存儲系統的低故障率如何實現?

NAND Flash嵌入式存儲系統設計

NAND Flash存儲系統解決方案

基于FPGA并以Flash為存儲介質的高速圖像數據存儲系統設計

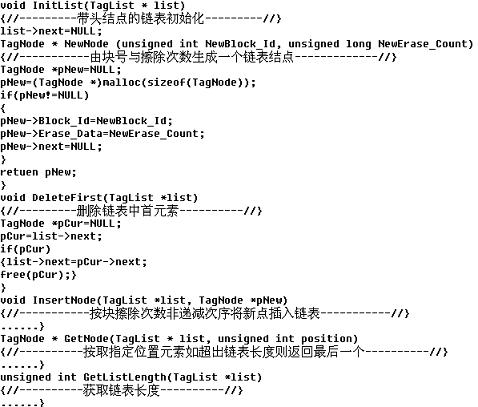

采用VHDL語言在FPGA上實現WolfMCU體系結構的設計

采用VHDL語言在FPGA芯片上實現NAND Flash的數據存儲系統的設計

采用VHDL語言在FPGA芯片上實現NAND Flash的數據存儲系統的設計

評論