1 引言

隨著EDA技術的發展及大規模可編程邏輯器件CPLD/FPGA的出現,電子系統的設計技術和工具發生了巨大的變化,通過EDA技術對CPLD/FP-GA編程開發產品,不僅成本低、周期短、可靠性高,而且可隨時在系統中修改其邏輯功能。本文介紹了一種以Altera公司可編程邏輯器件EP1K30TC144-3為控制核心,附加一定外圍電路組成的出租車計費器系統。

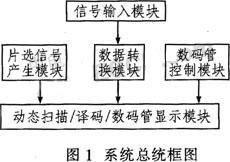

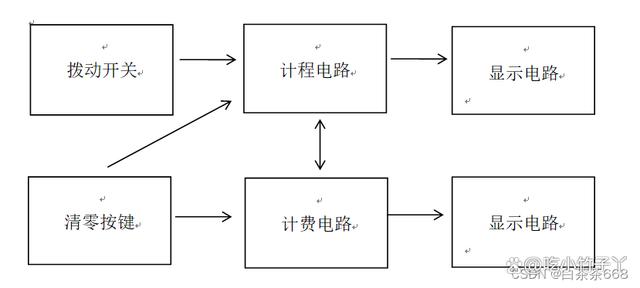

2 系統總體結構

基于CPLD的出租車計費器的組成如圖1所示。各部分主要功能包括:信號輸入模塊對車輪傳感器傳送的脈沖信號進行計數(每轉一圈送一個脈沖),并以高低脈沖模擬出租汽車啟動、停止、暫停、加速按鈕,具有輸入信號作用;數據轉換模塊將計費模塊輸出的車費和路程轉換成4位的十進制數據;譯碼/動態掃描模塊將路程與費用的數值譯碼后用動態掃描的方式驅動數碼管;數碼管顯示模塊將公里數和計費金額均用4位LED數碼管顯示(2位整數,2位小數)。

3 單元模塊設計

3.1 信號輸入模塊

該模塊主要實現計費功能和現場模擬功能。計費標準為:對車輪傳感器傳送的脈沖信號進行計數(每轉一圈傳送一個脈沖),按行駛里程 計費,起步價為7.00元,并在車行3 km后按2.40元/km計費,當計費器達到或超過20元時,每公里加收50%的車費,車停止不計費。并以高低脈沖模擬出租汽車啟動、停止、暫停、加速按鈕,具有輸入信號的作用。

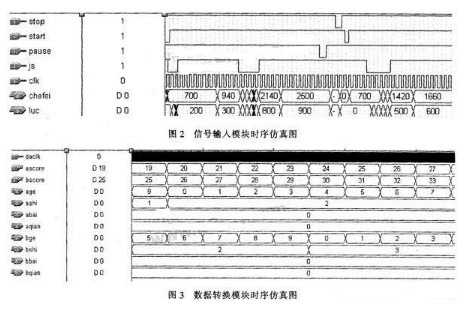

該模塊的時序仿真圖如圖2所示。圖中的stop下降沿到來時系統不計費,車費為“0”,路程為“0”,起步價為7.00元,在車行3 km(圖中300為3 km。因為后面有2位小數)后按2.40元/km計費,當計費器達到或超過20元時,每公里加收50%(即按3.60元/km)的車費。

3.2 數據轉換模塊

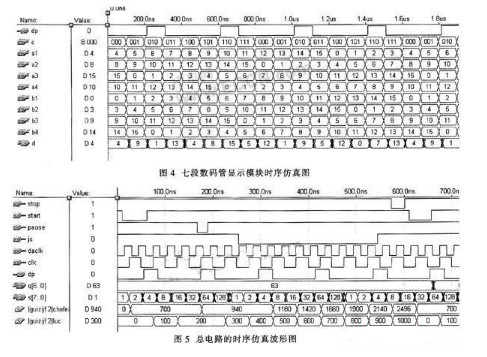

數據轉換模塊是一個模為10、步長可變的加法計數器,可將計費模塊輸出的車費和路程轉換成4位的十進制數。該模塊通過開關量預置步長,當超過一定預置參數時改變步長。計費模塊也采用非壓縮BCD碼,但因步長不為1,所以在做非壓縮BCD加法時必須調整,否則可能導致在超過或未超過預置參數時出現超程錯誤。這里采用模仿微機的AF標志位,在其設立一個半進位標志,當累加和大于9或半進位標志為“1”時,對其累加和調整。轉換模塊的時序仿真圖如圖3所示,可見能將路程和車費轉換為4位的十進制數,便于8位數碼管顯示。

3.3 顯示模塊

顯示模塊是由七段LED數碼管譯碼和動態掃描顯示兩部分組成。采用的是共陰極七段數碼管,根據十六進制數和七段顯示段碼表的對應關系,其中要求路程和車費都要用2位小數點來表示,所以須設置一個控制小數點的變量,即程序中的dp。這段程序所示的是在數碼管的第二、第六個后面顯示小數點,實現了路程和車費都用2位小數點表示的功能。要注意的是如果選擇的掃描頻率不合適,可能會出現小數點閃動的情況。但只要掃描頻率不小于24 Hz,人眼就感覺不到顯示器的閃爍。本系統采用36 Hz的掃描頻率,掃描脈沖由相應的外圍電路提供。七段數碼管顯示模塊的時序如圖4所示。

數碼管控制及譯碼顯示模塊將十進制的輸入信號用七段數碼管顯示,由七段發光二極管組成數碼顯示器,利用字段的不同組合。可分別顯示0~9十個數字。本設計中,要求輸出的段信號為低電平有效。

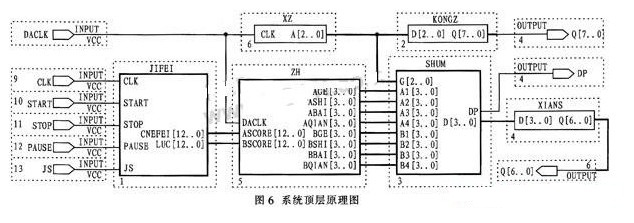

4 系統仿真、綜合、下載

仿真是EDA技術的重要組成部分,也是對設計的電路進行功能和性能測試的有效手段。EDA工具提供了強大且與電路實時行為相吻合的精確硬件系統測試工具。在建立了波形文件、輸入信號節點、波形參數、加輸入信號激勵電平并存盤之后,選擇主菜單“MAX+plusII”中的仿真器項“Simulator”,彈出對話框之后單擊“Start”進行仿真運算,完成之后就可以看到時序波形。圖5為總電路的時序圖。

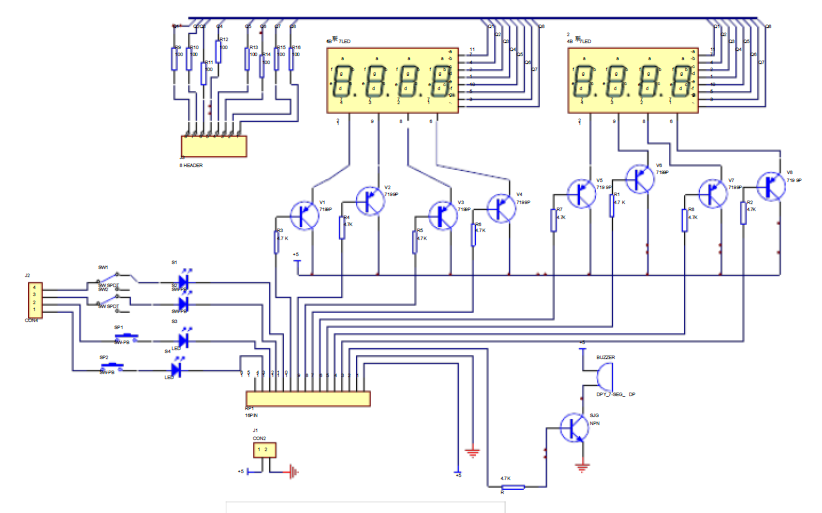

最終的電路設計完成后,若總體電路編譯無錯,且時序仿真成功,可進行硬件測試。將總電路下載到可編程邏輯器件中,按fit文件中自動分配引腳搭建硬件電路。系統頂層原理圖如圖6所示。

打開電源,數碼管有正確的數字顯示,操作運行實驗結果完全符合要求。查看報告文件可得到器件引腳的利用情況及器件內部資源的使用情況,通過更換適當的器件使其資源配置達到最優。選擇器件的一般原則是系統所使用的資源不要超過器件資源的80%,若超過90%,系統功耗將增大,工作不穩定。本設計中輸入、輸出引腳各用22個,器件資源利用率僅為62%,具有較大的擴展空間。

5 結束語

出租車計費器計數脈沖來自車輪轉速傳感器(干簧管),脈沖經器件內部整形后送至計數器;動態掃描脈沖由外圍電路給出,將單位脈沖看做行駛的單位公里數,并在此基礎上進行計費與顯示。系統采用整流、濾波、降壓后的出租車電源供電。

實驗表明:該計費器實現了按預置參數自動計費(最大計費金額為99.99元)、自動計程(最大計程公里數為99.99 km)等功能;能夠實現起步價、每公里收費、車型及加費里程的參數預置(如:起步價7.00元;3 km后,2.40元/km;計費超過20.00元,每公里加收50%的車費等),且預置參數可調范圍廣。由于采用CPLD大規模可編程邏輯器件,整機功耗小、抗干擾能力強、系統穩定、工作可靠、升級方便。另外,由于器件資源尚有較大的擴展空間,根據實際需要,系統可方便地增加所需功能,如通過器件內部編程增加時鐘功能,既可為司機和乘客提供方便,又能為夜間行車自動調整收費標準提供參考;還可以通過FPGA的輸出引線控制語音器件,對顧客發出問候語,提醒其所要收繳的費用等;也可以通過FPGA的輸出引線控制打印機打印發票等。

-

FPGA

+關注

關注

1629文章

21746瀏覽量

603756 -

cpld

+關注

關注

32文章

1248瀏覽量

169393 -

eda

+關注

關注

71文章

2764瀏覽量

173330

發布評論請先 登錄

相關推薦

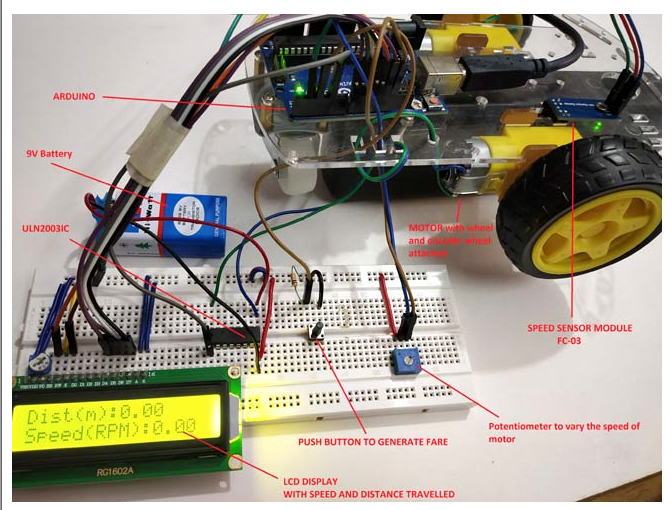

如何使用Arduino制作數字出租車計費器

多功能出租車計費器的相關資料推薦

基于CPLD/FPGA的出租車計費器

基于FPGA的出租車計費系統的設計與實現

出租車計費系統設計

如何使用CPLD實現出租車計費器的設計

以EP1K30TC144-3為控制核心實現CPLD出租車計費器系統的設計

以EP1K30TC144-3為控制核心實現CPLD出租車計費器系統的設計

評論