引言

分頻電路在頻率合成、光纖通信、無線通信等系統中有著廣泛應用。在高速通訊系統中, 當數據傳輸速率達到或超過10GB/s時,傳統的實現方法是采用雙極性硅、GaAs、InP等工藝 實現,但由于其較高的電壓和電流,其功耗也相對較大。隨著CMOS工藝向深亞微米發展, 其低功耗、高集成度、低價位、高性能的優勢使CMOS工藝日益成為業界主流工藝,提高CMOS 工藝分頻器的工作速度,成為設計的一個熱點[3]。高速分頻電路一般有三種電路結構:基于 TFF(Toggle Flip-Flip) 的分頻器,注入鎖定分頻器和再生分頻器。注入鎖定分頻器輸出時 鐘穩定,用于對輸出時鐘要求較高的場合,利用注入鎖定分頻系統可以實線非常高速的分頻 設計[4],但這種分頻器一般鎖定范圍很窄,且結構復雜,功耗偏大;再生分頻器在高頻時具 有更高的鎖定范圍,但需要使用很多無源器件,占用芯片面積很大,且不利于電路匹配。

基于TFF的CMOS分頻電路主要有以下幾種:源極耦合邏輯(SCFL)電路,通常,超高速 分頻器采用SCFL邏輯實現的居多[5],這種結構邏輯可以工作在輸入信號擺幅比較低的情況 下,因此電路速度較快,但這種結構層次較多,不適合低電源電壓下的超高速分頻器設計; 針對SCFL在低電源電壓下存在的問題,文獻[5]提出了偽差分邏輯電路,這樣低電源電壓下 電壓分配的問題得到了緩解,但是需要完全互補的時鐘信號來確保鎖存器的正常工作,在高 速通信中,電路的測試條件很難滿足;文獻[6]根據負載電阻是鎖存器速度的一個關鍵因素 提出了差動動態負載邏輯電路結構,電源電壓1.8V時,采用標準0.25μm CMOS工藝,最高工 作頻率超過16GHz,功耗約為3mW,由此看出,動態負載確實可以提高電路速度,輸出信號幅 度也足夠大,但是差分時鐘信號的相同直流偏置不易選擇,有文獻提出采用不同的直流偏置,但都會引入其它的問題;提出了單時鐘信號控制的動態鎖存邏輯結構,有效解決了 直流偏置問題,本文采取此結構實現了超高速分頻,并且給出了具體分析設計過程。

1. 分頻電路原理與設計

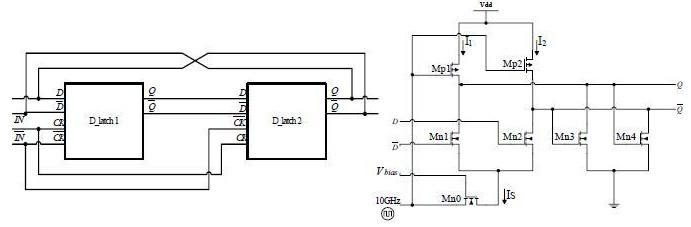

基于TFF的分頻器一般使用電流模式邏輯(CML),可獲得很大的工作頻率范圍,且通常由 兩個相同的互相耦合的鎖存器構成,圖1給出了分頻器的結構,由兩個CML D鎖存器組成。鎖 存器2的輸出反饋至鎖存器1的輸入,當時鐘為低電平時,鎖存器1工作在采樣模式,鎖存器2 工作在鎖存模式;時鐘為高時,鎖存器1工作在鎖存模式,鎖存器2工作在采樣模式。因此, D觸發器輸出數據變化發生在時鐘變化邊沿,且每兩個時鐘周期,數據只發生一次跳變,從 而實現了二分頻。

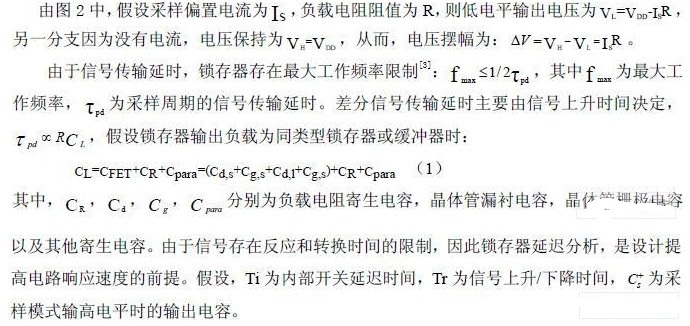

圖2為動態CML D鎖存器電路結構,采樣部分由Mn0、Mn1、Mn2組成,Mn3、Mn4組成 的正反饋鎖存邏輯電平。電路具有以下特點:

采用PMOS 作為動態負載,可實現不同負載的有效控制,在DFF 的采樣狀態,PMOS 負載 晶體管工作在線性區,其打開電阻非常小,較小的RC 時間常數使得NMOS 對(Mn1,Mn2)能夠 以較快的速度感應D / D 輸入數據的變化,正反饋連接的NMOS 對(Mn3,Mn4)進一步加速狀態 的轉換;維持狀態,PMOS 負載晶體管關斷,產生較大的RC 延時,正反饋連接的NMOS 對 (Mn3,Mn4)保持DFF 的輸出數據。

電路由單時鐘控制,時鐘分別加在PMOS 管的柵極和NMOS 管的源極,通過使用共柵極組 態,輸入時鐘信號CK 的直流偏置可以同時對PMOS 負載和NMOS 開關進行優化。這個技術能 使鎖存器工作在更高的頻率上。同時共柵連接的NMOS(Mn0)允許其穩定的工作在較低的電源 電壓下[6],適當調節,可達到零閾值電壓。

開關管MN0 的導通和關斷是鎖存器工作在采樣和保持模式的條件,因此要使鎖存器正常 工作,MN0 不能始終導通。這樣,比之于一直導通的電流源,該鎖存器的功耗明顯降低。

2.設計過程

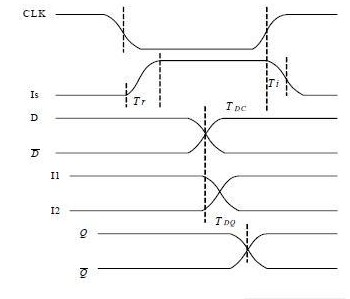

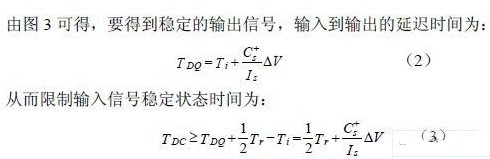

2.1 D 鎖存器延時分析

2.2 D 鎖存器具體設計步驟

首先,根據所要求的參數,如速度、擺幅、電壓、電流、負載等等確定電路具體結構, 本文中根據速度和功耗的要求,以及前面對各結構的分析,采用動態負載結構。

其次,根據所采用的工藝,提取所需要的晶體管基本參數,根據(2)、(3)式,當輸 入信號速度達到10GB/s,結合需要達到的參數要求,選擇合適的便置電流Is。

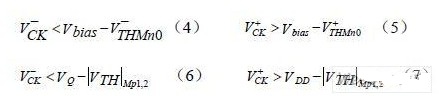

第三,進行靜態工作點分析,CK 輸入為低電平時,MN0 導通,同時MP1、MP2 工作 在線性區;而CK 為高時,Mn0 關斷,Mp1 和Mp2 工作在截止區;可得到:

由式(6)、(7)可確定CK 的直流工作范圍,而式(4)、(5)可確定偏置電壓的大小范圍。 第四,根據以上計算的靜態電流和電壓偏置等數值,結合提取的工藝參數,估算各晶 體管的寬長比。

第五,在靜態工作點正確的情況下,將鎖存器接成分頻器結構,并進行瞬態分析,使 分頻器自由振蕩,測算分頻器自由振蕩時的輸出頻率,如果要求分頻器正常工作時輸入的時 鐘頻率為f,則認為分頻器自由振蕩的輸出頻率為f/2 最佳。

靜態工作點需要根據系統的實際情況,通過仿真進行調整,而重復以上第二到第五步 驟的過程。此外,鎖存器中決定其工作速度的因素有:Q 、Q 兩節點的電容,輸出電壓擺幅 和充、放電電流。為提高電路速度,電路設過程中要盡量減小Q 、Q 兩節點的電容,增大充、 放電電流,而對輸出電壓擺幅的要求要從兩方面考慮,輸出電壓擺幅過大,充、放電過程持續時間會增加,輸出電壓擺幅過小,則無法驅動后續電路。因此,要合理設計輸出電壓擺幅。

3 仿真結果

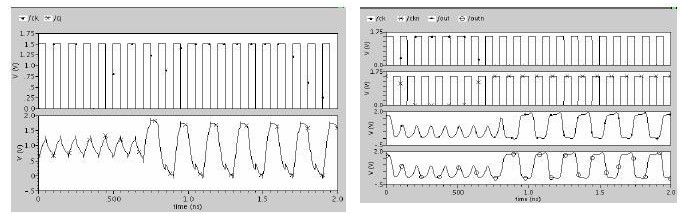

本文采用SMIC 0.18um 1P6M CMOS 工藝,使用Cadence 公司的Spectre 仿真器,對電 路進行了各種情況仿真。本文對分頻電路在室溫下對不同的工藝角進行了仿真,仿真結果顯 示,在Typical NMOS 和Typical PMOS 下,分頻器最高可以工作在13.5GHz,在快NMOS 和快PMOS 下,分頻器可以達到14GHz 以上頻率。10GHz 時鐘下的輸入輸出信號波形如圖 4 所示,其中,Vin1為輸入時鐘信號,OUT 為輸出信號。調試參數為:VCLK-=0V,VCLK+=1.5V, T=100ps, Vbias=1.2V. Wmp1、Wmp2=5.5u,Wmn1、Wmn2=4.4u,Wmn3、Wmn4=2.2u,Wmn0=16u, L=0.18u。

圖4 波形中可以看出,信號在兩級鎖存器間傳遞時,由于信號的突變,而引起毛刺,在 信號輸出端加上緩沖電路,可以淹沒這種影響,其波形輸出如圖5 所示,由圖可知分頻器很 好實現了兩路正交輸出信號,正確實現了二分頻,輸出擺幅也滿足設計要求。

表1 給出本文中電路功耗所用電路功耗。可以看出,本文電路設計功耗相對 較低。

4 結論

本文采用SMIC 0.18um 1P6M CMOS 工藝,單時鐘信號控制的動態鎖存邏輯結構,在 電源電壓為1.8 V 的情況下,仿真實現了一個10 GHz(可工作頻率范圍為1~13.5 GHz)、功 耗僅為3.1 mW 的分頻器。該電路結構簡單、功耗低,可用于光纖通訊、雷達、測量等系統 中,具有較廣泛的應用前景。

-

電源

+關注

關注

184文章

17740瀏覽量

250566 -

CMOS

+關注

關注

58文章

5722瀏覽量

235635 -

分頻器

+關注

關注

43文章

447瀏覽量

49965

發布評論請先 登錄

相關推薦

基于TFF的CMOS技術實現超高速分頻的設計

基于TFF的CMOS技術實現超高速分頻的設計

評論