曼徹斯特碼編碼、解碼器是1553B總線接口中不可缺少的重要組成部分。曼徹斯特碼編解碼器設計的好壞直接影響總線接口的性能。本文介紹的是MIL-STD-1553B接口中最曼徹斯特碼的編碼和解碼器的設計實現。

在電子設計領域,可編程器件的廣泛應用為數字系統的設計帶來極大的靈活性,1片FPGA/CPLD芯片可替代上百個IC電路。同時,Altera公司開發的MAX+PLUS II和QUARTUS II軟件,是完全集成化的可編程邏輯設計環境;Synplicity公司的Synplify是專門用于FPGA和CPLD的一種優秀邏輯綜合工具;VHDL更是一種功能強大的硬件設計語言,可用簡潔的代碼描述來進行復雜控制邏輯的設計。所這些使得硬件的設計如同軟件那樣方便,極大方便了數字電路的設計。所有這些條件都為在實驗室開發實現MIL-STD-1553B協議接口提供了有利條件。文中所設計的編碼、解碼器就是采用硬件描述語言VHDL進行編程,用Synplify進行綜合,以及采用MAX+PLUS II進行時序仿真,在FPGA上實現的MIL-STD-1553B總線接口中的曼徹斯特碼編碼、解碼器。

1 1553B總線及其接口功能

MIL-STD-1553B的全稱是:飛機內部時分制指令/響應式多路傳輸數據總線。它用可屏蔽雙絞線進行數據傳輸,信號是以串行數字脈沖的形式進行傳輸,其數據代碼用雙相曼徹特碼的形式來表示,其傳輸速率為1Mb/s。1553B數據總線上連接有三種類型的系統:①總線控制器(BC)——控制總線上的數據傳輸;②遠程終端控制器(RT)——響應BC來的命令,執行數據傳輸;③總線監視器(BM)——有選擇地接收數據總線上的信息并保存之。每個子系統可以通過1553B總線連接到任何一個子系統。數據就是在總線上進行傳輸的。

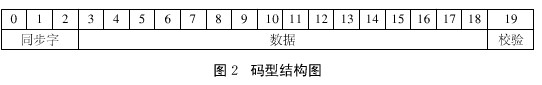

在總線上傳輸的有三種類型的字:命令字、狀態字和數據字。每種字的字長為20位,有效信息位是16位每個字的前三位為同步字頭,最后一位為奇校驗位。有效信息(16位)及奇偶校驗位在總線上以曼徹斯特碼的形式進行傳輸,每位占的時間為1μs。同步字頭占三位,或先正后負(命令字、狀態字)或先負后正(數據字)。正/負電平各占1.5μs,即占同位場的一半。由于系統的類型不同,可辨別出命令字和狀態字,命令字由現行的總線控制器發出,而狀態字總是由遠程終端RT發出。

作為MIL-STD-1553B總線的接口應完成以下功能:①將總線上的串行信息流轉換成處理機可以處理的并行信息或者與之相反;②接收或發送信息時,能夠識別或生成標準的1553B信息字和消息;③完成與處理機之間的信息交換,包括1553B信息地址的分配,命令字(或狀態字)的譯碼或返回狀態字、發送數據字等。曼徹斯特碼編解碼器完成的是曼徹斯特碼的編碼及解碼,并檢測錯誤。它接收具有有效同步字的曼徹斯特碼,并進行譯碼,

以及識別其類型和串/并轉換、奇偶校驗等;或者將處理器發出的并行二進制數據進行曼徹斯特碼編碼,再加上同步字頭及奇偶位使之成為符合1553B標準的字進行輸出。

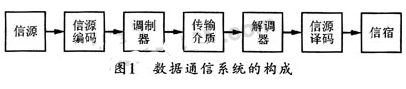

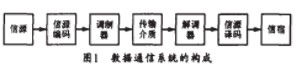

編解碼器是總線接口的一部分。一般說來,1553B總線接口由電平轉換電路、曼徹斯特碼編解碼器、命令字/狀態字譯碼邏輯和CPU及相關電路組成,如圖1所示。

除了編解碼器可由FPGA來實現外,它與CPU之間的相關電路,如共享RAM、命令字/狀態字譯碼和存儲器管理、處理器與存儲器接口邏輯等也可以由FPGA來實現;CPU可采用TMS320LF2407。本文所介紹的就是其中的編碼和解碼器的設計。

2 曼徹斯特碼編解碼器的總體設計

在介紹編解碼器的設計之前,有必要了解曼徹斯特碼的特征,以便在設計中對其加以利用,達到簡化電路的效果。

曼徹斯特碼是一種廣泛應用于航空電子綜合系統中的總線數據傳輸的雙極性碼。它在每個碼位中點存在一個跳變。1信號是一個由1到0的負跳沿,而0信號是由0到1的正跳沿。它本身包含了自定時的信息。因此它不需要獨立的信道來傳輸位定信息,它可以直接從數據中分離出定時時鐘,同時還能與變壓器耦合相協調,十分適合用在變壓器耦合形式,長度為150m(500英尺)左右的場合,因此在航空電子綜合系統中,它是最主要的形式。

在MIL-STD-1553B協議中其數據格式為如圖2所示。

根據1553B的數據格式以及曼徹斯特碼的特點,可采用狀態機對其進行編碼、解碼的實現。狀態機是一個廣義的時序電路,像移位寄存器、計數器等都算是它的特殊功能類型中的一種。根據輸入、輸出及狀態之間的關系,狀態機可分為兩類:一種是輸出狀態有關,而輸入與狀態無在的狀態機類型,稱為More狀態機;另一種是輸出及輸入與狀態皆有關系的狀態機,稱為Mealy狀態機。本設計采用的是Mealy狀態機。編碼和解碼是兩個相互獨立的模塊。

2.1 解碼

解碼的過程可分為三部分:①同步字頭檢測,并辨別其為數據字還是命令字。②對曼碼形式的數據進行解碼。由于曼徹斯特碼自帶定時時鐘,故可從數據中分離出同步時鐘。本設計采用的是傳統的用數字鎖相環的方法來分離時鐘;將時鐘和數據進行處理使曼碼數據轉化為非歸零二進制數據。③將串行數據轉化為并行數據,并進行奇偶校驗。解碼器的邏輯圖如圖3所示。圖中data為串行輸入數據。當data開始發生跳變時進行同步頭檢測,若在data發生變化后檢測到大于一個位時的高(或低)電平,則認為同步頭有效,輸出同步頭類型(comnd)及同步頭檢測位(synerr)(為低電平,若為高電平則表示同步頭有錯)。在同步頭有效后,進行時鐘分離及碼型變換及移位,移位完成后進行奇偶校驗,并把數據定寫入保持寄存器,此時rxrdy變為高電平,表示數據準備好可以讀出數據。進入下一個解碼周期,等待串行輸入數據。

該邏輯可由狀態機實現,可劃分為四個狀態進行:第一個狀態是空閑狀態,當檢測到數據跳變沿時,進入第二個狀態;第二個狀態為有效同步字頭檢測狀態;當檢測到有效同步字頭,啟動第三個狀態,用鎖相環分離時鐘,進行碼型轉換;當數據有效時進入第四個狀態,進行并/串轉換及奇偶校驗。其狀態機狀態轉換如圖4所示,以下是具體實現過程。

①同步字頭檢測。當檢測到數據跳變沿(下跳沿為命令字,上跳沿為數據字)時,用16MHz時鐘對數據進行采集;當采集到大于一個位時的低電平或高電平時,認為同步字頭有效,啟動第二狀態,進行處理。啟動位產生的時間要注意選擇,這對于消除數據中的毛刺和減少數據的延時都很重要。

②碼型轉換。檢測到有效同步字后,啟動鎖相環開始分離時鐘。此設計采用超前-滯后鎖相環,鎖相環如圖5所示。

圖5中邊沿檢測器的輸出e是在u2(t)的跳變沿時產生的窄脈沖,d是c的反相,c、d、e經過與門后在f和g形式滯后和超前脈沖。h和g分別用來控制和扣除門和添加門,通過扣除門和除脈沖和通過添加門添加脈沖,它們的和輸出經過分頻器2得到c,也即u2(t)就能跟隨u1(t)的相位了。

邊沿檢測器的工作原理是在u1(t)的上跳沿時放過一個16MHz的時鐘脈沖,這樣產生的邊沿檢測脈沖e只會在f和g中的一個產生脈沖,也就避免了超前一滯后型數字鎖相環存在的相位模糊問題。該鎖相環的相位鎖定時間最大為42ns,因此在與數據進行模二加之前,應將數據進行延時,以便消除毛剌。要想完全將毛剌消除還要配合同步字頭檢測時,啟動位產生時間的設置。這在后面毛剌處理中有詳細的介紹。

③奇偶校驗和串行并轉換。用移位寄存器可實現數據的串/并轉換。在設計移位寄存器時,要注意奇偶位的分離,因此在設計寄存器時需設置一定的標志位,其源代碼如下:

if reset=‘0’then

rsr《=(others=》‘0’);

--全為零可確保在移位過程中idle為低電平;

rxparity《=‘1’;

--確保在移位過程中idle=0,而在移位結束時,idle=1;

tag《=‘0’;

--移位標志位設置,當tag=1時,移位完成;

paritygen《=paritymode;

--為奇校驗時paritymode賦值為1,若為偶校驗則設置為0;

elsif rxclk‘event and rxclk=’1‘then

if idle=’1‘then

rsr《=(others=》’0‘);

rxparity《=’1‘;

tag《=’0‘;

paritygen《=paritymode;

elsif hunt=’1‘then

tag《=rsr(15);

rsr(15 downto 1)《=rsr(14 downto 0);

rsr(0)《=rxparity;

rxparity《=data1;

--進行移位,為右移寄存器;

paritypen《=parityegen xor rxparity;

--進行奇偶校驗;

end if;

end if;

至此曼徹斯特的解碼就完成了,其時序仿真波形如圖6所示。

畋6中data1.Q時,進行碼型轉換后的數據。由圖中可以看出采用此種方法進行轉換,數據沒有毛刺,產生的數據完全正確。

2.2 編碼

編碼的過程也可分為三部分:①檢測編碼周期是否開始,產生同步字頭;②進行串行轉換,產生奇偶校驗位;③對16位有效數據及奇偶位進行編碼,編碼周期結束。與解碼同理,編碼也由狀態機來實現。

由此狀態機可劃分為四個狀態進行實現,其狀態機狀態轉換如圖7所示。

編碼器的輸入時鐘(mclk)為16MHz。當寫信號(wr)為低電平時,同步頭選擇位(cmnd)為高是怦,開始產生命令字同步字頭;反之,為同步字頭。由于同步字頭的高低電平各占1.5個位時,所以選取它的發送時鐘為2MHz,該時鐘由mclk八分頻得到。同步字頭產生完成,則發出控制信號開始移位。移位時鐘(1MHz)由同步頭生成時用的時鐘兩分頻產生。在數據移位完成時自動添加廳偶位。曼碼形成器對數據、奇偶位、同步頭進行處理形成符合1553B標準的雙極性字tx和ntx,完成后txrdy為高電平,等待下一個數據的寫入開始再一次的編碼過程,邏輯框圖如圖8所示。

編碼其實是解碼的逆過程,其工作原理非常相似,這里就不詳細介紹了。編碼的時序仿真波形如圖9所示。

圖9中tx為經過編碼后的串行數據。采用此種方法進行編碼,產生的數據完全正確,并且也不存在毛剌。

3 設計中存在的問題及解決辦法

信號在FPGA器件內部通過連線和邏輯單元時,都有一定的延時。延時的大小與連線的長短和邏輯單元的數目有關。由于這兩方面的因素,多路信號的電平值發生變化時,在信號變化的瞬間,組合邏輯的輸出有先后順序。它們并不是同時變化,而且往往會出現一些不正確的類峰信號,這些類峰信號稱為“毛刺”。另外,FPGA器件與分立元件不同,其內部不存在寄生電容電感,這些毛刺將被完整的保留并向下一級傳遞,因此毛刺現象在PLD、FPGA設計中尤為突出。消除數據中的毛剌是設計中的一個重要問題。如果毛刺處理不好,就會影響系統性能甚至引起邏輯錯誤。

本設計中消除毛剌采用的方法有:①在有毛剌的輸出端加D觸發器;②計數器采用格雷碼計數器。采用D觸發器是因為D觸發器的D輸入端對毛剌不敏感,只要毛刺不存時鐘上跳沿時出現在D輸入端,就不會對輸出產生影響,這樣就可以消除毛刺了。采用格雷碼計數器代替普通的二進制計數器,是因為格雷碼計數器的輸出每次只有一位數據產生變化,這就消除了競爭冒險產生的條件,避免了毛刺的產生。例如在解碼器的設計中,進行碼型變換時,要將接收時鐘與接收的串行數據進行模2加。因為時鐘滯后于數據,為了消除毛刺要將數據進行延時再進行模2加;同時還要考慮到1553B對時間的要求(兩個數據之間的間隔最小只有1.5μs),因此在時鐘分離時就考慮提前進行他高。在檢測同步頭時,一旦其高(或低)電平大于1個位時的寬度就認為同步頭有效,開始進行時鐘分離,這樣就減小了數據延時,可有效節省時間。進行模2加后,加一D觸發器可確保完全將毛刺消除。在編碼器設計中在串行數據輸出端加一D觸發器,數據的毛刺 也被了。另外,在電路的設計中盡可能地消除毛刺產生的條件,例如分頻計數器采用格雷碼計數器。

4 仿真及FPGA實現

為了確保設計的可行性,必須對設計進行時序仿真;為了提高芯片的性能及資源利用率,要采用專門的綜合軟件對設計進行優化、綜合。由此采用Synplify7.1進行綜合,采用MAX+PLUS II進行時序仿真。在Synplify中使用有效的代碼,優化組合邏輯、減少邏輯延時等措施來提高整體性能,還進行了多個文件的分塊設計,然后將這些文件映射到頂層文件進行綜合,并運用VHDL對單個文件進行編寫、仿真和優化。在用到組合邏輯時,Synplify會盡量避免鎖存器的出現,節省邏輯單元。Synplify和其它綜合軟件一樣,編譯后生成的電子設計交換格式文件(EDIF)可以在MAX+PLUS II或Quartus II 3.0中進行編譯、仿真、分配引腳和其它優化處理。因此,采用MAX+PLUS II和Synplify 7.1相結合對FPGA進行設計、優化、綜合,可提高系統性能和芯片資源的利用率。

最后本設計在Altara公司ACEX1K系列的FPGA(EP1K100Q208-3)芯片上進行了實現。對于ACEX系列的芯片,它還支持寄存器配平技術、流水線操作、復制邏輯模塊、使用LPM函數等技術來提高其整性性能,并針對其特點對設計進行了最后的優化。該編解碼順共占用了218個邏輯單元,占總邏輯資源的4%,這有利于今后對其進行完善和功能的添加。其輸入時鐘為16MHz,數據速率為1MHz,編碼和解碼時序波形分別如圖6所示。

5 總結及設計通用性

該編碼解碼器采用自頂向下和自向上相結合的方法進行設計,用VHDL語言輸入,用MAX+PLUS II和Synplify分別進行仿真、綜合。在設計最后,針對器件進行了再一次的優化,縮短了設計周期,提高了系統性能,并且大大提高了芯片資源的利用率。

本設計具有一定的通用性,它的邏輯大部分只涉及到編、解碼器本身;而它與外部的接口十分簡單,只要對其讀、寫及同步字頭選擇信號進行有效控制,就能使其正常工作。它的設計是十分獨立的。另外,由于選擇器件資源比較豐富,故對其進行功能添加也十分方便,只需添加電路設計而不必對原有電路進行修改。

-

FPGA

+關注

關注

1630文章

21777瀏覽量

604686 -

vhdl

+關注

關注

30文章

817瀏覽量

128210 -

觸發器

+關注

關注

14文章

2000瀏覽量

61258

發布評論請先 登錄

相關推薦

采用復雜控制邏輯器件和VHDL語言實現曼徹斯特編解碼器的設計

基于CPLD的卷積碼編解碼器的設計

EDA卷積碼編解碼器實現技術

高速并行RS編解碼器

用CPLD控制曼徹斯特編解碼器

基于FPGA的曼徹斯特編解碼器設計

用FPGA器件與VHDL語言實現曼徹斯特碼編解碼器的設計

用FPGA器件與VHDL語言實現曼徹斯特碼編解碼器的設計

評論