IP(Intellectual Propcrty)就是常說的知識產權。美國Dataquest咨詢公司將半導體產業的IP定義為用于ASIC、ASSP和PLD等當中,并且是預先設計好的電路模塊。IP核模塊有行為(Behavior)、結構(Structure)和物理(Physical)_三級不同程度的設計。根據描述功能行為的不同,IP核分為三類。即軟核(Soft IP Corc)、完成結構描述的固核(Firm IP Core)和基于物理描述并經過工藝驗證的硬核(Hard IP Core)。IP軟核通常是用HDL文奉形式提交給用戶,它經過RTL級設計優化和功能驗證,但其中不含有任何具體的物理信息。據此,用戶可以綜合出正確的門電路級設計網表,并可以進行后續的結構設計,具有很大的靈活性;借助于EDA綜合工具可以很容易地與其他外部邏輯電路合成一體,根據各種不同半導體工藝,設計成具有不同性能的器件。本文利用先進的EDA軟件,用VHDL硬件描述語言采用自頂向下的模塊化設計方法,完成了具有相序自適應功能的雙脈沖數字移相觸發器的IP軟核設計。

1 三相全控橋整流電路

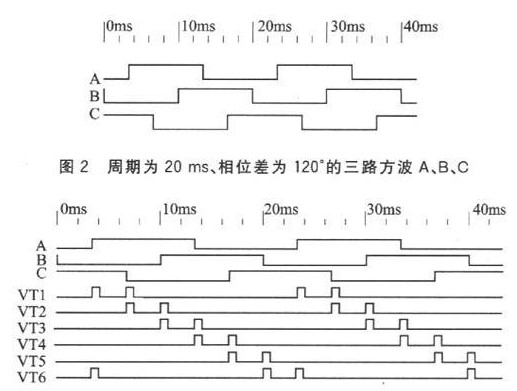

如圖1所示,三相全控橋整流電路由6只晶閘管組成。共陰極組側和共陽級組側的各3只晶閘管相互換流,在電源的一個周期內獲得6次換流的脈動波形。三相全控橋整流電路在任何時刻必須保證有兩個不同組別的晶閘管同時導通才能構成回路。換流只在本組內進行,每隔120°換流一次。由于共陰級組與共陽級組的換流點相隔60°,所以每隔60°有一個元件換流。同組內各晶閘管的觸發脈沖相位差為120°,接在同一相的兩個元件的觸發脈沖相位差為180°,而相鄰兩脈沖的相位差是60°。

2 IP軟核設計

2.1 觸發脈沖輸出設計思路

本設計的觸發脈沖移相是以三相的自然換相點為基準的,三相電源U、V、W輸入經過兩兩相減并整流以后得到周期為20 ms、相位差為120°的三路方波A、B、C(如圖2所示),作為頂層模塊的同步輸入。分析觸發脈沖可以發現,不管移相觸發角為多少,以A相的過零點作為同步點,則從同步點開始的一個周期360°內,必然產生6次輸出脈沖。本設計采用雙窄脈沖,每次有兩路輸出。6個晶閘管的觸發分別由A、B、C的正、負電平周期內進行延時。例如:A的正電平周期內,以A的上升沿為起始點,經過由移相角決定的延時后,發出VTl的觸發脈沖;在雙窄脈沖應用中,同時發出VT6的觸發脈沖。觸發脈沖時序圖如圖3昕示。

可以實現從自然換相點開始0°~180°的延時,設計思路簡單直觀,而通常設計則須區分不同的移相范圍。在外部輸入6MHz的時鐘時,可以實現精度為O.003°的移相,同時還可實現相序自適應。

2.2 IP軟核設計思路

采用層次化的設汁思想,將模塊分為頂層模塊和子模塊,各模塊均使用VHDL語言進行設計。頂層模塊(Trigger)決定整個設計的輸入/輸出接口和各個子模塊的連接關系。設計思路為:移相角的輸入由并行的16位數據線輸入,并保存在移相角寄存器中;A、B、C三相輸入作為移相觸發輸出的基準,根據移相角寄存器中的延時值對相應晶閘管的觸發脈沖進行延時;觸發脈沖由VTl~VT6輸出,CLK是時鐘輸入,SOUT是周期為3.3ms的同步輸出。共有4個子模塊s_pulse、ph_adp、delayer和word。

s_pulse模塊將A、B、C_三相輸入通過D觸發器實現時鐘同步,由TAF_EN信號輸入作為移相角的更新使能。當TAF_EN為1時,用并行的l6位數據口D0~D15的數據更新移相角寄存器中的數值。

ph_adp模塊根據A、B、C三相輸入完成相序的判斷。相序的判斷基于以下算法;當A相(U-V)的上升沿到來時,如果A、B、C三相輸入的電平為101,則為正相序(U、V、W)輸入;如果A、B、C三相輸入的電平為110,則為負相序(U、W、V)輸入。模塊輸出信號ps、ns分別作為正、負相序的標志。

delayer模塊產生寬度為O.8 ms的觸發脈沖。觸發脈沖的產生分別以三相輸入的上升、下降沿為基準,根據移相角寄存器中的值,由CLK觸發的計數器完成6個觸發脈沖的延時。例如:以同步輸入A相的上升沿為基準,由CLK觸發計數器開始計數,當計數值達到移相角寄存器中的值后,送出一個寬度為0.8 ms的觸發脈沖VTl;三相輸入的上升、下降沿分別采用各自的計數器。

word模塊完成觸發脈沖的調制。調制頻率為10 kHz,使得每個觸發脈沖內有8個子脈沖,通過脈沖變壓器對6個晶閘管的門極控制,并根據相序標志ps、ns以正確的順序送出觸發脈沖。

正相序時的觸發脈沖順序為:VTl→VT2→VT3→VT4→VT5→VT6→VTl。

負相序時的觸發脈沖順序為:VT6→V15→VT4→VT3→VT2→VT1→VT6。

2.3 IP軟核設計實現

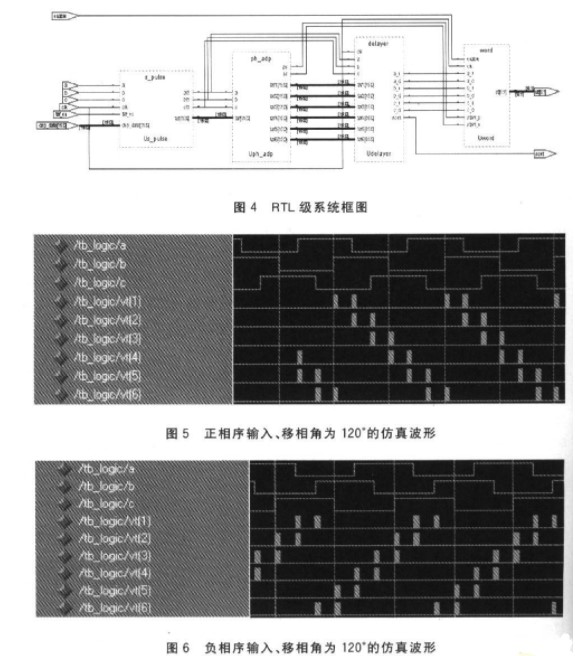

本設計中,IP軟核由VHDL語言編寫實現,使用synplicity公司的Synplify Pro完成編譯和綜合。綜合以后的RTL級系統框圖如圖4所示。

可以根據具體系統所用的不同器件進行綜合,再使用不同器件廠商的布局布線工具產生編程文件,然后下載到具體器什中,就完成了該IP軟核的應用實現。

3 IP軟核的仿真及驗證

為了驗證該IP軟核的邏輯功能,需要對其進行功能仿真。編寫testbench,在仿真軟件Modelsim中對頂層模塊進行功能模塊。使用testbench可以對所設計的功能模塊進行靈活的仿真,以檢驗IP軟核在正、負相序輸入以及各種移相角時的輸出是否正確。圖5和圖6分別為正、負相序輸入時移相角為120°的仿真波形。

由仿真結果可以看出,該IP核的邏輯功能正確。用QuARTUSII進行編譯后,下載到Altera公司的新一代CPLDMAXII系列的EPMl270中,能夠實現精確的移相以及相序自適應。

4 結論

按照IP軟核的設計流程,完成了全數字二二相晶閘管移相觸發器的設計。該方法解決了不同移相范圍觸發脈沖輸出的問題,并實現了相序自適應,為三相晶閘管移相觸發電路的應用提供了有效的可復用設計手段,使得整個控制系統的設計得以簡化。該IP軟核的設計已成功應用于基于TMS320LF2407A的直流電機調速系統中。

-

半導體

+關注

關注

334文章

27598瀏覽量

220816 -

eda

+關注

關注

71文章

2776瀏覽量

173528 -

觸發器

+關注

關注

14文章

2002瀏覽量

61267

發布評論請先 登錄

相關推薦

8PSK全數字解調技術的實現

VHDL語言實現數字電壓表

如何實現基于VHDL語言的全數字鎖相環?

全數字多媒體語言實驗室的應用與管理

采用EDA軟件與VHDL語言實現全數字數字移相觸發器IP軟核的設計

采用EDA軟件與VHDL語言實現全數字數字移相觸發器IP軟核的設計

評論