引言

隨著遙測系統的不斷發展,系統復雜程度也隨之提高,因此在終端設計中,對信號源的頻率穩定度、幅值范圍和頻率范圍提出了越來越高的要求。這就要求遙測系統具備高碼速、實時可重構、處理復雜結構的能力,傳統的數字電路難以實現這些復雜功能。FPGA(現場可編程門陣列)是近幾年發展起來的硬件可編程芯片,具有硬件密度高、結構靈活、可編程、加密性強等良好性能,在高速信號處理領域占有至關重要的地位,也為多路模擬量信號源的實現,提供了有效的途徑。本文針對遙測應用,以大容量FPGA器件為核心,實現了電源獨立的不同頻率、不同波形的多路模擬量信號源。

1 系統硬件設計

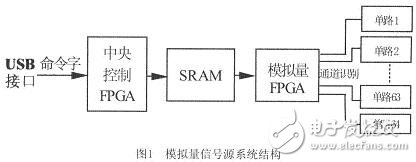

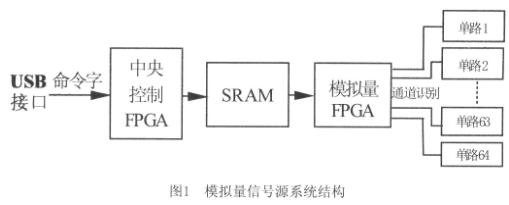

目前,大容量的FPGA主要有Altera、Xilinx、Lattice、Actel、Cypress等公司的產品。比較而言,Altera CycloneII系列FPGA芯片速度快、容量大、內嵌RAM多、并且有DSP硬件乘法器,是低成本、低功耗應用的最佳選擇。因此在本文中選用Altera公司的Cyclone II系列FPGA-EP2C8芯片,EP2C8芯片是1.25 V內核供電,具有8.256個邏輯單元(LE),36個M4K RAM塊,RAM總量為165,888,18個嵌入式乘法器以及208個管腳,其中包括182個最大可用I/O引腳。Altera公司有相應的開發軟件平臺Quartus II,此軟件功能強大,使用簡單,支持的器件種類眾多,可支持在線仿真,在線下載等,并具有豐富的IP核及邏輯功能模塊資源,便于使用VHDL+模塊/原理圖輸入界面等等。模擬量信號源主要包括中央控制FPGA單元、模擬量FPGA、靜態存儲SRAM、單路模擬量單元,如圖l所示,

整個系統使用USB 2.0接口與計算機進行通訊,信號由計算機軟件生成波形數據,通過USB口下載到主控FPGA,經過16位SRAM鎖存,將各路信號傳至模擬量FPGA,經由解碼分路選通,輸出電源獨立的不同頻率、不同波形的多路模擬量信號。其中包括4路單極性幅值O~30V,60路雙極性幅值±15V;四種波形分別為鋸齒波、正弦波和方波(占空比1:1),信號頻率為0~50Hz,以及固定電平,幅值可以初始設定,并可實現實時可調。

2 單路模擬量組成模塊設計

2.1 系統構成

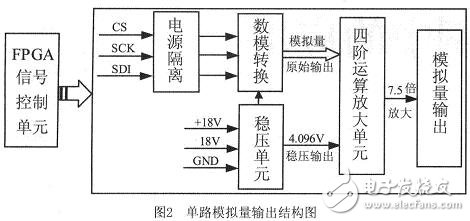

單路模擬量由電源隔離單元、前端穩壓單元、數模轉換(DAC)單元和運算放大單元等構成,具體構成如圖2所示,系統由雙18 V供電經過穩壓單元輸出4.096 V,給DAC和運放芯片提供工作電壓,另外通過指令啟動信號在SPI總線上發送FPGA的CS、SCK、SDI信號,傳至單路模擬量,將相應數字量進行D/A轉換,得到的模擬量數據經由運算放大輸出,即可實現64路模擬量波形。系統時鐘同步輸出,具有很高的可靠性。

2.2 組成模塊設計

2.2.1 電源隔離單元

64路模擬量信號要求對每路信號進行獨立電源隔離,本文采用的ADUM1300是基于ADI公司磁耦隔離技術的通用型三通道數字隔離器,經過自制高壓隔離信號調理電路,可以輸出系統任務要求的相互隔離的、獨立基準模擬量信號,實現SPI接口和數字轉換器的隔離。它采用了高速CMOS工藝和芯片級的變壓器技術,在性能、功耗、體積等各方面都有光電隔離器件無法比擬的優勢。ADUM130數字隔離器在一個器件中提供三個獨立的隔離通道,兩端工作電壓為2.7V~5.5V,支持低電壓工作,并能實現電平轉換。另外,ADUM130具有很低的脈寬失真(《3ns),功耗僅為0.8mA,工作電壓為3V/5V,傳輸速率為1M/25M/90Mb/s,ADuM130還具有直流校正功能,有一個刷新電路保證即使不存在輸入跳變的情況下,輸出狀態也能與輸入狀態相匹配,這對于上電狀態和具有低數據速率的輸入波形或恒定的直流輸入情況是很重要的。

2.2.2 前端穩壓單元

REF198精密電壓基準,初始精度0.05%,溫漂5ppm/℃,輸出電流30mA,最大電源電流45 μ A,電源電壓范圍6.4V~15V,輸出電壓4.096V,每路輸出電壓與理論設置值的誤差在30mV以內;每路驅動能力不低于5mA;該芯片同時為數模轉換(DAC)模塊和運放模塊提供工作電壓。

2.2.3 DAC單元

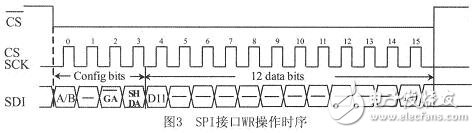

MCP4821是12位DAC芯片,本文中是單電源供電,32.768 MHz時鐘支持的SPI接口,溫漂50ppm/℃,電源電壓范圍2.7V~5.5V,內部參考電壓為2.048V,FPGA向MCP4821寫入16位數據,如圖3所示,高四位是芯片配置位(Config bits),其它12位是數據位(data bits),在CS信號上升沿有效時,經過16個時鐘脈沖完成轉換。

2.2.4 運算放大單元

AD824運算放大器是美國AD公司生產的單電源、低功耗、精密場效應輸入的運算放大器。采用雙電源工作時,它的輸出電壓能夠達到電源的正負電源電壓。AD824的芯片內含有四個性能匹配的運算放大器。在本設計的雙電源工作時,額定工作電壓由±1.5v到±18v。它們的輸出電壓擺幅僅比電源電壓小10mV。輸入信號有可能出現大于+VS時,運算放大器的同相輸入端串聯一個電阻,典型值為1k Ω,就能防止輸入信號的相位反相,但將產生附加的輸入電壓噪聲。

3 電磁干擾設計

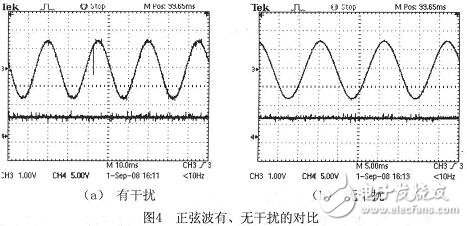

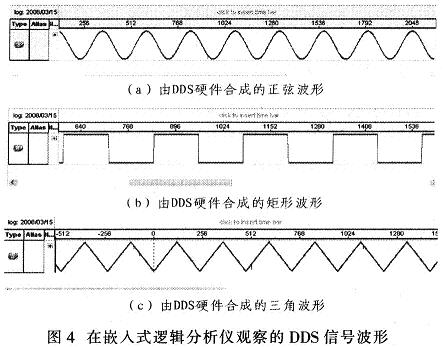

在整個電路系統中,電磁干擾主要出現在輸入與輸出接口處,其內部結構一般不會出現電磁干擾。本系統對輸入輸出信號進行接口保護,防止電磁干擾的產生;并采用線性電源及電源濾波模塊,關鍵模塊均進行電磁屏蔽,以最大程度降低模塊問的互擾。如圖4所示,左側為有電磁干擾的正弦波,可以很明顯地看出,在正弦波波峰位置突然出現一個下拉電平,經過多次分析,此現象為輸入電源受到嚴重干擾而引起,右側為經過II濾波模塊后的波形。

4 結束語

本文應用FPGA實現了模擬/數字信號采集系統設計,異步串行數據傳輸等,并且通過多路切換開關循環采集,實現了對高速信號的采集和精確的電路設計,系統性能穩定,數據采集精度較高,抗干擾能力較強,具有很高的使用價值和良好的應用前景。經過多次長時間上電測試,能產生頻率、幅值可調的波形信號,每路波形輸出電壓基準隔離,調節精度高達1%,遠高于普通的信號源,完全滿足系統設計的要求,已成功應用于某遙測信號源。

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603427 -

芯片

+關注

關注

455文章

50817瀏覽量

423678 -

轉換器

+關注

關注

27文章

8703瀏覽量

147184

發布評論請先 登錄

相關推薦

基于FPGA和DDS的信號源設計

基于FPGA的多路模擬量、數字量采集與處理系統

智能多路信號源的設計與實現

基于FPGA的多路模擬量、數字量采集與處理系統

基于CycloneII系列FPGA的DDFS信號源實現

基于FPGA的可調信號源設計

采用可編輯邏輯器件EP2C8芯片實現多路模擬量信號源的設計方案

通過采用FPGA器件實現遙測系統的多路模擬量信號源的設計

通過采用FPGA器件實現遙測系統的多路模擬量信號源的設計

評論