引言

Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS, Altera的Stratix、Stratix GX、Stratix II和Cyclone系列FPGA全面支持Nios II處理器。Nios II系列包括3種產品:Nios II/f(快速)--最高的系統性能,中等FPGA使用量;Nios II/s(標準)--高性能,低FPGA使用量;Nios II/e(經濟)--低性能,最低的FPGA使用量。這3種產品具有32位處理器的基本結構單元--32位指令大小,32位數據和地址路徑,32位通用寄存器和32個外部中斷源;使用同樣的指令集架構(ISA),100%二進制代碼兼容,設計者可以根據系統需求的變化更改CPU,選擇滿足性能和成本的最佳方案,而不會影響已有的軟件投入。另外,Nios II系列支持60多個外設選項,開發者能夠選擇合適的外設,獲得最合適的處理器、外設和接口組合,而不必支付根本不使用的硅片功能。本文采用CycloneTM器件中的EP1C6Q240C8來實現雷達仿真電路顯示模塊的設計。

1 硬件設計

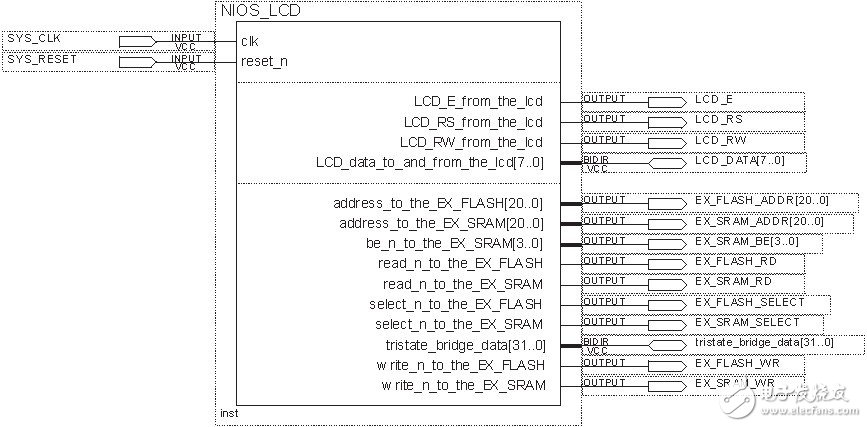

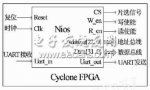

本系統的硬件結構如圖1所示,主要包括以下部分:

圖1 系統硬件結構

1.1 EP1C6Q240C8及其配置芯片

本文系統中的處理器選用的是采用Altera公司提供的Cyclone系列的EP1C6Q240C8,該芯片采用240腳的PQFP封裝,提供185個IO接口。

該芯片擁有5980個LEs;可提供92160bit的ram;芯片內部還自帶有2個鎖相環,可以在高速運行的時候保證系統時鐘信號的穩定性。

在Nios II的硬件電路,通常使用Altera串行配置器件來存儲FPGA配置文件*.Sof。

Altera串行配置器件可提供在系統編程(ISP)和多次編程能力,能夠使FPGA和配置器件能夠以最低的價格實現完整的可編程芯片系統(SOPC)解決方案。標準型配置器件, 包括EPC2、EPC1、EPC1441、EPC1213、EPC1064和EPC1064V.本文使用EPC2配置器件。使用時,首先使用下載電纜將計算機生成的FPGA配置文件*.Sof使用programmer燒入EPC2配置器件中,然后由EPC2配置器件控制配置時序對FPGA進行配置,一次燒寫即可重復使用,編程完后可以脫離計算機工作。

1.2 存儲模塊

存儲模塊包括兩部分:只讀存儲器和隨機存儲器。

只讀存儲器用來存儲用戶程序和需要下載的文件。由于利用EP1C6Q240C8處理器的LCD滾屏設計是較為復雜的SOPC系統,用戶程序和需要下載的文件較大,用EPCS來存儲是不現實的。根據設計的具體要求選擇存儲容量為4Mbit的FLASH作為只讀存儲器, 并可使用flashprogrammer將*.elf和需要下載的文件燒入FLASH中,并在系統加電后實現調用。

隨機存儲器(RAM)主要是為了存放可執行代碼和程序中用到的變量。由于所采用的處理器中的ram的存儲容量較小,根據本文中設計電路的要求,采用8M的外部sram.

1.3 顯示模塊

LCD顯示模塊是由控制器、行驅動器、列驅動器和液晶顯示屏等器件構成的。其核心部件LCD控制器是SOPC,它一方面提供與微控制器(即NIOS處理器)的接口,一方面連接行/列驅動器。通過對SOPC編程來實現對lcd的操作控制。本文采用的接口可編程芯片是T6963C來控制單色點陣圖形LCD。

T6963C是一種內置控制器的圖形液晶顯示模塊,其面向顯示存儲器的引腳有8根數據線(D7~D0)、16根地址線(AD15~AD0)和4根控制線,最多能管理64kB大小的顯示存儲器。T6963C單屏可以達到640×128像素,雙屏可以達到640×256像素。

2 軟件開發

基于NIOS II處理器的雷達仿真電路顯示模塊的軟件設計主要是使用NIOS通過對LCD的控制器進行編程以達到對LCD進行顯示控制來實現的,其軟件實現方案主要包括以下幾部分:

2.1 T6963C初始化

顯示模塊軟件開發首先要對控制LCD的T6963C的寄存器進行初始化,設置LCD的特性。其初始化包括:

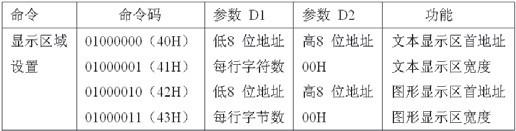

(1)設置文本和圖形緩沖區的起始地址和寬度、屏幕每行的字節數。其軟件設計主要依據表1指令來實現:

表1 T6963C控制指令

部分軟件代碼如下所示:

IOWR_ALTERA_AVALON_PIO_DIRECTION(LCD_DB_BASE,0xff);

IOWR _ ALTERA _ AVALON _ PIO _ DATA(LCD_CS_BASE,0);

IOWR _ ALTERA _ AVALON _ PIO _ DATA( LCD _ WR _ BASE , 0 );

IOWR _ ALTERA _AVALON_PIO_DATA(LCD_CD_BASE,0);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_DB_BASE,參數數據1);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_DB_BASE,參數數據2);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_CD_BASE,1);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_DB_BASE,指令);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_CS_BASE,1);//

IOWR_ALTERA_AVALON_PIO_DATA(LCD_WR_BASE,1);//

(2)設置系統的字符和圖形之間按"或"功能顯示,其軟件設計主要依據指令80H來實現,部分軟件代碼如下所示。

IOWR_ALTERA_AVALON_PIO_DIRECTION(LCD_DB_BASE,0xff);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_CS_BASE,0);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_WR_BASE,0);IOWR_ALTERA_AVALON_PIO_DATA(LCD_CD_BASE,1);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_DB_BASE,80H);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_CS_BASE,1);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_WR_BASE,1);

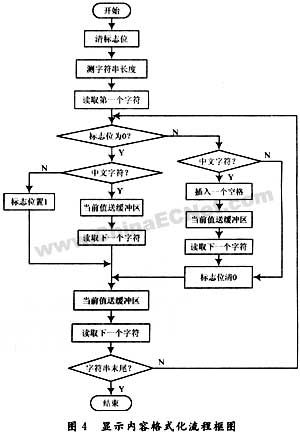

2.2 LCD滾屏設計

定時間、定間隔地修改文本顯示區與圖形顯示區首地址將會產生顯示畫面滾動顯示效果。軟件實現如下:

Delay(自行設定延時時間);

alt_u32Text_stadd;

alt_u8Text_stadd_newL,Text_stadd_newH;//調整后的文本顯示區低8位地址和高8位地址

Text_stadd_new=文本區地址高8位×256+文本區地址低8位+0x14//0x14表示每行可顯示30個字符

Text_stadd_newL=Text_stadd_new/256;

Text_stadd_newH=Text_stadd_new%256;

IOWR_ALTERA_AVALON_PIO_DATA(LCD_DB_BASE,Text_stadd_newL);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_DB_BASE,Text_stadd_newH);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_CD_BASE,1);

IOWR_ALTERA_AVALON_PIO_DATA(LCD_DB_BASE,40H)。

圖形顯示區首地址的調整方法同文本區的調整方法相同。

3 結論

本文闡述基于NIOSⅡ嵌入式處理器控制LCD的硬件設計方案和軟件設計方法,充分體現了NIOSⅡ嵌入式處理器在LCD設計中的靈活性。

-

處理器

+關注

關注

68文章

19286瀏覽量

229852 -

嵌入式

+關注

關注

5082文章

19126瀏覽量

305242 -

液晶顯示屏

+關注

關注

1文章

208瀏覽量

27473

發布評論請先 登錄

相關推薦

NIOSⅡ嵌入式處理器的特點及實現控制液晶顯示器

基于STM32的12個設計方案(電機控制,LED,觸摸屏,多路電...

淺析嵌入式的LCD液晶顯示屏

嵌入式數字頻率合成器的液晶顯示設計

基于ARM7微處理器的中文液晶顯示技術

Nios實現液晶顯示屏控制

適用于LCD液晶顯示的控制器設計方案

采用NIOSⅡ嵌入式處理器的液晶顯示屏滾屏設計方案

采用NIOSⅡ嵌入式處理器的液晶顯示屏滾屏設計方案

評論