在用高于常見的電源電壓(如24V)設計邏輯電路時,可以結合使用標準邏輯系列與一只穩壓器,通過電平轉換器做接口。另外,如果邏輯并不太復雜,速度也不是非常高,可以用分立元件建立門控電路,直接用當前電壓運行。分立元件的AND、OR和NOT功能都相對簡單明確,但XOR和XNOR功能通常需要多個AND、OR和NOT基礎功能的組合。

本例給出了一種不常見方法,用兩只電阻、四只二極管和一只晶體管,就能完成異或功能。NPN結構獲得的是XNOR運算,而PNP結構則得到XOR運算。

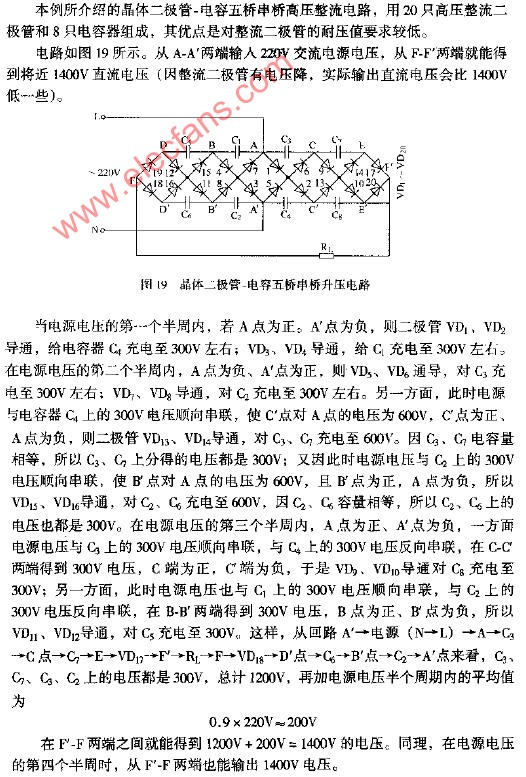

考慮圖1a中的XNOR電路。當A或B兩個門的輸入為相反邏輯態時,基射結上有一個高電壓壓降減低電壓再減1.2V,得到的電壓做正偏。晶體管導通,集電極的邏輯零電壓大約為0.6+VL+VCE,其中VL為低電壓,VCE是集射電壓。當輸入A和B為相同邏輯態時,晶體管基射結不能正偏,因此輸出Y為電源電壓。

圖1,XNOR(a)和XOR運算(b)的分立實現能夠使標準邏輯系列在較高電源電壓下運行。

集電極上6.8kΩ的選擇要看驅動A和B輸入端的是標準TTL邏輯還是CMOS邏輯,可根據應用來選擇。CMOS4000系列能夠在5V電源下可靠地供出或吸入1mA。低速TTL可以供出0.4mA,吸入8mA。對于基極電流,一個0.4mA的邏輯1驅動電流就足夠了,但是A或B端的邏輯0形成了射極電流,CMOS的1mA吸入電流極限就成問題了。在有1mA凈電流,輸出負載維持在大約250μA時,必須選擇一只6.8kΩ電阻(0.75mA×6.8kΩ)才能獲得大約5V壓降。

然后,考慮XOR結構,此時無論A或B的邏輯0都是相對基極,而邏輯1是相對射極。Y上的邏輯1電壓為VH-0.6V-VCE,而邏輯0約為0V,但通過集電極電阻限制了電流。

這里的問題是,TTL邏輯1的輸出電流大約為0.4mA,這是晶體管的射極電流。集電極電阻選10kΩ時,其電壓降可以達到近4V。這個電平足以驅動CMOS負載,但對TTL則不然,當Y為邏輯0時,其邏輯0的輸入至少需要0.4mA的電流。10kΩ無法提供這一電流。但是,采用前面的X NOR 結構,并在Y后另加反相晶體管,就得到了XOR功能(圖1b)。XOR似乎只適用于A 和B端的CMOS/TTL輸入,只能在輸出Y 驅動CMOS。

-

二極管

+關注

關注

147文章

9675瀏覽量

166986 -

驅動

+關注

關注

12文章

1844瀏覽量

85405 -

晶體管

+關注

關注

77文章

9711瀏覽量

138586

發布評論請先 登錄

相關推薦

隧道二極管與晶體管的組合使用

通過二極管橋和晶體管完成異或功能

通過二極管橋和晶體管完成異或功能

評論